# TiO<sub>2</sub>/TiO<sub>2-x</sub> 기반 멤리스터의 전기적 특성 활성화에 공정 변수가 미치는 영향 분석

이범구1, 이재윤1, 최정훈1, 서정무1, 김성진1,20

<sup>1</sup> 충북대학교 컴퓨터공학과

Analysis of Operation Parameter Impact on Electrical Characteristics Activation in TiO<sub>2</sub>/TiO<sub>2-x</sub> Based Memristors

Beom Gu Lee<sup>1</sup>, Jae-Yun Lee<sup>1</sup>, Jung Hun Choi<sup>1</sup>, Jung Moo Seo<sup>1</sup>, and Sung-Jin Kim<sup>1,2</sup>

<sup>1</sup> College of Electrical and Computer Engineering, Chungbuk National University, Cheongju 28644, Korea

<sup>2</sup> Biomedical Research Institute, Chungbuk National University Hospital, Cheongju 28644, Korea

(Received July 18, 2024; Revised August 19, 2024; Accepted August 26, 2024)

**Abstract:** Memristors, as next-generation memory devices, have garnered significant academic interest. Among them, TiO<sub>2</sub>/TiO<sub>2-x</sub> based memristors have particularly attracted substantial scholarly attention. Research on the activation and stability of TiO<sub>2</sub> based memristor devices through process parameters is essential. Here, to determine the impact of process parameters on the activation of TiO<sub>2</sub>/TiO<sub>2-x</sub> based memristor devices, we fabricated the memristor devices using a sputtering system and conducted annealing at 400 °C. Additionally, to analyze the electrical characteristics of the devices, we measured the I-V curves and C-V curves. Also, we examined TiO<sub>2</sub>/TiO<sub>2-x</sub> based memristor devices surface using SEM. Consequently, it was observed that the devices subjected to annealing exhibited improved hysteresis curves in the I-V characteristics, a reduced bandgap, and changes in resistance compared to the non-annealed devices. The retention test results further demonstrated that the set/reset characteristics of the devices were stable, confirming their potential applicability as memory devices.

Keywords: Memristor, Annealing, Operation parameters, TiO2-x, Activation

#### 1. 서 론

기존의 메모리가 가진 한계를 극복하기 위해 차세대 메모리는 데이터 처리 과정에서의 빠른 처리 속도와 비휘발성, 소모되는 소모 전력의 감소, 안정성 등 요소들이 함께 발휘되어야 한다 [1-5]. AI 기술의 고도화로 인한 기존의

☑ Sung-Jin Kim; cugatech@gmail.com

Copyright ©2024 KIEEME. All rights reserved.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

메모리 반도체의 성능 한계를 극복하기 위하여 ReRAM, FeRAM 등의 차세대 메모리 기술이 연구되는 실정이다. 이러한 차세대 메모리 소자들 중 ReRAM은 절연막의 저항값 변화를 이용하여 데이터를 저장할 수 있는 소자로 기존의 휘발성 메모리에 비해 수십, 수백 배의 처리 속도를 가지다 [6-10].

일반적으로 불리는 멤리스터(memristor)는 memory 와 resistor의 합성어로 저항의 특성을 띠는 소자가 전극 양단에 인가되는 특정 펄스 전압에 따라 가변저항을 가지 며 일정 시간 데이터를 저장하는 메모리 역할을 한다. 멤리

<sup>&</sup>lt;sup>2</sup> 충북대학교 의생명연구원

스터는 하나의 소자로 하나의 바이오 시냅스 구조를 모방할 수 있기 때문에 회로의 크기를 다중 트랜지스터로 구성된 시냅스 소자보다 획기적으로 줄일 수 있다. 이러한 특성은 반도체 트랜드인 회로 소형화를 통한 집적도 향상에 높은 도움을 줄 가능성이 기대되는 상황이다. 멤리스터는 일반적으로 금속과 산화물을 통한 metal-insulator-metal (MIM)의 구조를 가지므로 이러한 구조는 공정상의 결함을 줄일 수 있다는 장점이 존재한다 [11-14]. 멤리스터를 구성하는 물질 중 산화물은 TiO<sub>2</sub>, SiO<sub>2</sub>, NiO, HFO<sub>2</sub>, ZrO<sub>2</sub>, ZnO 등의 금속 산화물을 기반으로 제작된다 [15-17]. 이중 TiO<sub>2</sub> 박막 기반의 멤리스터는 가장 활발히 보고되고 있으며, 소자의 안정성과 활성화에 끼치는 영향을 분석하는 연구가 필수적으로 요구되는 실정이다 [14,18].

따라서 본 연구에서는  $TiO_2/TiO_{2-x}$  박막 기반 멤리스터 소자에 열처리 공정 변수가 미치는 영향을 분석하였다. 제 작한 디바이스의 전기적, 표면적 성능 변화에 대한 분석을 위해 I-V curves와 SEM 표면 image를 측정하였으며 또한, retention stability test와  $TiO_{2-x}$  박막의 밴드갭 변화를 분석하여 향후 비휘발성 메모리로의 응용 가능성을 판단하였다.

#### 2. 실험 방법

### 2.1 TiO<sub>2</sub>/TiO<sub>2-x</sub> 박막 기반 멤리스터 소자 제작

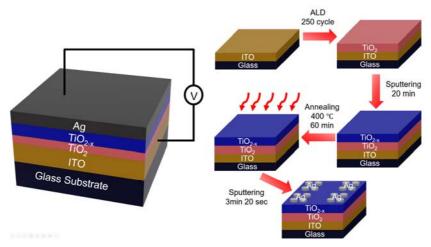

그림 1은 MIM 구조로 설계된  $TiO_2/TiO_{2-x}$  박막 기반 멤리스터의 구조와 멤리스터 디바이스 제작 과정을 나타낸

다. ITO glass를 기판이자 하부 전극으로 사용하였다. 이후 표면 위에 남아 있는 절연층 증착 시에 발생할 수 있는 불순물을 제거하기 위해 15분 동안 acetone을 사용하여 무기물과 유기물을 제거하였고, isopropyl alcohol과 deionized water을 이용하여 잔류 acetone을 제거하는 과정을 거치는 piranha cleaning 과정을 진행하였다. Cleaning 과정은 ultra-sonicating을 병행하며 진행하였다. Cleaning 과정 이후 소자에 남아 있는 isopropyl alcohol을 제거하기 위해 deionized water에 처리 과정을 진행한 후 N<sub>2</sub> gas blowing을 통해 기판에 남아 있는 수분을 제거하였으며 남아 있을지 모르는 deionized water을 제거하기 위해 60°C로 설정된 drying oven에 15분 동안 건조하였다.

세척을 통해 불순물이 제거된 기판 위에 5 nm 두께의  $TiO_2$  절연막을 형성하기 위해 atomic layer deposition (ALD) system을 이용하여 증착 공정을 수행하였다. 증착 과정에서의 신뢰성과 균일성을 위해 chamber 내의 온도 와 압력은 각각  $200^{\circ}$ C,  $2.5 \times 10^{-2}$  Torr로 유지하였다.

이후  $TiO_2$  절연막 위에  $TiO_{2-x}$  산화물 박막 활성층을 증착하기 위하여 RF magnetron sputtering system을 이용하였다. Sputtering 과정에서  $TiO_{2-x}$  target 쪽은 음극으로 하고 유리기판 위의 ITO 쪽을 양극으로, target과 유리기판 사이는 8 cm로 설정하여  $TiO_{2-x}$  절연막을 증착하였다. 제작공정의 신뢰성을 위하여 chamber 내의 초기 진공도를 chamber 내의 진공도는  $5\times10^{-5}$  Torr 이하로 설정하였다. 이후 안정적인 플라즈마 형성을 위해 공정 압력을 15 mTorr로 낮추었으며 Ar gas를 30 sccm으로 주입하여 증착을 진행하였다. 균일한 박막 형성을 위해 기판을

Fig. 1. Schematic illustration of TiO<sub>2</sub>/TiO<sub>2-x</sub> memristor based on oxide semiconductor active layers with annealing and TiO<sub>2</sub>/TiO<sub>2-x</sub> memristor manufacturing process.

| Table                                 | 1. | Electrical | properties | according | to | simultaneous | low- |  |  |

|---------------------------------------|----|------------|------------|-----------|----|--------------|------|--|--|

| temperature plasma annealing process. |    |            |            |           |    |              |      |  |  |

| Operation parameter | ITO    | TiO <sub>2</sub> | TiO <sub>2-x</sub> | Ag     |

|---------------------|--------|------------------|--------------------|--------|

| Non-annealing       | 100 nm | 5 nm             | 10 nm              | 100 nm |

| 400°C 60 min        | 100 nm | 5 nm             | 10 nm              | 100 nm |

8 rpm의 속도로 회전시켰으며, RF power를 120 W로 고 정하여 20분 동안 10 nm 두께의 TiO<sub>2-x</sub> 박막층을 증착하 였다.

어닐링이 소자의 전기적 특성 변화에 미치는 영향을 분 석하기 위하여 일부 소자에 열처리 box furnace에서 400℃의 온도로 60분간 어닐링하였다. 이후 상부 전극은 Ag target과 shadow mask를 이용하여 진공 상태에서 RF magnetron sputtering 하였다. 전극은 TiO<sub>2-x</sub> 증착 공정과 같은 조건에서 증착하였다. 증착된 Ag 전극은 island 형태를 띠고 있다. TiO<sub>2</sub>/TiO<sub>2-x</sub> 박막 기반 멤리스 터의 제작 공정 변수에 관련한 내용을 표 1에 정리하였다. 제작한 TiO<sub>2</sub>/TiO<sub>2-x</sub> 기반 박막 멤리스터의 전기적 성능에 대한 평가를 위해 암실의 환경에서 KEITHLEY사의 SYSTEM 2636A source meter를 활용하여 상부 전극에 -2~2 V의 전압이 인가해 I-V curve를 측정하였다. 또한, 제작된 멤리스터 소자의 메모리로의 응용 여부를 판단하 기 위해 retention test를 측정하였으며, 소자의 밴드갭 변 화를 확인하기 위해 제작된 소자의 투과율을 측정하였다.

## 2.2 TiO<sub>2</sub>/TiO<sub>2-x</sub> 박막 기반 멤리스터 소자 모델링

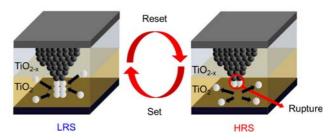

그림 2는 제작된 TiO<sub>2</sub>/TiO<sub>2-x</sub> 박막 기반 멤리스터의 동 작 과정을 간략하게 보여준다. 기존의 저항, 커패시터, 인 덕터를 활용하여 만들어진 RLC는 자속과 전하의 관계를 정의할 수 없으나, 저항 스위칭 메모리인 멤리스터는  $f_M$  $(\Phi, q)$ =0와 같은 구성 관계 특징을 가지는데, q는 전하 (charge)를, Φ는 멤리스터의 자속(magnetic flux)을 의 미하며, 이는  $\Phi = f_M(q)$ 으로 정의 가능하다. 또한  $f_M$ 은 특정 구간에서 미분 가능한 함수이다 [19]. 이를 시간에 따른 미 분 방정식 표현으로 변경하면 다음과 같은 수식으로 정의 된다.

$$\frac{d\Phi}{dt} = \frac{df_M(q)}{dq} \frac{dq}{dt} \tag{1}$$

Fig. 2. Conduction mechanism in a TiO<sub>2</sub>/TiO<sub>2-x</sub> memristor switches states as HRS and LRS by positive or negative bias.

형 소자인 멤리스터는 저항도에 따라서 낮은 저항도를 가 지는 R<sub>ON</sub>와 높은 저항도를 가지는 R<sub>OFF</sub>가 직렬로 연결된 가변 저항으로 나타낼 수 있다 [20]. Y(t) = M(q)i(t)와 같 은 식을 바탕으로 옴의 법칙을 활용하여 아래와 같은 멤리 스터의 전압과 전류의 관계를 가진다.

$$v(t) = \left(R_{ON} \frac{\omega(t)}{L} + R_{OFF} \left(1 - \frac{\omega(t)}{L}\right)\right) i(t)$$

(2)

L은 멤리스터 소자의 크기이며  $\omega(t)$ 는 시간에 따라 변하 는 도핑 영역의 크기로서 다음과 같은 수식으로 계산된다.

$$\frac{d\omega(t)}{dt} = \mu_V \frac{R_{ON}}{I} i(t) \tag{3}$$

$\mu(t)$ 은 양이온의 평균 이동도이며 위 식에서  $\omega(t)$ 를  $\mathbf{x}(t)$  =  $\omega(t)/L$ 로 대체하면 다음과 같은 수식을 유도할 수 있다.

$$\frac{dx(t)}{dt} = \mu_V \frac{R_{ON}}{L} i(t) \tag{4}$$

위 식을 바탕으로 멤리스터를 모델링할 시 다음과 같은 수식을 정의할 수 있다.

$$M(t) = R_{OFF} \left( \sqrt{1 - \frac{2c(t)}{r}} \right) \tag{5}$$

한편, 자속( $\Phi$ )의 크기는  $L^2/\mu$ 이며,  $r = R_{OFF}/R_{ON}$ . c(t)=  $\mu_{\nu} \Phi(t)/L^2$ 이다. 이를 위의 식에 대입하면 최종적으로 다 음과 같이 계산된다.

$$x(t) = 1 - \left(\sqrt{1 - \frac{2\phi(t)}{r\beta}}\right) \tag{6}$$

멤리스터의 측정은 상부 전극에 전압을 인가하고, 하부 전극을 접지로 사용하였다. TiO<sub>2-x</sub> 박막은 Ti와 산화 과정 에서 산소가 결핍되어 형성된다 [11,21-23]. TiO<sub>2-x</sub>는 산 멤리스턴스  $\mathrm{d}f_M\left(q\right)/\mathrm{d}q$ 를  $M\left(q\right)$ 라 정의하면 저항 가변 소의 결핍도만큼 공핍되는 부분이 형성되는데 공핍층에 양 이온이 분포되어 전도도가 매우 높다. 그러나 TiO<sub>2</sub> 박막은 절연층의 역할을 하기에 전도도가 매우 낮으며 바이어스에 인가하는 방향에 따라 TiO<sub>2</sub>/TiO<sub>2-x</sub>의 경계면이 이동을하게 된다. TiO<sub>2-x</sub> 박막에 양의 전압 바이어스를 인가하면두 전극 사이에 통로(filament)가 형성되는데 이를 electroforming이라 일컬으며 소자에 인가되는 전압과소자 내부 온도에 의해 결정된다. 이는 멤리스터를 낮은 저항을 가지는 low resistance state (LRS)로 만들며 전도도가 높은 상태(write)로 전환된다. 반대로 음의 전압 바이어스를 인가하면 두 전극 사이의 통로의 파열이 발생하여저항이 높아지는데 이는 멤리스터를 높은 저항을 가지는 high resistance state (HRS)로 만들며 전도도가 낮은 고저항(read) 상태으로 만든다 [10,24,25].

### 3. 결과 및 고찰

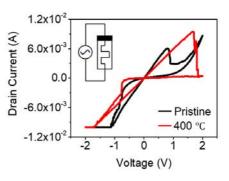

그림 3은 KEITHLEY사의 SYSTEM 2636A source meter 모델을 이용하여 어닐링 여부에 따른 TiO<sub>2</sub>/TiO<sub>2-x</sub> 박막 기반 멤리스터 소자의 전기적 특성을 판단하기 위해 측정한 I-V 곡선을 나타낸다. 그림 3 그래프에서 멤리스터 소자는 각각의 전극에 -2~2 V의 전압을 소자에 인가하였 을 때 I-V 곡선은 히스테리시스 형태를 가지는 것을 알 수 있다. 가해 준 전압에 의한 전류 값의 스위칭은 전자의 이 동통로인 filament가 소멸과 생성을 반복함을 나타낸다. 이 그래프를 통해 소자의 비휘발성 메모리 특성인 메모리 의 write, read 특성이 나타나는 것을 알 수 있다. 어닐링 을 진행하지 않은 소자의 경우, 0~2 V에서 다소 불안정한 HRS를 볼 수 있다. Reverse sweep 단계에서는 미약한 LRS로의 상태 변환을 확인할 수 있으며 동시에 current level이 높아지는 것을 볼 수 있다. 멤리스터의 상태는 -2 V 까지 상태가 유지되던 중, reverse sweep 단계에서는 -1 V 에서 다시 LRS로 변하는 현상을 볼 수 있으며 동시에 current level이 높아지는 것을 볼 수 있다. 이러한 현상 은 멤리스터의 read 성능을 의미한다. 400℃에서 60분 동 안 어닐링을 진행한 소자의 경우, 어닐링을 진행하지 않은 소자에 비해 0~2 V에서 상대적으로 온전한 HRS를 볼 수 있다. Reverse sweep 단계에서도 상대적으로 온전한 LRS로의 상태 변환을 확인할 수 있으며 동시에 current level이 높아지는 것을 볼 수 있다. 이러한 멤리스터의 상 태가 유지되던 중 reverse sweep 단계에서는 -1.5 V에서 다시 LRS로 변하는 현상을 볼 수 있으며 동시에 current level이 높아지는 것을 볼 수 있다. 이를 토대로 어닐링을 진행한 소자가 어닐링을 진행하지 않은 소자에 비해 상대

Fig. 3. I-V curves applied -2 V to 2 V of  $TiO_2/TiO_{2-x}$  based memristor non annealing and 400°C 60 min annealing.

적으로 히스테리시스 곡선의 형태가 온전하며 HRS, LRS 상태의 스위칭 폭이 높은 것을 확인할 수 있다. 이를 통해 어닐링 과정이  $TiO_2/TiO_{2-x}$  기반 박막 멤리스터 소자에 전 기적 성능 향상에 영향을 끼쳤음을 알 수 있다. 이는 어닐 링이 소자의 공정과정에서 결정 입도가 증가하고 재결정 화를 통해  $TiO_{2-x}$  박막의 산소 공공이 증가하여 filament 의 형성에 영향을 끼쳐 전기적 특성이 향상되었다는 것을 유추할 수 있다 [26].

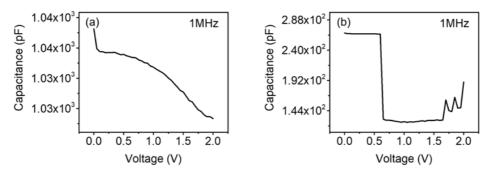

그림 4는 NF사의 ZM2410 LCR meter 장치를 활용하여 TiO<sub>2</sub>/TiO<sub>2-x</sub> 박막 기반 멤리스터 소자에 대하여 1 MHz 주파수를 적용한 C-V 곡선의 측정 결과이다. 소자 (a)는 어닐링을 진행하지 않은 소자, (b)는 400°C에서 60분 동안 어닐링을 진행한 소자이다. 0~2 V 범위에서 sweep이 되며, 바이어스 전압이 플랫 밴드 전압보다 높아지면 소자 내의 캐리어 농도는 도핑 농도보다 낮아지기 시작하고, 반도체 표면은 고갈 영역 상태로 급격하게 감소한다. 소자 (b)의 경우 0.7 V보다 높을 때 고갈 상태로 급격히 감소하는 모습을 보이나, 소자 (a)의 경우 이러한 변화가 보이지 않는 것을 확인할 수 있다.

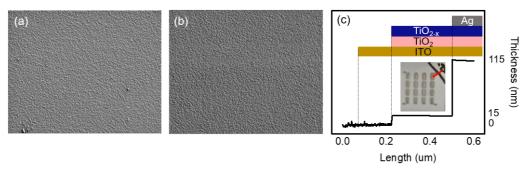

그림 5는 ZIESS사의 GeminiSEM 460 High Resolution - Scanning Electron Microscope 장치를 활용하여 측정한 어닐링 여부의 차이를 두고 제작된 TiO2/TiO2-x 기반 멤리스터 소자 표면의 이미지와 소자의 단차를 측정한 모습이다. 그림 5(a)는 어닐링을 진행하지 않은 소자의 표면을, (b)는 400°C에서 어닐링을 진행한 소자의 표면을 나타내며, (c)는 제작된 소자의 모습과 Bruker사의 DektakXT을 이용하여 측정한 멤리스터 소자의 구성을 단차로 나타낸 그래프이다. 소자 (b)는 소자(a)에 비해 particle이 적고 표면의 거칠기가 줄어든 것을 확인할 수 있다. 이는 공정과정에서 발생한 crack과 표면 손상이 고온의 어닐링 과정을 통한 재결정화로 인해 완화되어 표면 거칠기가 감소한 것으로 해석된다.

Fig. 4. C-V curves applied -2 V to 2 V of TiO<sub>2</sub>/TiO<sub>2-x</sub> based memristor (a) non annealing and (b) 400°C 60 min annealing.

Fig. 5. SEM image of TiO<sub>2</sub>/TiO<sub>2-x</sub> based memristor (a) non annealing, (b) 400°C 60 min annealing, and (c) depth profile of TiO<sub>2</sub>/TiO<sub>2-x</sub> based memristor with annealing.

Fig. 6. Schematic illustration of energy band gap diagram (a) TiO<sub>2-x</sub>, (b) TiO<sub>2-x</sub> with annealing, (c) transmittance of TiO<sub>2-x</sub>, and (d) Tauc plot of TiO<sub>2-x</sub>.

Fig. 7. (a) Schematic of Mechanism of memristor retention test, result of retention test TiO<sub>2</sub>/TiO<sub>2-x</sub> memristor based in annealing (b) 200 sec, (c) 300 sec, and (d) 1,000 sec.

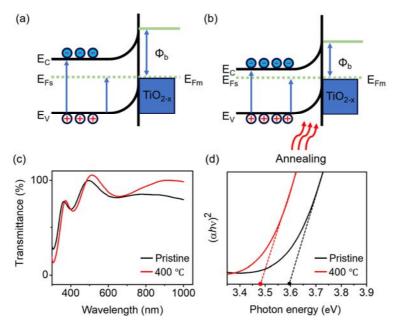

그림 6은 HUMAN사의 X-ma 3000 spectrometer 장치를 이용하여  $TiO_{2-x}$  박막의 열처리 여부에 따른 에너지 밴드갭 변화를 나타낸 모식도와 측정 결과를 나타낸다. (a)는 어닐링이 진행되지 않은  $TiO_{2-x}$ , (b)는 어닐링이 진행된  $TiO_{2-x}$ 를 시각적으로 나타낸 모식도이며, (c)는 X-ma 3000 spectrometer 장치를 이용해 측정한  $TiO_{2-x}$ 의 투과도, (d)는 투과도를 통해 도출해낸 타우 그래프이다.  $TiO_2$ 의 경우  $400^{\circ}$ C의 온도에서 어닐링할 경우 광촉매 반응성이 가장 높은 것으로 알려져 있다 [27]. 타우 그래프는 비정질 반도체의 밴드갭 에너지를 구하기 위해 사용되며 일반적으로 타우 그래프는 x축을 빛의 에너지, y축을  $(\alpha hv)^2$ 으로 놓는다 [28].  $\alpha$ 는 물질의 흡광도, h는 플랑크 상수, v는 빛의 진동수를 의미하며 물질의 흡광도는 물질의 빛 투과도(T)와 로그 함수 관계를 가진다.

또한 빛의 에너지와  $(\alpha h v)^2$ 는 다음과 같은 식 (7)로 계산 가능하다 [29,30].

$$\alpha = \log\left(\frac{1}{T}\right) \tag{7}$$

이때 c는 빛의 속도,  $\lambda$ 는 빛의 파장을 의미하므로 식 (8) 는 다음과 같이 나타낼 수 있다.

$$E_{photon} = hv = h\left(\frac{c}{\lambda}\right) \tag{8}$$

또한 식 (9)의 식을 응용하여  $(\alpha h v)^2$ 의 값을 유도할 수 있다 [31].

$$hV = \frac{1239.9eV}{\lambda} \tag{9}$$

타우 그래프를 통해 얻어진 소자의 밴드갭 에너지는  $400^{\circ}$ C에서 60분간 어닐링을 진행한 소자가 3.48 eV를, 어닐링을 진행하지 않은 소자는 3.59 eV의 값을 유도할 수있었다. 이는 어닐링 여부가 밴드갭의 범위를 변화하여  $TiO_{2-x}$  박막의 저항을 변화시키는 데 영향을 끼칠 수 있으며 이는 멤리스터 소자의 전기적 성능 변화가 일어났음을 의미한다 [29,31].

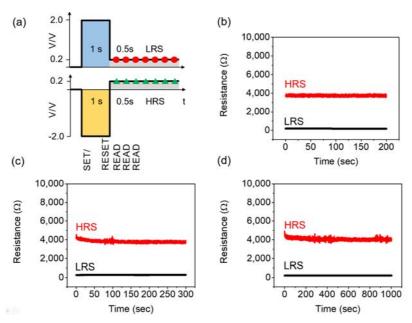

부 그림 7은 retention test의 메커니즘과 400℃에서 60분간 어닐링을 진행한 TiO₂/TiO₂-x 멤리스터 소자에 대한 retention test의 결과이다. 그림 7(a)는 retention test의 매커니즘을 나타낸 모식도이며, (b)는 200초, (c)는 300초, (d)는 1,000초 동안 retention test를 진행한 결과를 나타 낸 그래프이다. 비휘발성 메모리로 동작하기 위해서는 소자의 동작 상태 유지가 필수적이다 [32-34]. 메모리 소자의 동작 상태 유지가 필수적이다 [32-34]. 메모리 소자의 유작 상태 유지가 필수적이다 [32-34]. 메모리 소자의 무작이로 인가하여 측정하였다. 그림 7(b)의 결과를 통해 어닐링을 진행한 소자는 HRS에서의 평균 저항이 4.9× 10⁴Ω, 표준편차가 ±2.31×10²Ω이고, LRS에서는 평균 저항이 1.69×10²Ω, 표준편차가 ±9.38 Ω로 변화가 거의 없

이 일관적으로 유지되는 것을 확인할 수 있다. 또한 (c) 300 초, (d) 1,000초에서도 유사한 경향을 보이며 이를 통해서 1,000초 이상의 시간에서도 안정적인 모습을 보일 것으로 예상 가능하다.

### 4. 결 론

본 연구에서는 공정변수가 TiO₂/TiO₂-x 기반 박막 멤리스터에 미치는 효과를 확인하기 위해 400℃에서 60분간 어닐링 공정을 수행하였고, 이를 통해 제작된 소자의 전기적성능 평가와 밴드갭을 측정하였다. 결론적으로 어닐링을 진행한 소자가 어닐링을 진행하지 않은 소자에 비해 I-V curves에서 히스테리시스 곡선의 형태가 온전하며, current level이 높음을 알 수 있었다. 또한 밴드갭의 범위는 어닐링을 진행한 소자(3.48 eV)가 어닐링을 진행하지 않은 소자(3.59 eV)에 비해 0.11 eV 줄어들었음을 파악할 수 있다. 소자의 안정성과 비휘발성 메모리로서의 잠재적 응용 가능성을 판단할 수 있는 retention test에서도 어닐링을 진행한 소자의 안정성 또한 높았음을 알 수 있었다. 이는 멤리스터 소자의 구조적인 변화를 주지 않고 공정변수를 활용하여 전기적 안정성의 향상과 저항의 변화를 확인하였다.

## **ORCID**

Sung-Jin Kim

https://orcid.org/0000-0001-7739-5328

## 감사의 글

This research was partly supported by Innovative Human Resource Development for Local Intellectualization program through the Institute of Information & Communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) IITP-2024-2020-0-01462 (34%), in part by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by Ministry of Education under Grant 2020R1A6A1A12047945 (33%), and in part by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education under Grant RS-2023-00249610 (33%).

### **REFERENCES**

- Y. Chen, *IEEE Trans. Electron Devices*, **67**, 1420 (2024). doi: https://doi.org/10.1109/TED.2019.2961505

- [2] K. Sun, J. Chen, and X. Yan, Adv. Funct. Mater., 31, 2006773 (2021). doi: https://doi.org/10.1002/adfm.202006773

- [3] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, *Nature*, **453**, 80 (2008). doi: https://doi.org/10.1038/nature06932

- [4] W. Chen, L. Song, S. Wang, Z. Zhang, G. Wang, G. Hu, and S. Gao, Adv. Electron. Mater., 9, 2200833 (2023). doi: https://doi.org/10.1002/aelm.202200833

- [5] F. T. Chin, Y. H. Lin, H. C. You, W. L. Yang, L. M. Lin, Y. P. Hsiao, C. M. Ko, and T. S. Chao, *Nanoscale Res. Lett.*, 9, 592 (2014). doi: https://doi.org/10.1186/1556-276X-9-592

- [6] Y. Li, Z. Wang, R. Midya, Q. Xia, and J. J. Yang, *J. Phys. D: Appl. Phys.*, **51**, 503002 (2018). doi: https://doi.org/10.1088/1361-6463/aade3f

- [7] R. Waser, R. Dittmann, G. Staikov, and K. Szot, *Adv. Mater.*,

21, 2632 (2009).

doi: https://doi.org/10.1002/adma.200900375

- [8] Q. Li, A. Khiat, I. Salaoru, C. Papavassiliou, X. Hu, and T. Prodromakis, *Sci. Rep.*, 4, 4522 (2014). doi: https://doi.org/10.1038/srep04522

- [9] S. J. Song, J. Y. Seok, J. H. Yoon, K. M. Kim, G. H. Kim, M. H. Lee, and C. S. Hwang, *Sci. Rep.*, 3, 3443 (2013). doi: https://doi.org/10.1038/srep03443

- [10] K. Eshraghian, K. R. Cho, O. Kavehei, S. K. Kang, D. Abbott, and S.M.S. Kang, *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, 19, 1407 (2011). doi: https://doi.org/10.1109/TVLSI.2010.2049867

- [11] A. Sahoo, P. Padhan, and W. Prellier, ACS Appl. Mater. Interfaces, 9, 36423 (2017). doi: https://doi.org/10.1021/acsami.7b11930

- [12] R. U. Chandrasena, W. Yang, Q. Lei, M. U. Delgado-Jaime, K. D. Wijesekara, M. Golalikhani, B. A. Davidson, E. Arenholz, K. Kobayashi, M. Kobata, F.M.F. de Groot, U. Aschauer, N. A. Spaldin, X. Xi, and A. X. Gray, *Nano Lett.*, 17, 794 (2017). doi: https://doi.org/10.1021/acs.nanolett.6b03986

- [13] Y. Xiao, B. Jiang, Z. Zhang, S. Ke, Y. Jin, X. Wen, and C. Ye, Sci. Technol. Adv. Mater., 24, 2162323 (2023). doi: https://doi.org/10.1080/14686996.2022.2162323

- [14] S. Lee, H. Kim, D. J. Yun, S. W. Rhee, and K. Yong, *Appl. Phys. Lett.*, **95**, 262113 (2009). doi: https://doi.org/10.1063/1.3280864

- [15] S. Kim and Y. K. Choi, *IEEE Trans. Electron Devices*, **56**, 3049 (2009).

doi: https://doi.org/10.1109/TED.2009.2032597

- [16] S. Kim, H. Moon, D. Gupta, S. Yoo, and Y. K. Choi, *IEEE Trans. Electron Devices*, **56**, 696 (2009). doi: https://doi.org/10.1109/TED.2009.2012522

- [17] M. Lanza and H. Tian, Adv. Funct. Mater., 34, 2314512 (2024). doi: https://doi.org/10.1002/adfm.202314512

- [18] Y. H. Song, J. M. Lim, S. Khot, D. Jung, and Y. Kwon, *Korean J. Met. Mater.*, **62**, 212 (2024). doi: https://doi.org/10.3365/KJMM.2024.62.3.212

- [19] L. Chua, *IEEE Trans. Circuit Theory*, **18**, 507 (1971). doi: https://doi.org/10.1109/TCT.1971.1083337

- [20] H. Ha and O. Kim, Appl. Phys. Lett., 93, 033309 (2008). doi: https://doi.org/10.1063/1.2960998

- [21] K. Hoshino, N. L. Peterson, and C. L. Wiley, *J. Phys. Chem. Solids*, **46**, 1397 (1985). doi: https://doi.org/10.1016/0022-3697(85)90079-4

- [22] T. Cao, T. Xia, L. Zhou, G. Li, X. Chen, H. Tian, J. Zhao, J. O. Wang, W. Zhang, S. Li, S. Meng, and H. Guo, *J. Phys. D: Appl. Phys.*, 53, 424001 (2020). doi: https://doi.org/10.1088/1361-6463/ab9d99

- [23] M. Son, J. Lee, J. Park, J. Shin, G. Choi, S. Jung, W. Lee, S. Kim, S. Park, and H. Hwang, *IEEE Electron Device Lett.*, 32, 1579 (2011). doi: https://doi.org/10.1109/LED.2011.2163697

- [24] S. Kim and Y. K. Choi, *IEEE Trans. Electron Devices*, **56**, 3049 (2009).doi: https://doi.org/10.1109/TED.2009.2032597

- [25] A. K. Jena, M. C. Sahu, K. U. Mohanan, S. K. Mallik, S. Sahoo, G. K. Pradhan, and S. Sahoo, ACS Appl. Mater. Interfaces, 15, 3574 (2023). doi: https://doi.org/10.1021/acsami.2c17228

- [26] H. J. Lee, J. H. Kim, H. J. Kim, and S. N. Lee, *Materials*, 17, 2727 (2024). doi: https://doi.org/10.3390/ma17112727

- [27] C. P. Lin, H. Chen, A. Nakaruk, P. Koshy, and C. C. Sorrell, Energy Procedia, 34, 627 (2013). doi: https://doi.org/10.1016/j.egypro.2013.06.794

- [28] J. Klein, L. Kampermann, B. Mockenhaupt, M. Behrens, J. Strunk, and G. Bacher, *Adv. Funct. Mater.*, 33, 2304523 (2023). doi: https://doi.org/10.1002/adfm.202304523

- [29] L. Bian, M. Song, T. Zhou, X. Zhao, and Q. Dai, J. Rare Earths, 27, 461 (2009). doi: https://doi.org/10.1016/S1002-0721(08)60270-7

- [30] L. G. Ferreira, M. Marques, and L. K. Teles, *Phys. Rev. B*, 78, 125116 (2008). doi: https://doi.org/10.1103/PhysRevB.78.125116

- [31] P. Makuła, M. Pacia, and W. Macyk, J. Phys. Chem. Lett., 9, 6814 (2018). doi: https://doi.org/10.1021/acs.jpclett.8b02892

- [32] L. Wang, Z. Su, and C. Wang, Appl. Phys. Lett., 100, 213303 (2012).doi: https://doi.org/10.1063/1.4721518

- [33] T. Wang, Z. Cui, Y. Liu, D. Lu, M. Wang, C. Wan, W. R. Leow, C. Wang, L. Pan, X. Cao, Y. Huang, Z. Liu, A.I.Y. Tok, and X. Chen, *Adv. Mater.*, 34, 2106212 (2022). doi: https://doi.org/10.1002/adma.202106212

- [34] W. G. Lee, B. E. Park, and K. E. Park, *Met. Mater. Int.*, 19, 597 (2023).doi: https://doi.org/10.1007/s12540-013-3032