ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online)

논문번호 24-03-18

https://doi.org/10.7471/ikeee.2024.28.3.369

# 트랜지스터의 온도 계수를 고려한 커패시터리스 디램의 설계 최적화

# Design Optimization of Capacitor-less DRAM using zero-temperature coefficient point

김 경 희<sup>1</sup>, 김 경 민<sup>1</sup>, 김 영 환<sup>1</sup>, 임 종 범<sup>1</sup>, 최 규 호<sup>1</sup>, 강 인 만<sup>2</sup>, 윤 영 준<sup>1\*</sup>

Kyung Hee Kim<sup>1</sup>, Kyeong Min Kim<sup>1</sup>, Yeong Hwan Kim<sup>1</sup>, Jong Beom Im<sup>1</sup>, Gyu Ho Choi<sup>1</sup>, In Man Kang<sup>2</sup>, Young Jun Yoon<sup>1</sup>

#### **Abstract**

This paper addresses the design optimization of capacitorless DRAM(one-transistor DRAM., 1T-DRAM), which has gained attention as a next-generation memory technology. To overcome the limitations of conventional capacitor-based DRAM, an asymmetric dual-gate structure is proposed to enhance retention time and overall performance. The zero-temperature coefficient (ZTC) point is set at 1.25 V to minimize performance degradation due to temperature variations. Current-voltage characteristics were analyzed at various temperatures (300K-400K), confirming stable memory operation at the ZTC point, even under temperature fluctuations. The proposed design demonstrates reliable operation at high temperatures, proving the potential for high-efficiency, highly reliable memory technology. As a result, the 1T-DRAM device can make a significant contribution to the development of next-generation memory devices.

## 요 약

본 논문에서는 차세대 메모리 기술로 주목받고 있는 커패시터리스 디램(one-transistor DRAM, 1T-DRAM)을 소자의 설계 최적 화에 대해 다룬다. 기존 커패시터기반 DRAM의 한계를 해결하고자, 비대칭 듀얼 게이트 구조를 사용하여 보유 시간 및 성능을 향상 시키는 방향성을 제시한다. ZTC(Zero-temperature coefficient) 지점을 1.25 V로 설정하여 온도 변화에 따른 성능 저하를 최소 화하였다. 다양한 온도(300K~400K)에서 전류-전압 특성을 분석하여, ZTC 지점에서의 메모리 특성이 온도에 안정적으로 동작하는 것을 확인하였으며, 고온에서도 신뢰성 있는 동작을 보장하는 설계가 가능함을 입증하였다. 이를 통해 1T-DRAM 소자는 높은 신뢰 성과 고효율을 갖춘 메모리 기술로서, 차세대 메모리 소자 개발에 중요한 기여를 할 수 있다.

Key words: Capacitorless DRAM, One transistor DRAM, Zero-temperature coefficient point, Sensing margin, Retention time

E-mail: yjyoon@anu.ac.kr, Tel: +82-54-820-5750

\* Acknowledgment

This work was supported by a grant from 2024 Research Fund of Andong National University.

Manuscript received Sep. 13, 2024; revised Sep. 19, 2024; accepted Sep. 24, 2024.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>1</sup> Department of Electronic Engineering, Andong National University, Andong 36729, Korea

<sup>2</sup> School of Electronic and Electrical Engineering, Kyungpook National University, Daegu 41566, Korea

<sup>★</sup> Corresponding author

#### 1. 서론

디램(Dynamic random-access memory, DRAM) 기술은 커패시터 관련 제한 사항으로 인해 소자 축소화 공정에 한계를 겪고 있다. 커패시터 기반 디램은 소자 축 소화 공정에서 커패시터의 크기와 충전 유지 능력 문제 로 인해 한계에 도달하고 있으며, 고온 환경에서 성능 저 하와 누설 전류 증가 문제를 겪고 있다. 또한, 지속적인 데이터 리프레시 요구로 인한 전력 소모 증가가 중요한 문제로 부각되고 있다. 이러한 한계를 극복하기 위해 최 근에는 커패시터 없이 메모리 동작이 가능한 커패시터리스 디램(capacitor-less DRAM, one-transistor DRAM, 1T-DRAM)[1]-[9] 소자 기술에 대한 연구가 활발히 이 루어지고 있다. 1T-DRAM 기술은 소자 축소화 문제를 해결하고 더 높은 집적도를 가능하게 하며, 고온 환경에 서의 디램 성능을 개선할 수 있는 잠재력을 가지고 있다. 디램과 같은 반도체 소자의 전기적 특성은 온도 변화에 크게 영향을 받으며, 이는 메모리 소자의 성능과 신뢰성 에 직접적인 영향을 미친다. 특히, 트랜지스터의 온도 계 수(Zero Temperature Coefficient, ZTC)[10]-[12] 지 점은 온도 변화에 따른 전류 변화가 없는 지점으로, 안정 적인 동작을 위해 중요한 역할을 한다. ZTC 지점에서의 동작은 다양한 온도 환경에서도 일정한 성능을 유지할 수 있게 해주며, 이는 고온 환경에서도 신뢰성 있는 메모 리 소자를 개발하는 부분에서 활용할 수 있다. 본 논문에 서는 트랜지스터의 온도 계수를 고려한 1T-DRAM의 설 계 최적화에 대해 다룬다. 이를 위해 다양한 온도에서 전 류-전압 특성을 분석하고, ZTC 지점을 활용하여 온도 변화에 따른 성능 변화를 최소화하는 설계 방법을 제시 한다. 따라서, 이 연구는 1T-DRAM의 설계와 최적화를 통해 고효율, 고신뢰성 메모리 소자 개발에 기여하고자 하며, 이를 통해 차세대 메모리 기술의 발전에 중요한 기 반을 제공하고자 한다.

#### II. 본론

# 1. 1T-DRAM 구조 및 온도에 따른 전류 특성

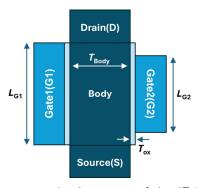

그림 1은 1T-DRAM의 구조를 보여주며, 보유시간 향상 및 메모리 기술 최적화를 위해 비대칭 듀얼 게이트 구조로 설계하였다[7].

표 1에 제시된 1T-DRAM의 구조 변수는 장치 성능에 중요한 역할을 하며, 이 조건을 기반으로 Sentaurus TCAD 시뮬레이션을 통해 분석하였다. Gate 1의 길이 ( $L_{GI}$ )는 100nm, Gate 2의 길이( $L_{G2}$ ) 70nm로 설정되어, 각 게이트는 소스 및 드레인과의 전기장 분포를 조정하여 누설 전류를 최소화하고 전하 보유 성능을 향상시킨다. 바디 두께는 27nm로 얇게 설계되었으며, 산화물두께는 3nm이다. 또한, 소스와 드레인 영역은 N형 물질, 바디는 P형 물질로 도핑하였다. 메인 게이트와 컨트롤 게이트의 일함수는 각각 4.85 eV와 5.3 eV로 설정하였고, 이러한 일함수 차이는 실리콘 바디 내에서 전하의저장 및 효율성을 극대화하는데 중요한 역할을 한다.

Fig. 1. A cross-sectional structure of the 1T-DRAM.

그림 1. 1T-DRAM 구조 단면

Table 1. Structure parameters of the 1T-DRAM.

표 1. 1T-DRAM 구조 변수

| Parameters                        | Values [Units]                                |  |

|-----------------------------------|-----------------------------------------------|--|

| Gate1 Length (LG1)                | 100 [nm]                                      |  |

| Gate2 Length (LG2)                | 70 [nm]                                       |  |

| Body Thickess ( $T_{Body}$ )      | 27 [nm]                                       |  |

| Oxide Thickness ( $T_{ox}$ )      | 3 [nm]                                        |  |

| Source/Drain doping concentration | N-type, 5 x 10 <sup>19</sup> cm <sup>-3</sup> |  |

| Body doping concentration         | P-type, 1x 10 <sup>18</sup> cm <sup>-3</sup>  |  |

| Main gate work-function(WF1)      | 4.85 eV                                       |  |

| Control gate work-function(WF2)   | 5.3 eV                                        |  |

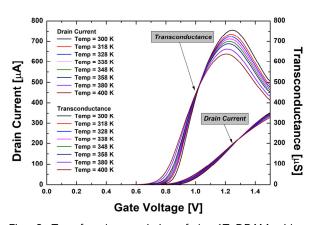

그림 2는 다양한 온도 (300K~400K)에서 게이트 전압에 따른 드레인 전류 및 트랜스컨덕턴스 변화를 나타낸다. ZTC 지점은 온도 변화에 따른 전류 변화가 거의 없는 전압 지점으로, 1T-DRAM 소자의 온도 민감도를 최소화하는 중요한 역할을 한다. 여러 전압 조건에서 드레인 전류의 온도 민감도를 분석한 결과, 1.25 V에서 ZTC특성이 가장 뚜렷하게 나타났기 때문에, 본 소자에서는 ZTC 지점을 1.25 V로 설정하였다. 게이트 전압이 1.25 V일 때, 온도가 300K에서 400K로 변화하더라도 드레인 전류는 일정하게 유지된다. 이는 ZTC 지점에서 캐리

어 이동도와 재결합/생성이 온도 변화에 대해 상대적으로 안정적으로 유지되기 때문이다 [10]. ZTC 지점 부근에서는 트랜스컨덕턴스의 변화도 최소화되며, 이는 온도변화에 관계없이 전류 제어 능력이 일정하게 유지된다는 것을 의미한다. 결론적으로, 1.25 V에서의 ZTC 지점은 1T-DRAM 소자의 안정적인 동작을 보장하는 전압 구간으로, 온도 변화에 따른 드레인 전류의 변화가 최소화된다. 이로 인해 1T-DRAM 소자는 다양한 온도 환경에서도 일정한 성능을 유지할 수 있으며, 특히 고온 환경에서의 신뢰성을 높일 수 있다.

Fig. 2. Transfer characteristics of the 1T-DRAM with variation of temperature.

그림 2. 온도 변화에 따른 1T-DRAM 전류 특성

#### 2. 온도에 따른 1T-DRAM 메모리 특성

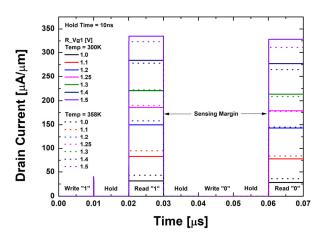

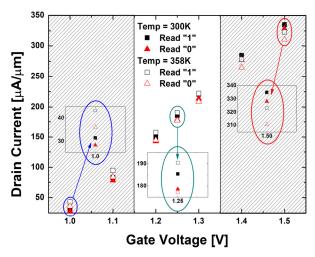

그림 3에서 1.0 V에서 1.5 V의 전압은 읽기 상태에서 의 각각의 게이트 전압(R\_Vg1)을 나타낸다. 이 전압 값은 1T-DRAM의 메모리 성능을 다양한 조건에서 분석하기 위해 설정된 값들로, 주어진 온도(300K, 358K)에서 메모리의 쓰기(Write), 읽기(Read) 상태에서의 드레인전류 변화를 나타낸다. 표 2에서 보인 메모리 동작 전압조건을 통하여 메모리 특성을 확인하였고, 읽기 동작의게이트 전압 조건에 따른 전류 값 변화를 관찰하였다.

Table 2. Bais conditions for memory of the 1T-DRAM. 표 2. 메모리 동작 전압 조건

|                                          | Write "1"<br>(Program) | Write "0"<br>(Erase) | Read   | Hold  |

|------------------------------------------|------------------------|----------------------|--------|-------|

| Main gate<br>voltage (V <sub>GS1</sub> ) | 2.5 V                  | 0.0 V                | 1.25 V | 0.0 V |

| Control gate voltage (V <sub>GS2</sub> ) | -2.5 V                 | 0.5 V                | 0.0 V  | 0.0 V |

| Drain voltage (V <sub>DS</sub> )         | 0.0 V                  | -0.5 V               | 0.5 V  | 0.0 V |

Fig. 3. Memory characteristics of the 1T-DRAM with variation of temperature.

그림 3. 온도 변화에 따른 1T-DRAM의 메모리 특성

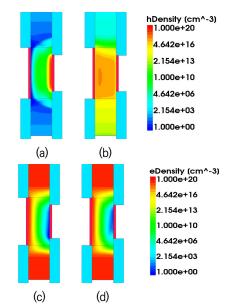

그림 4 (a)와 (b)는 온도 300K 일 때 1T-DRAM 구조에서 "1"과 "0" 상태의 쓰기(Program, Erase) 동작에 따른 정공 밀도 분포를 보여주며, (c)와 (d)는 "1"과 "0" 상태의 읽기 동작에 따른 전자 밀도 분포를 나타낸다. "1" 상태의 쓰기 동작에서는 채널 내에 정공이 축적되고, "0" 상태의 쓰기 동작에서는 정공이 방출된다. 이로 인해 읽기 동작에서의 "0"과 "1" 상태에서 정공 밀도 차이가 발생하고, 이 차이는 채널 내의 전자 밀도에도 영향을 미친다. "1"과 "0" 상태에서 전자 밀도의 차이를 통해 제안된 1T-DRAM 구조는 메모리 상태를 정확하게 구분할 수

Fig. 4. Hole density in 1T-DRAM under (a) program and (b) erase conditions. Electron density under (c) read "1" and (d) read "0" conditions.

그림 4. 1T-DRAM의 "1"과 "0" 상태 쓰기 조건에서 정공 밀도 분포 및 읽기 조건에서 전자 밀도 분포 있다. 읽기 동작의 게이트 전압(R\_Vg1)으로 1T-DRAM 동작을 확인하였을 때, 읽기 동작의 게이트 전압이 1.25 V인 경우, 300K와 358K에서 "1"과 "0" 상태에서의 읽기 전류 구분이 뚜렷한 것을 확인하였다. 이는 ZTC 현상과 일치하며, 해당 전압에서 메모리 동작이 온도 변화에 영향을 최소화하고, 안정적으로 유지됨을 의미한다.

Fig. 5. Read current at "1" and "0" states as function of gate voltage in read operation.

그림 5. 읽기 동작에서의 게이트 전압에 따른 "1"과 "0" 상태의 전류 특성

그림 5은 읽기 동작에서 게이트 전압의 최적 구간을 정하기 위하여 온도 변화와 읽기 동작에서 게이트 전압 에 의한 "1"과 "0" 상태에서의 전류 변화를 보여준다. 여 기서 화살표는 해당 구간의 값을 강조하여 확대된 그래 프를 보여주기 위한 것이며, 온도에 따른 메모리 동작의 특성 차이를 보다 명확히 나타내기 위해 사용되었다. 읽 기 동작에서 1.3 V의 게이트 전압 이상 구간에서는 300K 때의 읽기 "0" 값이 358K의 읽기 "1" 값보다 큰 역전 현상이 나타난다. 또한 읽기 동작에서 1.2 V의 게 이트 전압 이하 구간에서는 358K 때의 읽기 "0" 값이 300K의 읽기 "1" 값보다 큰 것을 알 수 있다. 이와 같은 역전 현상이 일어나면 특정 구간에서 메모리 동작의 불 안정성을 야기하며, 고온에서의 데이터 유지 성능이 저 하될 수 있다. 이러한 이유로 ZTC 지점인 1.25 V를 기 점으로 1.2 V와 1.3 V 사이 구간을 최적화 구간으로 설 정하였다. 게이트 전압이 1.25 V일 때, 300K에서의 감 지 마진은 6.959  $\mu$ A, 358K에서는 13.268  $\mu$ A로 측정하 였다.

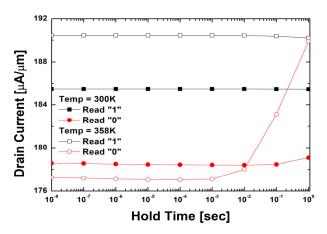

그림 6는 게이트 전압 1.25 V일 때, 300K와 358K에서의 보유시간 특성을 나타낸다. 보유시간이  $10^{-2}$ s 이전

Fig. 6. Retention characteristics of the 1T-DRAM with temperature of 300K and 358K.

그림 6. 온도 300K와 358K에서의 1T-DRAM의 보유시간 특성

까지는 300K와 358K에서 "1"과 "0" 상태일 때 전류 값이 큰 변화 없이 안정적으로 동작한다.  $10^{-2}$ s부터는 감지마진이 감소하는 경향을 보이지만, 64ms 이상의 보유 성능을 충족시킨다. 이는 고온에서도 제안된 1T-DRAM이안정적으로 동작함을 의미한다.

# Ⅲ. 결론

본 논문에서는 온도에 따른 1T-DRAM의 드레인 전류 특성 변화와 온도 변화에 따른 전류 변화가 없는 ZTC 지점을 확인하였다. 1.25 V의 ZTC 지점을 이용하여 온도에 큰 변화가 없는 1T-DRAM의 메모리 특성을 설계하기 위하여 읽기 동작에서의 게이트 전압에 따른 '1'과'0' 상태의 전류값을 비교하였다. 최종적으로 온도 변화에 민감하지 않은 1T-DRAM의 구동 전압을 최적화하였다. 향후 연구에서는 게이트 전압과 바디 두께를 조절하여, 1.2 V와 1.3 V 사이에서 보다 균일한 드레인 전류특성을 유지하고, 온도 변화에 민감하지 않은 최적화 구간을 넓히는 방안을 추가적으로 고려할 계획이다.

#### References

[1] Md. H. R. Ansari and J. Singh, "Capacitorless 2T-DRAM for Higher Retention Time and Sense Margin," *IEEE Trans. Electron Devices*, vol.67, no.3, pp.902-906, 2020.

DOI: 10.1109/TED.2020.2963995.

[2] A. Biswas and A. M. Ionescu, "1T Capacitor-Less DRAM Cell Based on Asymmetric Tunnel FET Design," *IEEE J. Electron Devices Soc.*, vol.3, no.3, pp.217-222, 2015.

DOI: 10.1109/JEDS.2014.2382759.

[3] J. H. Bae, J. W. Back, M. W. Kwon, J. H. Seo, K. Yoo, S. Y. Woo, K. Park, B. G. Park, and J. H. Lee, "Characterization of a Capacitorless DRAM Cell for Cryogenic Memory Applications," *IEEE Electron Device Lett.*, vol.40, no.10, pp.1614–1617, 2019. DOI: 10.1109/LED.2019.2933504.

[4] R. K. Nirala, A. S. Roy, S. Semwal, N. Rai, and A. Kranti, "Architectural evaluation of programmable transistor-based capacitorless DRAM for high-speed system-on-chip applications," *Jpn. J. Appl. Phys.*, vol.62, no.1040, 2023.

DOI: 10.35848/1347-4065/acb0db.

[5] J. S. Shin, H. Choi, H. Bae, J. Jang, D. Yun, E. Hong, D. H. Kim, and D. M. Kim, "Vertical-Gate Si/SiGe Double-HBT-Based Capacitorless 1T DRAM Cell for Extended Retention Time at Low Latch Voltage," *IEEE Electron Device Lett.*, vol.33, no.2, pp.134-136, 2012. DOI: 10.1109/LED.2011.2174025. [6] J. H. Seo, Y. J. Yoon, E. Yu, W. Sun, H. Shin, I. M. Kang, J. H. Lee, and S. Cho, "Fabrication and Characterization of a Thin-Body Poly-Si 1T DRAM With Charge-Trap Effect," *IEEE Electron Device Lett.*, vol.40, no.4, pp.566-569, 2019.

DOI: 10.1109/LED.2019.2901003.

[7] S. H. Lee, W. D. Jang, Y. J. Yoon, J. H. Seo, H. J. Mun, M. S. Cho, J. Jang, J. H. Bae, and I. M. Kang, "Polycrystalline-Silicon-MOSFET-Based Capacitorless DRAM With Grain Boundaries and Its Performances," *IEEE Access*, vol.9, pp.50281-50290, 2021.

DOI: 10.1109/ACCESS.2021.3068987.

[8] S. H. Lee, J. Park, Y. J. Yoon, and I. M. Kang, "Capacitorless One-Transistor Dynamic Random-Access Memory with Novel Mechanism: Self-Refreshing," *Nanomaterials*, vol.14, no.2, 2024. DOI: 10.3390/nano14020179.

[9] S. H. Lee, J. Park, S. R. Min, G. U. Kim, J. Jang, J. H. Bae, S. H. Lee, and I. M. Kang, "3-D stacked polycrystalline-silicon-MOSFET-based capacitorless DRAM with superior immunity to grain-boundary's influence," *Sci Rep*, vol.12, p.14455, 2022.

DOI: 10.1038/s41598-

[10] Z. D. Prijić, S. S. Dimitrijev, and N. D. Stojadinović, "The determination of zero temperature coefficient point in CMOS transistors," *Microelectron. Reliab.*, vol.32, no.6, pp.769-773, 1992. DOI: 10.1016/0026-2714(92)90041-I.

[11] L. M. Camillo, J. A. Martino, E. Simoen, and C. Claeys, "The temperature mobility degradation influence on the zero temperature coefficient of partially and fully depleted SOI MOSFETs," *Microelectron. J.*, vol.37, no.9, pp.952-957, 2006.

DOI: 10.1016/j.mejo.2006.01.008.

[12] T. H. Tan and A. K. Goel, "Zero-temperature-coefficient biasing point of a fully-depleted SOI MOSFET," *Microw. Opt. Technol. Lett.*, vol.37, no.5, pp. 366-370, 2003. DOI: 10.1002/mop.10920.

## **BIOGRAPHY**

#### Kyung Hee Kim (Member)

2019~present: BS degree in Electronics Engineering, Andong National University

#### Kyeong Min Kim (Member)

2018~present: BS degree in Electronics Engineering, Andong National University

#### Yeong Hwan Kim (Member)

2019~present: BS degree in Electronics Engineering, Andong National University

#### Jong Beom Im (Member)

2020~present: BS degree in Electronics Engineering, Andong National University

#### Gyu Ho Choi (Member)

2019~present: BS degree in Electronics Engineering, Andong National University

#### In Man Kang (Member)

2007: PhD degree in Electrical Engineering, School of Electrical Engineering and Computer Science, Seoul National University 2007–2010: Senior Engineer, Design Technology Team, Samsung Electronics Company.

2010~present: Professor, School of Electronic and Electrical Engineering, Kyungpook National University

#### Young Jun Yoon (Member)

2019: PhD degree in Electronics Engineering, Kyungpook National University 2020: Post Doctoral Scholar, Bio-Micro Systems Group, Korea Institute of Science and Technology (KIST).

2021: Post Doctoral Scholar, Accelerator Utilization Research Division, Korea Atomic Energy Research Institute (KAERI).

2022: Senior Researcher, Accelerator Utilization Research Division, Korea Atomic Energy Research Institute (KAERI).

2023~present: Professor, Department of Electronic Engineering, Andong National University