ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online)

논문번호 24-02-17

117

# 저전압급 ESD 보호를 위한 LRSCR 기반 Self-bias SCR에 관한 연구

# A Study on Self-bias SCR Based on LRSCR for Low Voltage Class ESD Protection

서 우 열\*, 권 상 욱\*, 오 재 윤\*, 구 용 서\*\*

U-Yeol Seo\*, Sang-wook Kwon\*, Jae-yoon Oh\*, Yong-Seo Koo

# **Abstract**

This paper proposed an ESD protection device that improved the current driving ability through Self-bias than the existing ESD protection device. The new proposed structure is based on the LRSCR structure and adds an N+ diffusion region, and reduces resistance by connecting the gate and the P+ diffusion region. As a result, it was confirmed that the proposed ESD protection device exhibits a trigger voltage of 11.8V and a holding voltage of 5.9V. It can be used in 5V applications for low voltage and is expected to have excellent current driving capability.

### 요 약

본 논문에서는 기존의 ESD 보호소자보다 Self-bias를 통하여 전류구동 능력을 향상시킨 ESD 보호소자를 제안하였다. 새로운 제안 구조는 LRSCR구조 기반이며 N+ 확산 영역을 추가하였으며 게이트와 P+ 확산영역을 연결하여 저항을 감소시킨다. 그 결과, 제안된 ESD 보호소자는 11.8V의 트리거 전압과 5.9V의 홀딩 전압을 나타내는 것으로 확인되었다. 저전압용 5V 애플리케이션에 사용될 수 있으며 우수한 전류구동능력을 가지고있을 것으로 기대된다.

Key words: ESD, LRSCR, Self-bias., Application, LVTSCR

#### 1. 서론

반도체 공정 기술의 발전으로 소자가 점점 소형화 되어지면서 IC 장치 고장의 많은 문제 중에서 고열 파괴로

인한 ESD 보호의 중요성이 더욱 부각 되어지고 있다[1]. 정전기 방전(Electro-Static Discharge; ESD)는 서로 다른 극성을 축적된 정전하가 마찰 또는 대전 등에 의해 매우 빠르게 방전되는 현상으로 마찰전기 현상과 관련되

Dept. of Electronics Engineering, Dankook University

★ Corresponding author

E-mail: tjdnduf100@dankook.ac.kr, Tel: +82-031-8005-3625

\* Acknowledgment

This paper was supported by Korea Evaluation Institute of Industrial Technology (KEIT) grant funded by the Korea Government(MOTIE)(RS-2024-00403586, Development of Reinforced Insulated High Reliability Integrated Power IC Technology including Digital Precision Control) and conducted with the support of the Compound Material-based Next Generation Power Semiconductor Technology Development Project of the Ministry of Trade, Industry and Energy and the Korea Institute for Industrial Technology Evaluation (RS-2022-00143842, "Single/Three-phase AC/DC Converter Smart Power IC using SiC MOSFET devices")

Manuscript received, Jun. 10, 2024; revised Jun. 19, 2024; accepted Jun. 24, 2024.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited

어 잘 알려진 물리 현상이다. 반도체의 IC 고장 원인은 매우 다양하지만, 그중에서 ESD/EOS 현상으로 인한 파 괴가 40%에 달한다. ESD 보호가 되지 않는다면, ESD 전류가 방전되면서 산화막 게이트, 금속 전극 및 접합 부 분이 손상될 수 있다[2]. 따라서 ESD 보호소자는 반도체 IC(집적회로)의 안정성과 신뢰성에 있어 매우 중요한 이 슈 중 하나로 대두된다[3]-[4]. IC를 ESD로부터 보호하 기 위해 Diode, SCR(Silicon Controlled Rectifier)과 GGNMOS(Grounded-Gate NMOS)가 ESD 보호 장치 로 널리 알려져 있다. SCR은 두 개의 기생 바이폴라 트 랜지스터를 통해 전류를 방전시켜 높은 전류 구동 능력 을 제공한다. 하지만 트리거 전압은 높고, 홀딩 전압은 낮기 때문에 모바일 기기 적용에는 어려움이 있다[5]. 선 행 연구된 LVTSCR(Low Trigger SCR)과 LRSCR(Low Ron SCR)은 트리거 전압이 높고, 홀딩 전압이 낮은 문 제점을 가지고있어 이를 개선하기 위해 기존 SCR의 구 조적 변형을 진행 하였다. 전류구동 특성을 향상시키기 위해 확산 영역을 추가하여 저전압급 어플리케이션에 최 적화 하였다[6]. 따라서 본 논문에서는 기존 SCR의 특성 을 개선하기 위해 구조적인 변형과 홀딩 전압이 높은 SCR 기반 ESD 보호 소자를 제안한다. 이 제안된 소자는 Synopsys 사의 T-CAD를 이용하여 검증되었다.

# Ⅱ. 본론

#### 1. ESD 보호소자 단면도 및 분석

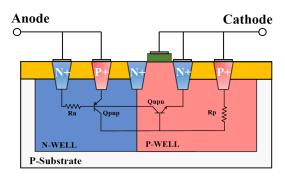

LVTSCR와 LRSCR 구조의 단면도를 그림 1, 2에 보여준다.

Fig. 1. Cross sectional of the conventional LVTSCR.

그림 1. LVTSCR의 단면도

LVTSCR(Low Voltage Triggered SCR)은 SCR에 GGNMOS 구조를 결합하여 애벌런치 항복 전압을 낮추고 트리거 전압을 감소시킨다. 동작 원리는 다음과 같다.

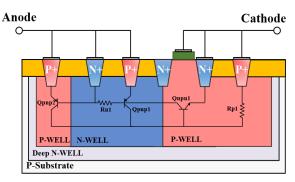

Fig. 2. Cross sectional of the conventional LRSCR. 그림 2. LRSCR의 단면도

정상 상태에서는 N-Well과 P-Well 사이에 역방향 접합 이 형성되어 있어 ESD 보호 소자가 동작하지 않는다. 그 러나 ESD 서지가 발생하면 N+ 브릿지와 P-Well 사이 에서 임계점 이상이되면 애벌런치 현상이 일어나 생성된 전자-정공 쌍 중 전공전류는 P+ 캐소드 쪽으로 이동하 며 P-Well의 전위를 증가시킨다. 이때, P-Well의 전위 가 P-Well과 N+ 캐소드 사이의 순방향 접합이 되면서 기생 NPN 트랜지스터가 작동하고, 동시에 기생 PNP 트 랜지스터도 작동하게 된다. 이 과정으로써 SCR 동작을 하게 되며, 두 BJT는 서로의 베이스 전류를 공급하게 되 면서 정궤환 루프를 이루게 된다. 정궤환 루프 형성으로 전류구동능력을 갖는다. 구조적으로 보게되면 LVTSCR 은 N+ 브릿지 영역으로 인해 낮은 트리거 전압을 가지 게된다. 하지만 홀딩 전압이 낮기 때문에 Latch-up 문 제를 가지고 있는 단점이 존재한다. 이 문제는 LRSCR에 서도 마찬가지로 존재한다. LRSCR의 동작 원리는 LVTSCR과 비슷하지만, 추가적인 N-Well의 왼쪽에 P-Well과 P+ 영역을 추가하여 추가적인 기생 PNP 트 랜지스터가 활성화 된다. 이는 전류의 병렬 방전 경로를 증가시켜 on 저항을 낮추고, 결과적으로 홀딩 전압을 개 선하는 효과를 가져온다. 하지만 여전히 홀딩 전압이 낮 기 때문에 Latch-up 현상에서 자유로울 수 없다. 따라

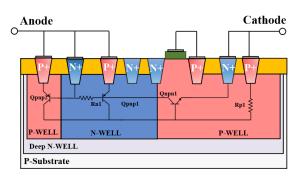

Fig. 3. Cross sectional of Proposed ESD protection device. 그림 3. 제안된 ESD 보호 소자 단면도

서 본 논문에서는 간단한 구조 변형으로 높은 홀딩 전압을 갖는 ESD 보호 소자를 제안한다.

그림 3은 제안하는 보소호자의 단면도를 나타낸다. 동작원리는 LVTSCR과 LRSCR과 유사하다. 하지만 추가적인 N+확산영역을 추가하여 홀딩전압을 높였으며 게이트와 P+확산영역을 연결하였다. 이는 게이트에 전압이인가되기 때문에 P-Well의 농도의 변화가 일어나게 되며, 순간적으로 P-Well의 저항이 낮아지는 효과가 존재한다. 결과적으로 홀딩전류의 상승으로 이어지게 된다.

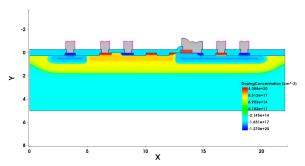

Fig. 4. Simulation structure of the proposed ESD Protection device.

그림 4. 제안하는 ESD 보호소자의 Simulation 구조

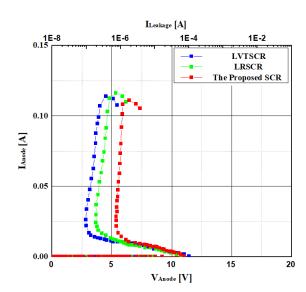

Fig. 5. Results of Simulation of LVTSCR, LRSCR and Proposed ESD Protection Device.

그림 5. LVTSCR, LRSCR 및 제안 ESD 보호장치의 시뮬레이션 결과

그림 4는 T-CAD Simulation으로 구현한 제안된 보소소자의 구조이며 N+ 확산 영역을 추가하였으며 게이 트와 P+확산영역을 연결되어있는 것을 볼 수 있다. 시뮬레이션 결과 N+ 확산 영역을 추가하여 확산 영역만큼의 전체적인 면적의 소폭 증가함을 확인하였다. 추가적인

N+ 확산 영역으로 인해 주변 확산 영역에 영향이 없다는 것을 시뮬레이션을 통해 분석하였다.

# Ⅲ. 결론

본 논문에선 기존의 ESD 보호소자보다 홀딩전압과 온저항 특성을 개선한 ESD 보호소자를 제안하였다. 새로운 구조는 기존 LRSCR에 N+확산영역을 추가하고 게이트와 P+확산영역을 연결함으로써 SCR의 Self-biasing을 통하여 농도 변화를 활용한 홀딩전류 상승을 시켰다. 제안된 구조의 검증은 T-CAD Simulation을 통해 진행되었으며 simulation을 통해 동작 및 전기적 특성을 입증하였다. 그 결과 제안된 ESD 보호소자는 11.8V의 트리거 전압 및 5.9V의 홀딩전압을 갖는 것을 확인하였다. 이는 5V 어플리케이션에 활용할 수 있으며 고신뢰성을 가질 것으로 예상된다. 구조적 변형을 통하여 높은 감내특성을 가질 것으로 보여진다.. 또한 홀딩 전류와 전압의 상승으로 인하여 Latch-up 면역특성 향상에 도움이 될 것으로 기대된다.

# References

[1] M. Ker and C. Yen, "Investigation and design of on-chip power-rail ESD clamp circuits without suffering latchup-like failure during system-level ESD test," *IEEE J. Solid-State Circuits*, vol 43, no. 11, pp.2533-2545, 2008.

DOI: 10.1109/JSSC.2008.2005451

[2] Y. Koo, K. Lee, K. Kim, and J. Kwon, "Design of SCR-based ESD protection device for power clamp using deep-submicron CMOS technology," *J. Microelectron,* vol.40, no.6, pp.1007-1012, 2009.

DOI: 10.1016/j.mejo.2009.01.001

[3] C. Lin and R. Chang, "Design of ESD protection device for K/Ka-band applications in nanoscale CMOS process," *IEEE Trans. Electron Devices*, vol. 62, no.9, pp.2824-2829, 2015.

DOI: 10.1109/TED.2015.2450225

[4] O. Semenov, H. Sarbishaei, and M. Sachdev, "ESD protection design for advanced CMOS," in Proc. SPIE, pp.123-131, 2001.

[5] B. Song, K. Do, Y. koo, "SCR-Based ESD Protection Using a Penta-Well for 5V Applications,"

IEEE Journal of the Electron Devices Society, vol.

6, pp.691-695, 2018.

DOI: 10.1109/JEDS.2018.2817636

[6] O. Quittard, Z. Mrcarica, F. Blanc, G. Notermans,

T. Smedes, and H.van Zwol, "ESD protection for

high-voltage CMOS technologies," in Proc. EOS/

ESD Symp., pp.77-86. 2006.