IJASC 23-4-1

# Ultra-High Resolution and Large Size Organic Light Emitting Diode Panels with Highly Reliable Gate Driver Circuits

Hong Jae Shin

Research Fellow, Large Display Development Group, LG Display, Republic of Korea hongjae.shin@lgdisplay.com

#### Abstract

Large-size, organic light-emitting device (OLED) panels based on highly reliable gate driver circuits integrated using InGaZnO thin film transistors (TFTs) were developed to achieve ultra-high resolution TVs. These large-size OLED panels were driven by using a novel gate driver circuit not only for displaying images but also for sensing TFT characteristics for external compensation. Regardless of the negative threshold voltage of the TFTs, the proposed gate driver circuit in OLED panels functioned precisely, resulting from a decrease in the leakage current. The falling time of the circuit is approximately 0.9  $\mu$ s, which is fast enough to drive 8K resolution OLED displays at 120 Hz. 120 Hz is most commonly used as the operating voltage because images consisting of 120 frames per second can be quickly shown on the display panel without any image sticking. The reliability tests showed that the lifetime of the proposed integrated gate driver is at least 100,000 h.

**Keywords:** Organic light emitting diodes, ultra-high resolution, large size, gate driver circuits, InGaZnO thin film transistor.

## **1. INTRODUCTION**

Recently, with rapid advances in organic light-emitting device (OLED) technologies, the fabrication of large-size televisions (TVs) based on OLED panels, which have been replaced by liquid crystal displays (LCDs) in the high-end market, has become possible [1]. OLED panels with self-luminous sub-pixels simultaneously achieve perfect black without light leakage, and have high brightness, a much wider viewing angle, and higher luminance uniformity due to advanced compensation technologies [2]. However, OLED panels because of their high price are not sufficiently competitive to replace LCDs.

In order to reduce cost of OLED panels, the cost-reduction technologies in addition to the current qualityoriented technologies are required to gain a higher market share [3]. LCDs have a long history of using costreduction technologies, including the use of integrated gate driver circuits that eliminate gate driver ICs and can have a narrow bezel size [4]. Gate driver integration is one of the key technologies for flexible displays and tiling displays, and the utilization of gate driver circuits has become necessary for OLED panels [5].

Corresponding Author: hongjae.shin@lgdisplay.com

Tel: +82-31-933-5427, Fax: +82-31-933-1140

Research Fellow, Large Display Development Group, LG Display, Korea.

Manuscript Received: october. 2, 2023 / Revised: october. 7, 2023 / Accepted: october. 12, 2023

Oxide thin-film transistors (TFTs), which are different from the a-Si TFTs commonly used for LCDs, are currently being used as backplanes for OLED display [6]. Because the mobilities of oxide TFTs are approximately 10 times higher than those of a-Si TFTs, the integrated circuits tend to be smaller. On the other hand, depletion-mode transistors often have a negative threshold voltage (Vth) at an initial stage, which will result in a leakage current and even a malfunction if the transistors are not well designed [7-8]. While the resistance of an oxide TFT to a positive bias is typically larger than that of a-Si TFT, the recovery of the Vth of the oxide TFT is generally slow, and its shift in real situations does not show a saturation behavior [9-10]. Therefore, these disadvantages should be taken into account when designing integrated circuits with oxide TFTs.

### 2. EXPERIMENTS

Active-matrix displays basically require gate ICs for the horizontal gate lines and source ICs for the vertical source lines. Because the gate signals generally have only two kinds of states, high and low states, the integration of the gate circuit is simpler than that of the source circuit for satisfying performance requirements. Because the active-matrix display should be replaced by high-mobility Si-based ICs, double-rate driving and triple-rate driving methods for LCDs have already been developed and applied to products in order to reduce the cost of the source ICs [11]. Since the OLED panels require sophisticated sensing and compensation, unlike LCDs with a simple gate driving circuit, the integration of the gate driver in the OLED panels is very difficult. In addition to the sequential drive of the gate lines, the sensing function of the Vth and the mobility are necessary for the TFTs if the OLED panels are to operate properly. Because the pixels with low Vth values are rapidly degraded due to the large current flow which results in the decrease of the lifetime of the OLED panels, the flow current of the pixels should be constant. Any gate driver circuit proposed for use in OLED panels should have dedicated blocks for sensing, and a method for driving the scan and the sense lines with different times is essential for the design of a novel gate driver circuit for use in highly efficient OLED panels.

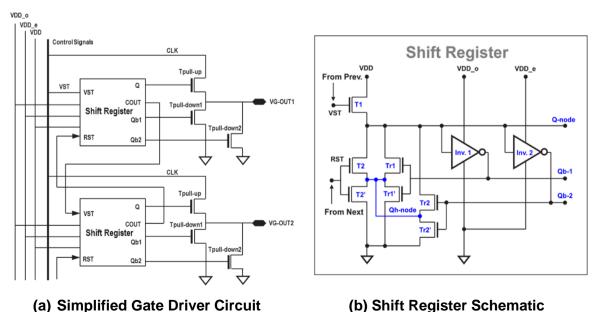

Figure 1 (a) shows a schematic diagram of the proposed integrated gate driver circuit for use in OLED panels. The dual pull-down structure is controlled by each of the two Qb-nodes.

Figure 1. The proposed integrated gate driver for OLED panels

3

Only one of the two pull-down TFTs is used to suppress the Vth shift by reducing the duty ratio to 50%. Because oxide TFTs are depletion-mode TFTs with negative Vth values, leakage currents might cause malfunction, especially in the sensing mode, which the pulse width is much larger than that of the display mode. The channel length, mobility, Vth center value, and maximum distribution of the manufactured a-IGZO TFT is 5.5  $\mu$ m, 9.5 cm<sup>2</sup>/v.s, 0.05 V, and 0.57 V, respectively. The manufactured TFT showed excellent uniformity, but negative Vth when considering the distribution characteristics. The average power consumption of the gate driver at 24 V/-6 V operation was 900 mW. Figure 1 (b) shows the leakage current can be successfully suppressed by adding the Qh-node. The Q-node is not directly connected to the low-voltage line via any TFT; the node is connected only to the Qh-node, which is automatically connected to the low-voltage line. The Qb-node and the Qh-node always have the same voltage, and the operation of the TFT is negative.

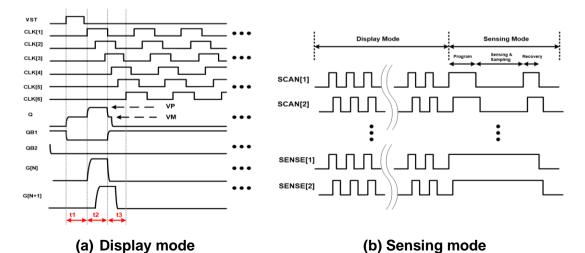

Figure 2 (a) shows the timing diagram of the proposed integrated gate driver circuit in the display mode. The timing diagram in the display mode can be described as follows: the voltage of the scan start signal (VST) increases during the period t1, charges the buffer of the TFT (Tpull-up) gate line through the SR latch, and increases the Q-node voltage. Then, Tpull-up is turned on, which resets the gate line to CLK[1], and the VST signal transfers from high to low voltage, thereby blocking the charging of the Q-node. The Q-node voltage can be maintained at the clock's high voltage level because of the existence of the capacitance of the buffer TFT. The VST signal during the period t2 transfers CLK from low to high voltages. Then, the Q-node voltage is bootstrapped, and the Tpull-up starts to charge the gate line to the high level of the CLK voltage and turns on the TFTs in the active region to charge the pixel capacitor. After the pixel charging has been completed, the selected gate line is discharged to turn off the TFTs in the active region before the (N+3) gate line is charged by the CLK[4] transition to the high level of the CLK voltage during the period t3 because the gate line, by means of the CLK transition to the low voltage level at the CLK non-overlap time between the CLK[1] and the CLK[4], is discharged. When the CLK transition to low voltage occurs in advance of the CLK[4] transition to high voltage, the gate line is discharged by the CLK[1] through the Tpull-up during the period t3 until the CLK[4] transition turns on the next gate output and then turns on the Tpull-down to turn off the Tpull-up. When the duty ratio of the clock signal starts to decrease from 50%, part of the discharging gate line can be transferred to the T<sub>pull-up</sub>.

Figure 2. Timing diagram of the proposed integrated gate driver circuit

The lower the duty ratio is, the more the gate line is discharged by using the Tpu, resulting in decreased  $T_{pull-down}$  size. Figure 2 (b) shows the timing diagram of the proposed integrated gate driver in the sensing mode. The signal width for the gate driver in the sensing mode is larger than that when it is in the display mode. The pulse signal of the gate driver does not deteriorate over a long time, which plays an important role in obtaining reliable OLED panels.

# **3. RESULTS AND DISCUSSION**

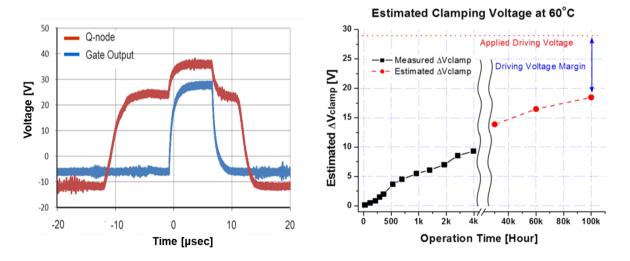

The lifetimes of the integrated driver circuits are very important if they are to replace the ICs currently used in the relatively unstable TFTs in OLED panels. While the lifetime of an OLED gradually deteriorates, that of an integrated circuit suddenly malfunctions like a light bulb. Thus, it is important not only to design a highly reliable integrated circuit but also to estimate its lifetime correctly. The deterioration of the pull-down TFTs with the fastest Vth shift rates should be correctly measured by using a nondestructive method. When the Vth of the pull-down TFTs becomes higher than the VDD voltage, the TFTs can no longer hold a gate line at low voltage, resulting in a circuit malfunction. The clamping voltage and the lowest operating voltage of the VDD line have been used to estimate the Vth of the pull-down TFTs. Because lowering the VDD voltage has an effect similar to that of a positive Vth shift of the pull-down TFTs, a voltage margin can be estimated before the malfunction of the circuit. After the reliability tests, the Vth of each TFT can be measured by using a destructive method to confirm that the Vth of the pull-down TFTs is the dominant factor. Because the Vth of the pull-down TFTs can be estimated by the lowest operating voltage of the VDD line, the Vth of the pulldown TFTs is preferable than that of the pull-up TFTs. A scalable integrated gate driver circuit with a sensing function has been successfully developed, and the driver circuit has been applied to 77-inch 8K OLED displays. The product lifetimes of the highly reliable OLED displays with a dual pull-down structure have been measured. Figure 3 (a) shows the internal voltages as functions of time for the Q-node and the gate output states. The fall time of the circuit is approximately  $0.9 \,\mu$ s, which is fast enough to drive UHD OLED displays at 120 Hz. Because the gate on-time of the 8K OLED displays is 1.9 µs, their fall times should be 1/2 to charge and discharge within the time.

## (a) Measured voltage as functions of time

Figure 3. Experimental results of the integrated gate driver

Figure 3 (b) shows the measured and the estimated clamping voltages under an accelerated life test at 60°C. The results of the reliability test show that the lifetime of the proposed integrated gate driver is at least 100,000 h. The Vth shift for the OLED display does not saturate until an operation time of 100,000 h. Because the product guarantee time of the OLED displays is 30,000 h deterioration of our device is slow enough for practical applications in OLED displays.

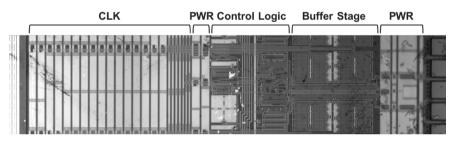

A microscopic image of the integrated gate driver on the bezel, indicative of a well-organized circuit layout, is shown in Figure 4. While the input clock signal is located on the left, the circuit for the control logic and the buffer TFT are located on the right.

Figure 5 shows a photograph of the 77-inch 8K OLED panel with an integrated gate driver circuit. OLED panels are designed as bottom-emission-type panels by using oxide TFT backplanes, and they achieve the characteristics of a narrow bezel (5.9 mm) by utilizing an integrated gate driver. The performance parameters of the 77-inch OLED panels are shown in Table 1. These parameters, functionalities of the sensing and the compensation of the OLED panels, can be seen to be the same as those of OLED panels with the previously used gate ICs.

Figure 4. Microscopic image of the integrated gate driver on the bezel of 77-inch 8K OLED display panel

Figure 5. The 77-inch 8K OLED panel with the proposed gate driver integrated using IGZO TFTs

| Item                   | Content         | Unit |

|------------------------|-----------------|------|

| Panel size             | 77              | inch |

| Resolution             | 7680x4320       | -    |

| Frame rate             | 120             | Hz   |

| Bezel Size             | 5.9             | mm   |

| Brightness (3/25/100%) | 2,000/650/250   | nit  |

| Contrast ratio         | > 1,000,000 : 1 | -    |

| Color Gamut (DCI)      | 99              | %-   |

### **4. CONCLUSION**

We presented the ultra-high resolution and large size organic light emitting diode panels with highly reliable gate driver circuits using InGaZnO thin film transistors. An integrated gate driver circuit for use in large-size OLED displays with sensing functions and scalability was developed to achieve ultra-high resolution OLED displays. The lifetime of the proposed integrated gate driver is at least 100,000 hours. The designed gate drive circuit precisely operated in the OLED panels, regardless of the negative threshold voltage of the TFTs. The falling time of the circuit is approximately 0.9 µs, which is fast enough to drive 8K OLED displays at 120 Hz. These results indicate that the gate driver circuit integrated by using InGaZnO thin film transistors holds promise for application in large-size 8K OLED display. Thus, the present observations provide good motivation for envisioning the use of UHD large-size OLEDs with highly reliable gate driver circuits in ultra-high resolution and large size televisions.

#### REFERENCES

- H. J. Shin and T. W. Kim, "Ultra-high-image-density large-size organic light-emitting devices based on In-Ga-Zn-O thin-film transistors with a coplanar structure," *Opt. Express*, vol. 26, no. 13, pp. 16812-16819, July 2018. DOI: https://doi.org/10.1364/OE.26.016805

- Y. H. Jang, "Instability of Shift Register Circuits Using Hydrogenated Amorphous Si TFTs," Jpn. J. Appl. Phys., vol. 45, pp. 6806-6811, Sep. 2006.

DOI: https://doi.org/10.1143/JJAP.45.6806

- [3] J. M. Lee, I. T. Cho, J. H. Lee, and H. I. Kwon, "Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors," *Appl. Phys. Lett.*, vol. 93, no. 9, pp. 093 504-1-093 504-3, Sep. 2008.

DOI: https://doi.org/10.1063/1.2977865

- [4] G. W. Chang, T. C. Chang, J. C. Jhu, T. M. Tsai, K. C. Chang, Y. E. Syu, Y. H. Tai, F. Y. Jian, and Y. C. Hung, "Temperature-Dependent Instability of Bias Stress in InGaZnO Thin-Film Transistors," *IEEE Trans. Electron Devices*, vol. 61, no. 6, pp. 2119-2124, Jun. 2014. DOI: https://doi.org/10.1109/TED.2014.2319105

- [5] L. R. Zhang, C. Y. Huang, G. M. Li, L. Zhou, W. J. Wu, M. Xu, L. Wang, H. L. Ning, R. H. Yao, and J. B. Peng, "A low-power high-stability flexible scan driver integrated by IZO TFTs," *IEEE Trans. Electron Devices*, vol. 63, no. 4, pp. 1779-1782, Apr. 2016. DOI: https://doi.org/10.1109/TED.2016.2529656

- [6] J. W. Choi, J. I. Kim, S. H. Kim, and J. Jang, "Highly reliable amorphous silicon gate driver using stable centeroffset thin-film transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 9, pp. 2330-2334, Sep. 2010. DOI: https://doi.org/10.1109/TED.2010.2054453

- [7] H. Lebrun, N. Szydlo, and E. Bidal, "Threshold-voltage Drift of Amorphous Silicon TFTs in Integrated Drivers for

Active Matrix LCDs," J. SID, vol. 11, no. 3, pp. 539-542, Sep. 2003. DOI: https://doi.org/10.1889/1.1825683

[8] C. L. Lin, P. S. Chen, M. Y. Deng, C. E. Wu, W. C. Chiu, and Y. S. Lin, "UHD AMOLED Driving Scheme of Compensation Pixel and Gate Driver Circuits Achieving High-Speed Operation," *J. Electron Dev. Soc.*, vol. 6, no. 1, pp. 26-33, Oct. 2018.

DOI: https://doi.org/10.1109/JEDS.2017.2763601

- M. M, M. H. Choi, J. W. Choi, and J. Jang, "Transparent flexible circuits based on amorphous -indium-gallium-zincoxide thin-film transistors," *IEEE Electron Device Lett.*, vol. 32, no. 2, pp. 170-172, Feb. 2011. DOI: https://doi.org/10.1109/LED.2010.2093504

- [10] J. W. Cha and Y. C. Park, "A Study of 0.5-bit Resolution for True-Time Delay of Phased-Array Antenna System," *International Journal of Advanced Smart Convergence*, vol. 11, no. 4, pp. 96-103, December 2022. DOI: http://dx.doi.org/10.7236/IJASC.2022.11.4.96

- [11] H. J. Shin and T. W. Kim, "Enhancement of the Luminance Uniformity in Large-Size Organic Light-Emitting Devices Based on In–Ga–Zn–O Thin-Film Transistors by Using a New Compensation Method," *IEEE J. Electron Devices Society*, vol. 7, no. 1, pp. 557-560, May 2019. DOI: https://doi.org/10.1109/JEDS.2019.2914497