J. Korean Inst. Electr. Electron. Mater. Eng. Vol. 35, No. 3, pp. 255-263 May 2022 DOI: https://doi.org/10.4313/JKEM.2022.35.3.7 ISSN 1226-7945(Print), 2288-3258(Online)

# 가우스 함수의 파라미터에 따른 비대칭형 무접합 이중 게이트 MOSFET의 문턱전압 이하 스윙 분석

## 정학기⑩

군산대학교 전자공학과

## Analysis on Subthreshold Swing of Asymmetric Junctionless Double Gate MOSFET for Parameters for Gaussian Function

### Hakkee Jung

Department of Electronic Engineering, Kunsan National University, Gunsan 54150, Korea

(Received December 13, 2021; Revised January 5, 2022; Accepted January 8, 2022)

**Abstract:** The subthreshold swing (SS) of an asymmetric junctionless double gate (AJLDG) MOSFET is analyzed by the use of Gaussian function. In the asymmetric structure, the thickness of the top/bottom oxide film and the flat-band voltages of top gate ( $V_{\rm fbf}$ ) and bottom gate ( $V_{\rm fbb}$ ) could be made differently, so the change in the SS for these factors is analyzed with the projected range and standard projected deviation which are parameters for the Gaussian function. An analytical subthreshold swing model is presented from the Poisson's equation, and it is shown that this model is in a good agreement with the numerical model. As a result, the SS changes linearly according to the geometric mean of the top and bottom oxide film thicknesses, and if the projected range is less than half of the silicon thickness, the SS decreases as the top gate oxide film is smaller. Conversely, if the projected range is bigger than a half of the silicon thickness, the SS decreases as the bottom gate oxide film is smaller. In addition, the SS decreases as  $V_{\rm fbb}$ - $V_{\rm fbf}$  increases when the projected range is near the top gate, and the SS decreases as  $V_{\rm fbb}$ - $V_{\rm fbf}$  decreases when the projected range is near the bottom gate. It is necessary that one should pay attention to the selection of the top/bottom oxide thickness and the gate metal in order to reduce the SS when designing an AJLDG MOSFET.

**Keywords:** Asymmetric, Double gate, Junctionless, Subthreshold swing, Oxide thickness, Projected range, Standard projected deviation

## 1. 서 론

소자의 크기가 감소하면서 트랜지스터의 스케일링은 매우 중요한 요소가 되었다 [1-4]. 채널 크기 감소와 함께 가

☑ Hakkee Jung; hkjung@kunsan.ac.kr

Copyright ©2022 KIEEME. All rights reserved.

This is an Open-Access article distributed under the terms of the Creative Commons. Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

장 중요한 소자 파라미터는 소스/드레인 및 채널 내 도핑이다 [5-7]. 채널 도핑에 주로 이용되고 있는 이온주입법에서는 도핑 분포가 가우스 함수를 따르고 있다 [8-10]. 가우스 함수는 최대 도핑농도와 함께 투사범위(projected range)와 표준투사편차(standard projected deviation)의 두 가지 파라미터에 의하여 분포함수의 형태가 결정된다. 그러나 많은 연구자들이 채널의 전위 분포를 구하기 위하여 이용하고 있는 포아송 방정식을 풀 때, 계산의 간단함을 위하여 채널 내 도핑 분포는 일정하다는 가정하에 전위

분포를 구하고 있다 [11-13]. 본 논문에서는 채널의 깊이 방향인 수직 가우스 함수를 이용한 포아송 방정식의 해를 구하여 채널 내 전위 분포를 구하고자 한다. 대상 트랜지스 터는 비대칭 무접합 이중 게이트(asymmetric junctionless double gate, AJLDG) MOSFET를 사용할 것이다 [14-16]. 상하단 비대칭 구조는 상하단의 게이트 산화막 구조를 달 리 제작할 수 있어 단채널 효과를 제어할 수 있는 요소가 증가하므로 대칭형보다 단채널 효과를 효율적으로 제어할 수 있을 것이다. 또한 본 논문에서는 무접합 구조의 트랜지 스터를 사용할 것이다. 이 구조는 소스/드레인과 채널 간 동일한 도핑 형태와 도핑 농도를 사용함으로써 접합형 (junction-based) MOSFET의 크기 감소로 발생하는 소 스/드레인과 채널 간 접합 형성의 난해함을 해결하는 구조 로써 널리 연구되고 있다 [17-19]. 전술한 바와 같이 비대 칭 구조의 경우 상하단 산화막 두께, 산화막의 종류 및 게 이트 금속을 달리 사용할 수 있어 단채널 효과를 효과적으 로 제어할 수 있는 요소가 증가한다. 본 논문에서는 단채널 효과 중, 문턱전압 이하 스윙(subthreshold swing, SS)의 변화를 채널 도핑 분포함수인 가우스 함수의 파라미터에 따라 분석할 것이다. 가우스 함수는 최대 도핑농도가 채널 두께의 중간이 아니라면 채널 도핑은 비대칭 분포함수이 다. 그러므로 비대칭 이중 게이트 MOSFET의 상하단 산화 막 두께 및 게이트 금속의 일함수 등에 따라 채널 내 전위 분포는 영향을 받을 것이며 이로 인하여 캐리어의 전송특 성도 변화할 것이다. 이러한 변화는 문턱전압 이하 스윙에 영향을 미칠 것이므로 본 논문에서는 상기 파라미터(상하 단 산화막 두께, 평탄전압, 투사범위, 표준투사편차)에 따 른 문턱전압 이하 스윙의 변화를 관찰할 것이다.

Singh 등과 Hashemi 등은 무접합 이중 게이트 FET의 문턱전압을 해석하기 위하여 가우스 함수 적분의 난해함 을 피할 수 있도록 유사 가우스도핑 분포(Gaussian-like doping profile)를 이용하였다 [20,21]. 또한 Kumari 등 은 가우스 함수를 이용하여 채널 길이가 30 nm 이상의 트 랜지스터에 대하여 문턱전압 이하 특성을 분석하였다 [22]. Tiwari 등은 접합형 이중 게이트 MOSFET의 채널에 가우 스 함수를 적용하여 문턱전압을 해석하였다 [23]. 이에 본 연구에서는 무접합 이중 게이트 MOSFET에 적용할 수 있 도록 Tiwari의 채널 내 전위 분포모델을 수정하여 채널 길 이가 20 nm일 경우에도 이용할 수 있는 문턱전압 이하 스 윙모델을 가우스 함수를 이용하여 제시하고자 한다. 가우 스 함수는 투사범위와 표준투사편차 등에 따라 분포함수 의 모양이 결정된다. 그러므로 두 변수에 따라 채널 내 전 위 분포함수가 변화할 것이며 이는 문턱전압 이하 스윙에 직접적으로 영향을 미칠 것이다. 이에 본 논문에서는 두 변

수가 문턱전압 이하 스윙에 미치는 영향을 고찰할 것이며 상하단 산화막 두께 및 평탄전압에 따른 문턱전압 이하 스 윙의 변화를 관찰할 것이다.

## 2. 가우스 함수를 이용한 AJLDG MOSFET의 문턱전압 이하 스윙 모델

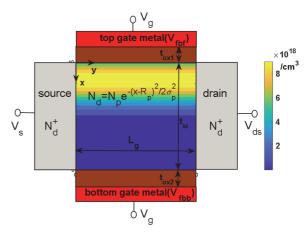

그림 1에 본 논문에서 사용한 비대칭 무접합 이중 게이 트 MOSFET의 개략도를 도시하였다. 소스와 드레인은  $N^{+}$ 로 고농도 도핑하였으며 채널은 소스/드레인과 채널 간 무접합을 위하여 n형으로 고도핑하였다. 이때 최대 도 핑농도  $N_0=10^{19}$  cm<sup>-3</sup>인 가우스 함수로 도핑하였으며 투사 범위  $R_p$ 와 표준투사편차  $\sigma_p$ 를 변화시키면서 문턱전압 이 하 스윙의 변화를 관찰하였다. 채널 길이는  $L_{g}$ , 실리콘 두 께는  $t_{\rm si}$ 이며  $t_{\rm ox1}$ 은 상단 게이트산화막 두께,  $t_{\rm ox2}$ 는 하단 게 이트산화막 두께를 표시한다. 본 논문에서는 채널 길이 20 nm, 실리콘 두께 10 nm로 고정하였을 경우, 상하단 산화 막 두께가 1~3 nm로 변화할 경우 문턱전압 이하 스윙의 변화를 관찰할 것이다. 채널 영역 도핑은 채널의 두께 방향 으로 가우스 도핑 분포를 보이고 있으며 상단 게이트 금속 과 하단 게이트 금속은 달리 사용할 수 있도록 설계하였다. 즉 게이트 금속이 변화하면 결국 일함수가 변화하여 평탄 전압이 변화할 것이다. 본 논문에서는 상하단의 게이트 금 속에 대한 평탄전압이 0.5~1.0 V 사이에서 변화할 때 문턱 전압 이하 스윙의 변화를 관찰할 것이다.

먼저 채널 내 전위 분포를 구하기 위하여 다음과 같은 포 아송 방정식과 경계조건을 이용하였다.

**Fig. 1.** Schematic cross-sectional diagram of the asymmetric junctionless double gate (AJLDG) MOSFET with Gaussian doping profile.

$$\frac{\partial \phi^{2}(x, y)}{\partial x^{2}} + \frac{\partial \phi^{2}(x, y)}{\partial y^{2}} = -\frac{qN_{p}}{\varepsilon_{sl}} \exp \left[ -\left(\frac{x - R_{p}}{\sqrt{2}\sigma_{p}}\right)^{2} \right]$$

$$\phi(x, y)|_{x=0} = \phi_{s}(y)$$

$$\frac{\varepsilon_{ss}}{t_{ss1}} \left( V_{g} - V_{fby} - \phi(0, y) \right) = -\varepsilon_{sl} \frac{\partial \phi}{\partial x}|_{x=0}$$

$$\frac{\varepsilon_{ss}}{t_{ss2}} \left( V_{g} - V_{fbb} - \phi(t_{sl}, y) \right) = \varepsilon_{sl} \frac{\partial \phi}{\partial x}|_{x=t_{sl}}$$

$$\phi(0, 0) = V_{hl}$$

$$\phi(0, L_{g}) = V_{hl} + V_{dl}$$

(1)

여기서  $\varepsilon_{si}$ 와  $\varepsilon_{ox}$ 는 각각 실리콘과 게이트 산화막의 유전율로서 게이트 산화막은 SiO $_2$ 를 사용하였다.  $V_{sb}$ 는 게이트전압,  $V_{tbs}$ 와  $V_{tbb}$ 는 각각 상단과 하단 게이트 금속에 따라변화하는 평탄전압,  $V_{sb}$ 는 드레인전압,  $V_{bb}$ 는 빌트인 전압(built-in potential)이다. Ding 등의 전개 방법을 이용하여 마지막 두 개의 경계조건을 이용하면 전위 분포는 다음과 같은 급수 형태로 표현할 수 있다 [24].

$$\phi(x, y) = V_s + \frac{V_d}{L_g} y + \sum_{n=1}^{\infty} A_n(x) \sin \frac{n\pi y}{L_g}$$

(2)

여기서 n은 정수이며  $A_n(x)$ 는 다음과 같은 식에서 구할 수 있다.

$$\frac{d^{2}A_{n}(x)}{dx^{2}} - k_{n}^{2}A_{n}(x) = G_{n}N_{p} \exp\left\{-\left(\frac{x - R_{p}}{\sqrt{2}\sigma_{p}}\right)^{2}\right\} = r(x)$$

$$G_{n} = \frac{2q\left[1 - (-1)^{n}\right]}{n\pi\varepsilon_{n}}$$

(3)

식 (3)의 비동차(nonhomogeneous) 미분방정식의 해는 다음과 같은 동차(homogeneous) 미분방정식의 해  $A_h(x)$ 와 특이해  $A_o(x)$ 의 합으로 표현할 수 있다.

$$A_{n}(x) = A_{n}(x) + A_{n}(x) \tag{4}$$

이때 동차 미분방정식의 해는

$$A_{h}(x) = C_{n}e^{k_{n}x} + D_{n}e^{-k_{n}x}$$

(5)

와 같으며 이를 이용하면

$$\begin{split} &A_{p}(x) = \frac{e^{k,x}}{2k_{s}} \int e^{-k,x} r(x) dx - \frac{e^{-k,x}}{2k_{s}} \int e^{k,x} r(x) dx \\ &= \sqrt{\frac{\pi}{2}} \frac{G_{s} N_{p} \sigma_{p}}{2k_{s}} \frac{e^{\frac{(k\sigma_{s})^{2}}{2}}}{e^{2}} \left[ e^{k_{s}(x-R_{p})} erf\left(\frac{x-R_{p}}{\sqrt{2}\sigma_{p}} + \frac{k_{s}\sigma_{p}}{\sqrt{2}}\right) - e^{-k_{s}(x-R_{p})} erf\left(\frac{x-R_{p}}{\sqrt{2}\sigma_{p}} - \frac{k_{s}\sigma_{p}}{\sqrt{2}}\right) \right] \end{split}$$

와 같이 구할 수 있다. 식 (5)의 동차 미분방정식 해의 계수  $C_n$ 과  $D_n$ 은 경계조건의 처음 두 개의 조건과 프리에 급수 (Fourier series)의 계수관계를 이용하여 다음과 같이 구할 수 있다.

$$C_{n} = \frac{a_{21}I_{1} - a_{12}I_{2}}{a_{11}a_{22} - a_{12}a_{21}}, D_{n} = \frac{a_{21}I_{1} - a_{11}I_{2}}{a_{12}a_{21} - a_{11}a_{22}}$$

$$a_{11} = 1 - \frac{\varepsilon_{n}k_{n}}{C_{mt}}, a_{12} = 1 + \frac{\varepsilon_{n}k_{n}}{C_{m1}}, a_{21} = e^{k_{x}I_{n}} + \frac{\varepsilon_{n}k_{n}}{C_{m2}}, a_{22} = e^{-k_{x}I_{n}} - \frac{\varepsilon_{n}k_{n}e^{-k_{x}I_{n}}}{C_{m2}}$$

$$I_{1} = \frac{\varepsilon_{n}}{C_{m1}} \frac{dA_{p}(\mathbf{x})}{d\mathbf{x}} \Big|_{\mathbf{x}=0} - A_{p}(0) - \frac{2}{n\pi} \Big[ \Big( V_{s} - V_{gy} + V_{fyf} \Big) \{1 - (-1)^{n}\} - V_{ab}(-1)^{n} \Big]$$

$$I_{2} = -\frac{\varepsilon_{n}}{C_{n}} \frac{dA_{p}(\mathbf{x})}{d\mathbf{x}} \Big|_{\mathbf{x}=0} - A_{p}(t_{n}) - \frac{2}{n\pi} \Big[ \Big( V_{s} - V_{gsb} + V_{fsb} \Big) \{1 - (-1)^{n}\} - V_{ab}(-1)^{n} \Big]$$

이와 같이 구한 전위 분포와 문턱전압 이하 스윙의 정의를 이용하여

$$SS = \ln(10) \left(\frac{kT}{q}\right) \left[\frac{\partial \phi(x_{eff}, y_{min})}{\partial V_{a}}\right]^{-1}$$

(8)

와 같이 문턱전압 이하 스윙을 구할 수 있다. 여기서  $X_{eff}$ 는 전도 중심이며  $Y_{min}$ 은 전도 중심에서 가장 낮은 전위 분포를 보이는 V축 값을 나타낸다 [25]. 전위 분포는

$$\phi(x, y) = V_s + \frac{V_d}{L_o} y + \sum_{n=1}^{\infty} (A_h(x) + A_p(x)) \sin \frac{n\pi y}{L_o}$$

와 같으며 이때  $\frac{\partial A_p}{\partial V_g} = 0$  이므로 결국

$$\frac{\partial \phi}{\partial V_{g}} = \sum_{n=1}^{\infty} \frac{\partial A_{h}(x)}{\partial V_{g}} \sin\left(\frac{n\pi y}{L_{g}}\right)$$

와 같다. 여기서  $V_g$ 에 대한  $A_h$ 의 미분은

$$\begin{split} &\frac{\partial A_{h}(x)}{\partial V_{gsf}} = e^{k_{x}x} \frac{\partial C_{n}}{\partial V_{g}} + e^{-k_{x}x} \frac{\partial D_{n}}{\partial V_{g}} \\ &= e^{k_{x}x} \left( \frac{a_{22} - a_{12}}{a_{11}a_{22} - a_{12}a_{21}} \frac{\partial I_{1}}{\partial V_{g}} \right) - e^{-k_{x}x} \left( \frac{a_{21} - a_{11}}{a_{11}a_{22} - a_{12}a_{21}} \frac{\partial I_{1}}{\partial V_{g}} \right) \\ &= \frac{2}{n\pi} \left[ 1 - (-1)^{n} \right] \frac{1}{a_{11}a_{22} - a_{12}a_{21}} \left[ a_{22}e^{k_{x}x} - a_{21}e^{-k_{x}x} \right] \end{split}$$

와 같이 구할 수 있다. 결국 최종적으로 SS는

$$SS = 2.3V_{t} \left[ \sum_{n=1}^{\infty} \frac{2}{n\pi} \left[ 1 - (-1)^{n} \right] \frac{1}{a_{11}a_{22} - a_{12}a_{21}} \left[ a_{22}e^{k_{x_{eff}}} - a_{21}e^{-k_{x_{eff}}} \right] \sin\left(\frac{n\pi y_{\min}}{L_{g}}\right) \right]^{-1}$$

(9)

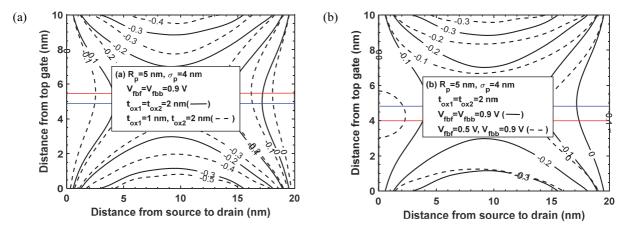

Fig. 2. Contours of potential distribution and conduction paths (a) when the top and bottom gate oxide thicknesses are changed from  $t_{\text{ox1}}$ =2 nm to  $t_{\text{ox1}}$ =1 nm and  $t_{\text{ox2}}$ =2 nm, and (b) when the top and bottom flat-band voltages are changed from  $V_{\text{fb}}$ = $V_{\text{fb}}$ =0.9 V to  $V_{\text{fb}}$ =0.5 V and  $V_{\text{fb}}$ =0.9 V (The blue line denotes the conduction path in the case of the symmetric structure, and the red line for the asymmetric structure).

이다.

먼저 전송특성에 가장 큰 영향을 미치는 채널 내 전위 분 포의 상하단 산화막 두께 및 평탄전압에 따른 변화를 그림 2에 도시하였다. 최대 도핑농도의 위치를 나타내는 투사범 위 값은 실리콘 두께의 중간값 즉  $R_p = t_{si}/2$ 을 사용하였으며 표준투사편차는 4 nm 값을 사용하였다. 그림 2(a)와 (b)에 서 파란 실선은 상하단 산화막 및 평탄전압이 동일하여 대 칭인 경우의 전도 중심을 표시하고 있으며 정확히 실리콘 두께의 1/2 값에서 전도 중심이 나타나고 있었다. 그림 2(a) 에서 적색 실선은 상단 게이트 산화막 두께가 2 nm에서 1 nm로 작아졌을 경우 전도 중심의 변화를 나타내고 있다. 그림 2(a)의 적색 실선에서 알 수 있듯이 상단의 산화막 두 께가 감소하면 전도 중심은 하단 게이트 단자 방향으로 이 동하는 것을 알 수 있다. 이러한 전도 중심의 이동은 결국 문턱전압 이하 스윙에 영향을 미칠 것이다. 전도 중심의 변 화는 상하단 게이트 산화막 두께 변화뿐만 아니라 게이트 금속의 일함수에 따라서도 변화하고 있다는 것을 그림 2(b) 에서도 관찰할 수 있다. 그림 2(b)에서 적색 실선은 상단의 평탄전압이 0.9 V에서 0.5 V로 변화하였을 경우 전도 중 심을 나타내고 있다. 그림 2(b)에서 알 수 있듯이 평탄전압 이 상하단 다를 경우도 전도 중심은 변화하고 있었다.

## 3. AJLDG MOSFET의 문턱전압 이하 스윙 분석

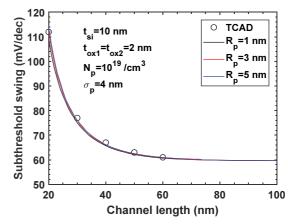

먼저 본 논문에서 제시한 식 (8)의 타당성을 검증하기 위하여 타 논문의 TCAD 결과 [26]와 그림 3에서 비교하였다. 채널 길이는 20 nm 이상의 값을 사용하였으며 실리콘 두

께는 10 nm, 게이트 산화막 두께는 2 nm, 최대 도핑농도는 10<sup>19</sup> cm<sup>-3</sup>의 경우에 대하여 비교한 결과 본 논문에서 고찰하고 있는 투사범위와 표준투사편차의 범위 내의 특정한 값을 사용하면 충분히 일정한 도핑농도를 사용한 경우와 일치시킬 수 있다는 것을 알 수 있다. 그러므로 본 논문에서 제시한 식 (8)의 모델은 타당하다고 사료된다. 그림 3의 결과를 관찰해 보면 상하단 대칭구조에서는 투사범위값의 변화에 대하여 문턱전압 이하 스윙의 값은 거의 동일한 결과를 유도하였다. 그러나 그림 2에서 설명한 바와 같이 상하단 게이트 구조가 비대칭일 경우 문턱전압 이하 스윙은 산화막 두께 및 평탄전압에 따라 변화할 것이다.

먼저 상하단 게이트 산화막 두께가 1 nm에서 3 nm까지 변화할 경우 투사범위가 5 nm와 표준투사편차가 3 nm

**Fig. 3.** Comparison of subthreshold swings of this model with the results of TCAD with the projected range as a parameter.

3

$R_{\rm p}$ =5 nm,  $\sigma_{\rm p}$ =3 nm

$R_p=1 \text{ nm}, \sigma_p=3 \text{ nm}$  $R_{p}$ =5 nm,  $\sigma_{p}$ =1 nm

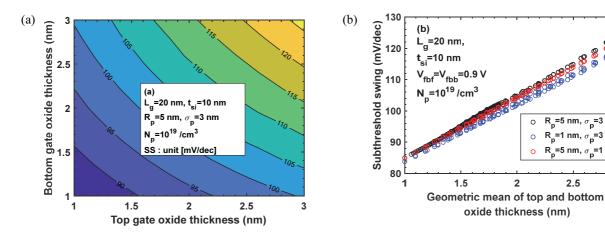

Fig. 4. (a) Contours of the subthreshold swing for the top and bottom gate oxide thickness under the given conditions and (b) subthreshold swings for the geometric mean of the top and bottom oxide thickness with the projected range and standard projected deviation as parameters.

에서 문턱전압 이하 스윙의 등고선 선도를 그림 4(a)에 도 시하였다. 상하단 산화막 두께가 증가하면 문턱전압 이하 스윙도 증가하며 거의 비례적으로 증가하고 있다는 것을 알 수 있었다. 이러한 형태의 등고선 관계는 이미 발표한 논문 [27]에서도 언급한 바와 같이 상하단 게이트 산화막 두께의 기하평균  $\sqrt{t_{ox1}t_{ox2}}$ 에 문턱전압 이하 스윙이 선형 적으로 비례하고 있다는 것을 알 수 있다. 이와 같은 관계 를 그림 4(b)에 도시하였다.

그림 4(b)는 상하단 산화막 두께의 기하평균에 문턱전압 이하 스윙이 선형적으로 비례한다는 것을 보여주고 있다. 그러나 비례상수는 투사범위와 표준투사편차에 따라 변화 하고 있었다. 즉 투사범위와 표준투사편차의 변화에 따라 상하단 산화막 두께의 기하평균에 대한 문턱전압 이하 스 윙의 변화율이 다르다는 것을 알 수 있다.

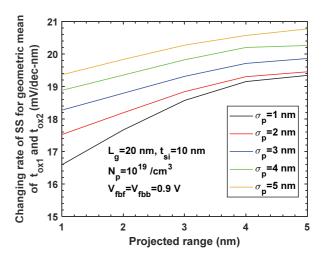

상하단 게이트 산화막 두께의 기하평균뿐만 아니라 투 사범위와 표준투사편차의 변화만으로도 문턱전압 이하 스 윙에 영향을 미치고 있다는 것을 알 수 있다. 그림 5에 상 하단 산화막 두께의 기하평균에 대한 문턱전압 이하 스윙 의 변화율 $(\Delta SS/\Delta\sqrt{t_{ox1}t_{ox2}})$ 을 투사범위에 대하여 도시하였 다. 이때 파라미터는 표준투사편차를 사용하였다. 그림 5 에서 알 수 있듯이 투사범위가 증가할수록 그리고 표준투 사편차가 증가할수록 변화율  $\Delta SS/\Delta\sqrt{t_{ox1}t_{ox2}}$ 은 증가하고 있었다. 즉 두 파라미터가 증가할수록 산화막 두께에 대하 여 문턱전압 이하 스윙은 더욱 민감하게 변화한다는 것을 알 수 있다. 그러나 투사범위가 증가할수록 변화율은 포화 되고 있었다. 또한 투사범위가 작을 경우 표준투사편차에 대한 변화율은 증가하였으며, 투사범위가 클 경우 표준투 사편차에 대한 변화율은 감소하였다. 이러한 특성은 결국 채널 내 도핑된 도즈량에 따라 결정될 것이다.

Fig. 5. The changing rate of subthreshold swing for the geometric mean of top and bottom gate oxide thickness for the projected range with the standard projected deviation as a parameter.

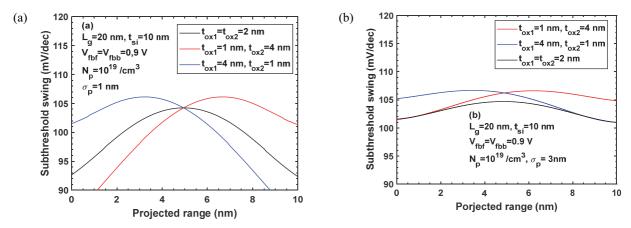

그림 6에 투사범위의 변화에 대한 문턱전압 이하 스윙의 변화를 상하단 산화막 두께 변화에 대하여 도시하였다. 그림 6(a)는 표준투사편차가 1 nm인 경우로써 상하단 산화막의 기하평균이 모두 2 nm인 경우를 비교하였다. 상하단 산화막 두께가 2 nm로 동일할 경우, 투사범위가 실리콘 두께의 1/2일 때 최대 문턱전압 이하 스윙 값을 보이고 있었다. 투사범위가 증가 또는 감소하면 문턱전압 이하 스윙은 감소하였으며 거의 대칭적인 관계를 보이면서 감소하였다. 즉,  $R_p$ =3 nm인 경우의 문턱전압 이하 스윙값과  $R_p=7$  nm인 경우의 문턱전압 이하 스윙 값은 거의 동일하였다. 그러나 상하단 산화막 두께의 기하 평균값은 동일하나 비대칭 구조를 가진 경우 다른

Fig. 6. Subthreshold swings for the projected range with the top and bottom gate oxide thicknesses as parameters in the case of (a)  $\sigma_p = 1 \, nm$  and (b)  $\sigma_p = 3 \, nm$ .

분포함수를 보이고 있었다.  $t_{ox1} > t_{ox2}$ 인 경우 투사범위가 실리콘 두께의 1/2보다 클 때, 문턱전압 이하 스윙값의 감소가 더욱 심하게 발생하였으며 반대로  $t_{ox1} < t_{ox2}$ 인 경우 투사범위가 실리콘 두께의 1/2보다 작을 때, 문턱전압 이하 스윙값의 감소가 더욱 심하게 발생하였다. 그러나  $R_p$ =5 nm인 경우, 상하단 산화막 두께의 기하평균이 동일하다면 문턱전압 이하 스윙값도 동일하다는 것을 알 수 있었다. 그림 6(b)에 표준투사편차가 3 nm인 경우, 문턱전압 이하 스윙의 투사범위에 대한 변화를 도시하였다. 그림 6(a)와 (b)를 비교해 보면, 표준투사편차가 증가하면 문턱전압 이하 스윙값이 투사범위의 변화에 대하여 크게 변화하지 않고 있다는 것을 관찰할 수 있다. 가우스 함수의 특성상, 표준투사편차가 증가할수록 채널 내 도핑은 일정한 분포와 동일해지기 때문에 이러한 현상이 발생할 것이다. 그림 6(a)와 (b)에서 알 수 있듯이 표준투사편차가 감소하면 투사범위에 따라 문턱전압 이하 스윙을 더욱 감소시킬 수 있을 것이다. 또한 그림 6(a)의  $\sigma_n = 1$  nm 경우와 달리 그림 6(b)의  $\sigma_p$  = 3 nm 경우는  $R_p$ =5 nm일 때 동일한 문턱전압 이하 스윙값을 나타내고 있지 않았다. 그러나 그 차이는 1~2 mV/dec 정도이므로 상하단 산화막 두께의 기하평균에 문턱전압 이하 스윙이 선형적으로 비례한다는 결과에는 큰 차이가 없을 것이다. 그보다  $R_p$ 가 작거나 큰 영역에서 상하단 산화막 두께의 기하평균에 문턱전압 이하 스윙의 선형성이 떨어지는 것을 그림 6(a)와 (b)뿐만 아니라 그림 4(b)에서도 관찰할 수 있다.

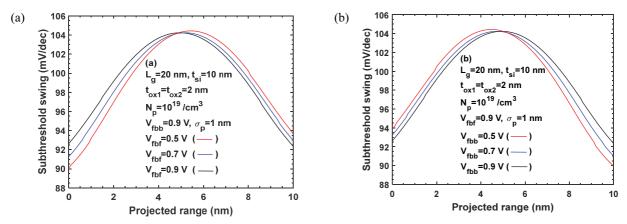

상하단 게이트 산화막 두께에 대한 영향뿐만 아니라 상하단 게이트 금속의 일함수에 따라 변화하는 상하단 평탄 전압에 대한 문턱전압 이하 스윙의 변화를 관찰하기 위하여 상하단 게이트 산화막 두께가 2 nm이고  $\sigma_p = 1 \text{ nm}$ 일

때 투사범위에 대한 문턱전압 이하 스윙의 변화를 상하단 평탄전압을 파라미터로 그림 7(a)와 (b)에 도시하였다. 상 하단 평탄전압이 문턱전압 이하 스윙에 미치는 영향을 관 찰하기 위하여 상하단 게이트 산화막 두께는 동일하게 설 정하였다. 그림 7(a)에서 하단 평탄전압을 0.9 V로 고정하 고 상단 평탄전압을 0.3~0.9 V 사이에서 변화할 때 문턱전 압 이하 스윙의 변화를 관찰해 보면, 그림 6(a)에서 언급한 바와 같이  $R_p$ =5 nm에서는  $V_{\rm fbf}$ 의 변화와 관계없이 일정한 문턱전압 이하 스윙값을 나타내고 있었다. 그러나  $R_p < t_{si}/2$ 인 영역에서는  $V_{fbf}$ 가 감소할수록 문턱전압 이하 스윙은 감 소하였으며  $R_p > t_{si}/2$ 인 영역에서는  $V_{flot}$ 가 감소할수록 문턱 전압 이하 스윙은 증가하고 있다는 것을 관찰할 수 있다. 하단 평탄전압의 변화에 대한 문턱전압 이하 스윙의 변화 를 관찰하기 위하여 그림 7(b)에 상단 평탄전압을 0.9 V로 고정하고 하단 평탄전압을 0.3~0.9 V 사이에서 변화할 때 문턱전압 이하 스윙의 변화를 도시하였다. 그림 7(b)에서 알 수 있듯이  $R_p < t_{si}/2$ 인 영역에서는  $V_{fbb}$ 가 증가할수록 문 턱전압 이하 스윙은 감소하였으며  $R_p > t_{si}/2$ 인 영역에서는 V<sub>fbb</sub>가 감소할수록 문턱전압 이하 스윙은 감소하고 있다는 것을 관찰할 수 있다.

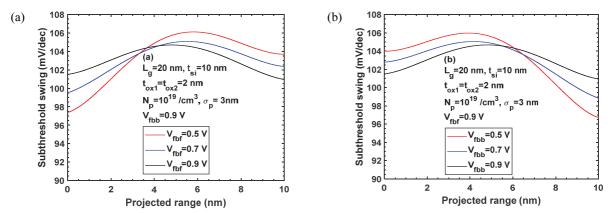

표준투사편차의 변화가 평탄전압의 변화에 미치는 영향을 관찰하기 위하여 그림 8에  $\sigma_p$ = 3 nm일 경우 문턱전압이하 스윙의 변화를 그림 7과 같은 조건에서 도시하였다. 그림 7과 8을 비교해 보면 평탄전압과 투사범위에 대한 변화경향은 표준투사편차에 관계없이 동일하다는 것을 알수 있으나 표준투사편차가 증가할수록 평탄전압의 변화에 대한 문턱전압 이하 스윙의 변화가 증가한다는 것을 관찰할수 있다. 그러므로 표준투사편차가 증가할수록 평탄전압의 설정에 주의할 필요가 있을 것이다. 그림 7과 같이 표준

Fig. 7. Subthreshold swings for the projected range with (a) top gate flat-band voltage and (b) bottom gate flat-band voltage as a parameter in the case of  $\sigma_p = 1 \, nm$ .

**Fig. 8.** Subthreshold swings for the projected range with (a) top gate flat-band voltage and (b) bottom gate flat-band voltage as a parameter in the case of  $\sigma_p = 3 \ nm$ .

투사편차가 작을 경우, 투사범위가 채널의 중심부에 있을때 문턱전압 이하 스윙의 최댓값이 나타난다. 이는 표준투사편차가 작을 경우 도핑 분포의 폭이 좁아 최대 도핑된 채널 중심부에 대부분의 불순물이 첨가되기 때문이다. 그러나 그림 8과 같이 표준투사편차가 3 nm로 증가하면 도핑분포가 퍼져서 나타나기 때문에 문턱전압 이하 스윙의 최댓값도 평탄전압에 따라 다른 투사범위값에서 관측되고 있었다. 그림 7과 8에서 알 수 있듯이 투사범위는 상단 또는하단 게이트 금속에 가깝고 표준투사편차는 작을수록, 그리고 상단과 하단의 평탄전압의 차이가 클수록 문턱전압이하 스윙값은 작아질 수 있다는 것을 관찰하였다.

#### 4. 결 론

본 논문에서는 AJLDG MOSFET의 채널에 가우스 함수를 적용한 경우 투사범위와 표준투사편차의 변화에 따라 문턱전압 이하 스윙의 변화를 고찰하였다. 상단과 하단의 산화막 두께 및 평탄전압을 파라미터로 사용하였다. 이를 위하여 포아송방정식으로부터 유도한 전위 분포함수 모델을 이용하여 문턱전압 이하 스윙 모델을 제시하였다. 이 모델은 이차원 시뮬레이션 값과 잘 일치하였다. 채널 내 도핑이 일정하다고 가정한 경우와 같이 가우스 함수를 이용한 경우도 상하단 산화막 두께의 기하평균에 선형적으로 비례하고 있었다. 그러나 비례상수는 투사범위와 표준투사편차에 따라 변화하였으며  $R_p = \sigma_p = 1$  nm일 때 16.8 mV/dec-nm까지 변화하였다. 즉 투사범위와 표준투사편차가 클수

록 상하단 산화막 두께에 대하여 문턱전압 이하 스윙은 민감하게 변화하였다. 상단 또는 하단 평탄전압이 0.4 V 변화하였을 때, 문턱전압 이하 스윙의 변화를 투사범위와 표준투사편차에 대하여 수행한 결과,  $\sigma_p$  = 1 nm일 때  $R_p$ 에 따라 문턱전압 이하 스윙은 최대 14 mV/dec 정도 차이가 발생하였으나  $\sigma_p$  = 3 nm로 표준투사편차가 증가하면  $R_p$ 에 따른 문턱전압 이하 스윙은 약 9 mV/dec 정도 차이가 발생하는 것을 관찰하였다. 결국 가우스 함수를 갖는 AJLDG MOSFET에서 문턱전압 이하 스윙은 투사범위와 표준투사편차의 변화뿐만 아니라 상하단 산화막 두께와 평단전압의 변화에 민감하게 변화하는 것을 알 수 있었다.

#### **ORCID**

Hakkee Jung

https://orcid.org/0000-0002-2828-2957

#### REFERENCES

- [1] T. B. Hook, *Joule*, **2**, 1 (2018). [DOI: https://doi.org/10.1016/j.joule.2017.10.014]

- [2] H. H. Radamson, H. Zhu, Z. Wu, X. He, H. Lin, J. Liu, J. Xiang, Z. Kong, W. Xiang, J. Li, H. Cui, J. Gao, H. Yang, Y. Du, B. Xu, B. Li, X. Zhao, J. Yu, Y. Dong, and G. Wang, *Nanomaterials*, 10, 1555 (2020). [DOI: https://doi.org/10.3390/ nano10081555]

- [3] G. Arutchelvan, Q. Smets, D. Verreck, Z. Ahmed, A. Gaur, S. Sutar, J. Jussot, B. Groven, M. Heyns, D. Lin, I. Asselberghs, and I. Radu, *Sci. Rep.*, 11, 6610 (2021). [DOI: https://doi.org/10.1038/s41598-021-85968-y]

- [4] S. Zhang, *J. Phys.: Conf. Ser.*, **1617**, 012054 (2020). [DOI: https://doi.org/10.1088/1742-6596/1617/1/012054]

- [5] R. Kim, U. E. Avci, and I. A. Young, *IEEE J. Electron Devices Soc.*, 3, 37 (2015). [DOI: https://doi.org/10.1109/JEDS.2014. 2363389]

- [6] J. S. Yoon, S. Lee, J. Lee, J. Jeong, H. Yun, B. Kang, and R. H. Baek, *IEEE Access*, 7, 172290 (2019). [DOI: https://doi.org/10.1109/ACCESS.2019.2956503]

- [7] H. H. Radamson, X. He, Q. Zhang, J. Liu, H. Cui, J. Xiang, Z. Kong, W. Xiang, J. Li, J. Gao, H. Yang, S. Gu, X. Zhao, Y. Du, J. Yu, and G. Wang, *Micromachines*, 10, 293 (2019). [DOI: https://doi.org/10.3390/mi10050293]

- [8] K. Baral, P. K. Singh, S. Kumar, S. Chander, K. Singh, and S. Jit, Proc. 2018 3rd International Conference for Convergence in Technology (I2CT) (IEEE, Pune, India, 2018) p. 1. [DOI: https://doi.org/10.1109/I2CT.2018.8529584]

- [9] P.S.T.N. Srinivas, A. Kumar, and P. K. Tiwari, Proc. 2019 IEEE 9th International Nanoelectronics Conferences (INEC) (IEEE, Kuching, Malaysia, 2019) p. 1. [DOI: https://doi.org/10.1109/

- INEC.2019.8853855]

- [10] S. Folkersma, J. Bogdanowicz, A. Schuze, P. Favia, A. Franquet, V. Spampinato, D. H. Petersen, O. Hansen, H. H. Henrichsen, P. F. Nielsen, L. Shiv, and W. Vandervorst, *Proc. 2018 22nd International Conference on Ion Implantation Technology (IIT)* (IEEE, Würzburg, Germany, 2018) p. 153. [DOI: https://doi.org/10.1109/IIT.2018.8807934]

- [11] T. Saxena, V. Khemka, G. Qin, M. Zitouni, and R. Gupta, *IEEE Trans. Electron Devices*, **68**, 658 (2021). [DOI: https://doi.org/10.1109/TED.2020.3043993]

- [12] S. Sarkhel and N. Bagga, Proc. 2020 IEEE Applied Signal Processing Conference (ASPCON) (IEEE, Kolkata, India, 2020) p. 208. [DOI: https://doi.org/10.1109/ASPCON49795.2020. 9276694]

- [13] M. I. Khan, I.K.M.R. Rahman, and Q.D.M. Khosru, *IEEE Trans. Electron Devices*, **67**, 3568 (2020). [DOI: https://doi.org/10.1109/TED.2020.3011645]

- [14] N. K. Niranjan, S. Choudhury, M. Choudhury, K. L. Baishnab,

K. Guha, and J. Iannacci, *Microsyst. Technol.*, 27, 3757 (2021).

[DOI: https://doi.org/10.1007/s00542-020-05160-6]

- [15] S. Gupta, N. Pandey, and R. S. Gupta, Proc. 2020 IEEE 17th India Council International Conference (INDICON) (IEEE, New Delhi, India, 2020) p. 1. [DOI: https://doi.org/10.1109/ INDICON49873.2020.9342380]

- [16] D. Y. Jeon, M. Mouis, S. Barraud, and G. Ghibaudo, *IEEE Trans. Electron Devices*, **67**, 4736 (2020). [DOI: https://doi.org/10.1109/TED.2020.3020284]

- [17] D. Bosch, J. P. Colinge, G. Ghibaudo, X. Garros, S. Barraud, J. Lacord, B. Sklenard, L. Brunet, P. Batude, C. Fenouillet-Béranger, J. Cluzel, R. Kies, J. M. Hartmann, C. Vizioz, G. Audoit, F. Balestra, and F. Andrieu, *Proc. 2020 IEEE Symposium on VLSI Technology* (IEEE, Honolulu, USA, 2020) p. 1. [DOI: https://doi.org/10.1109/VLSITechnology18217. 2020.9265036]

- [18] D. Bosch, J. P. Colinge, J. Lugo, A. Tataridou, C. Theodorou, X. Garros, S. Barraud, J. Lacord, B. Sklenard, M. Casse, L. Brunet, P. Batude, C. Fenouillet-Béranger, D. Lattard, J. Cluzel, F. Allain, R. N. Youcef, J. M. Hartmann, C. Vizioz, G. Audoit, F. Balestra, and F. Andrieu, Proc. 2020 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA) (IEEE, Hsinchu, Taiwan, 2020) p. 126. [DOI: https://doi.org/10.1109/VLSI-TSA48913.2020.9203690]

- [19] M. I. Khan, I.K.M.R. Rahman, and Q.D.M. Khosru, *IEEE Trans. Electron Devices*, **67**, 3568 (2020). [DOI: https://doi.org/10.1109/TED.2020.3011645]

- [20] B. Singh, D. Gola, K. Singh, E. Goel, S. Kumar, and S. Jit, *IEEE Trans. Electron Devices*, **63**, 2299 (2016). [DOI: https://doi.org/10.1109/TED.2016.2556227]

- [21] S. A. Hashemi, K. Beigi, and S. Jit, *IEEE Trans. Electron Devices*, 66, 4126 (2019). [DOI: https://doi.org/10.1109/TED. 2019.2937205]

- [22] V. Kumari, A. Kumar, M. Saxena, and M. Gupta, *Superlattices Microstruct.*, **113**, 57 (2018). [DOI: https://doi.org/10.1016/j.spmi.2017.09.049]

- [23] P. K. Tiwari, S. Kumar, S. Mittal, V. Srivastava, U. Pandey, and S. Jit, Proc. 2009 International Multimedia, Signal Processing and Communication Technologies (IEEE, Aligarh, India, 2009) p. 52. [DOI: https://doi.org/10.1109/MSPCT.2009.5164172]

- [24] Z. Ding, G. Hu, J. Gu, R. Liu, L. Wang, and T. Tang, *Microelectron. J.*, **42**, 515 (2011). [DOI: https://doi.org/10.1016/j.mejo.2010.11.002]

- [25] P. K. Singh, K. Baral, S. Kumar, A. K. Singh, M. R. Tripathy, R. K. Upadhyay, and S. Jit, *Proc. 2020 IEEE International Conference on Electronics, Computing and Communication Technologies (CONECCT)* (IEEE, Bangalore, India, 2020) p. 1. [DOI: https://doi.org/10.1109/CONECCT50063.2020.9198488]

- [26] C. Jiang, R. Liang, J. Wang, and J. Xu, AIP Adv., 5, 057122 (2015). [DOI: https://doi.org/10.1063/1.4921086]

- [27] H. Jung, *Int. J. Electr. Electron. Eng. Telecommun.*, **8**, 334 (2019). [DOI: https://doi.org/10.18178/ijeetc.8.6.334-339]