ISSN: 2288-243X (Online) j.inst.Korean.

# Deep-Trench 기술을 적용한 Super Junction MOSFET의 Charge Balance 특성에 관한 연구 A Study on the Charge Balance Characteristics of Super Junction MOSFET with Deep-Trench Technology

최 종 문\*, 허 윤 영\*, 정 헌 석\*, 강 이 구\*\*

Jong-Mun Choi\*, Yoon-Young Huh\*, Heon-Seok Cheong\*, Ey-Goo Kang\*

#### Abstract

Super Junction structure is the proposed structure to minimize the Trade-off phenomenon of power devices. Super Junction can have On-resistance(Ron) characteristics as less as five times than conventional structure.

There are process methods that Multi-Epi and Deep-Trench of Super Junction structure. The reason for this is that Deep-Trench process is known to be a relatively difficult manufacturing method because it is easy to form a P-Pillar by burying impurities on top of a silicon substrate through a Deep-Trench process. However, the structure created by the Deep-Trench process has low On-resistance and high breakdown voltage, showing better efficiency. In this paper, we suggested a novel method in the process and designed structure with Charge Balance theory.

#### 요 약

파워 소자의 트레이드오프 현상을 최소화하기 위해 제시된 구조가 Super Junction 구조이다. Super Junction은 기존의 많이 사용하던 기본 구조 대비 1/5 정도의 낮은 온 저항(Ron) 특성을 가질 수 있다. Super Junction 구조의 공정 방법으로 Multi-Epi 공정과 Deep-Trench 공정 방법이 있다. Deep-Trench 공정은 실리콘 기판 상면에 깊은 트렌치 공정을 통하여 그 안에 불순물이 도핑 되어 있는 폴리실리콘을 매립하여 P-Pillar를 형성 시키는 공정 방법이라 매립하는 과정에서 결함이 형성되기 쉬워서 비교적 어려운 제조 방법으로 알려져 있다. 하지만 비교적 Deep-Trench 공정으로 만들어진 구조가 낮은 온 저항과 높은 항복 전압을 형성하여 좋은 효율을 보인다. 본 논문에서는 공정상의 새로운 방법을 제시하고, Charge Balance 이론을 접목시킨 구조를 설계하였다.

Key words: Power Device, Trade-off, Super Junction, Deep-Trench, Charge Balance

ISSN: 1226-7244 (Print)

논문번호 21-02-18

E-mail: keg@kdu.ac.kr, Tel: +82-43-880-3292

Acknowledgment

This research was supported by Korea Institute of Energy Technology Evaluation and Planning (20194010201810 and 2019). / Global Cooperation on Innovative Graduate Student Engineers on Power Semiconductors for Renewable Energy and Intelligent Power System(20194010000050)

Manuscript received May. 17, 2021; revised Jun. 3, 2021; accepted Jun. 25, 2021.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Dept. of Energy IT Engineering, Far East University

<sup>★</sup> Corresponding author

## I . 서론

파워 소자는 스위칭 제어가 주인 소자이기 때문에 소자 전원이 꺼진 상태에서 전류가 흐르지 않으며, 소자가 켜진 상태에서는 전압강하(Voltage Drop)가 없이 전력을 효율적으로 활용하며 손실 전력을 최 소화 하여야한다.

고전압과 고전류를 처리하는 과정에서 소자에 가해지는 열과 스트레스 또한 전력소자의 성능저하를 일으키므로 중요한 설계 변수이다. 항복전압 (Breakdown Voltage)과 온 저항(Ron)은 서로 트레이드오프(Trade-off) 관계로 연관 되어 있기 때문에 높은 항복전압과 낮은 온 저항을 만들어 내기에 기술적 어려움을 겪는다[1], [2].

이러한 트레이드오프 관계를 최소화 시킬 수 있는 900 V급 Deep-Trench Super Junction MOSFET구 조를 설계하고, Deep-Trench 공정을 방법을 변형하여 Charge Balance 이론을 접목시켜 기존 보다더 효율적인 Super Junction MOSFET을 제시하고자 한다[3]-[6].

### Ⅱ. 본론

# 1. Super Junction MOSFET 기본 구조 설계

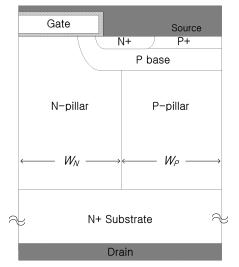

Fig. 1. Structure of Super Junction MOSFET. 그림 1. Super Junction MOSFET 구조

그림 1은 Super Junction MOSFET의 기본적인 구조의 그림이다. 기본 구조를 설계하여 게이트가 0 V일 때 드레인의 전압을 인가하여 전계분포 그 래프를 확인 하면 그림 2와 같이 확인된다.

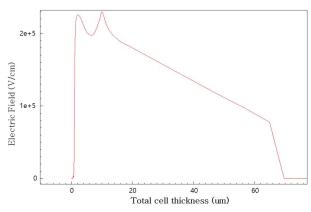

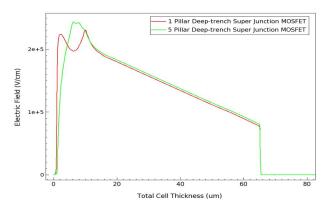

Fig. 2. Electric Field of Deep-Trench Super Junction MOSFET.

그림 2. Deep-Trench Super Junction MOSFET의 Electric Field

그림 2에서 전계가 가장 크게 집중되는 두 곳을 확인 할 수 있다. 첫 번째로 전계가 많이 집중되는 곳은 그래프 앞단의 P-Base와 P-Pillar 접합부이고, 두 번째는 P-Pillar의 가장 아래 부분, 즉, P-Pillar 와 Drift영역의 접합부에서 가장 높은 전계가 형성 되었다. Super Junction MOSFET의 구조 특성상 전계 집중은 Pillar 부분에 고르게 분포되어야 하지 만, Deep-Trench 공정 특성상 필러의 일정 부분의 농도 조절이 어렵다. 이러한 공정 변수는 N-Pillar의 영향을 받는다. Pillar 구조를 설계할 때 P-Pillar와 N-Pillar의 농도를 각층에 알맞게 선택하여 층마다 설계할 수 있는 Multi-Epi 공정에 비해 본 구조에 서는 J-FET을 이온 주입하여 확산시켜 N-Pillar 역할을 수행하게 한다. 이러한 공정 특성상 이온 주입된 상단부에는 고농도의 J-FET이, 하단부로 확산된 J-FET 영역은 비교적 낮은 농도로 형성된 다. 이와 같은 공정상의 문제로 전계가 특정 부분 에 집중되는 것을 확인할 수 있었다.

#### 2. 전계 분산을 위한 P-Pillar 구조 변형

기존의 Deep-Trench 구조에서 시뮬레이션 상에 P-Pillar 부분의 식각 커맨드를 변경하였다.

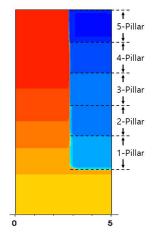

Deep-Trench 기본 구조를 만들 때는 P-Pillar 영역의 식각 공정 후, 그 안에 P형을 이온 주입하는 공정이 한번만 진행되었지만, 변경한 구조에서는 처음 깊이를 10 um으로 식각하고 동일하게 이온 주입을 한 후 주입되어있는 P형 물질에 층을 나누기 위해서 2 um를 남긴 나머지를 다시 식각하는 공정 시뮬레이션 커맨드를 다섯 차례로 변경 하였

다. 그 결과 그림 3과 같이 5개의 P-Pillar 층을 만들 수 있었다. 그 후 각 층의 P-Pillar 영역 이온 주입 농도를 변수로 두고 각 층마다 농도를 다르게하여 Super Junction Charge Balance 이론을 적용하고자 하였다.

Fig. 3. Deep-Trench Super Function MOSFET with Modified Structure.

그림 3. 변형된 P-Pillar 구조의 Deep-Trench Super Junction MOSFET

## 3. Super Junction구조상의 Charge Balance

$$N_a \cdot pillar \times W_p = N_d \cdot pillar W_p \tag{1}$$

Super Junction MOSFET 구조의 항복전압은 최 적화를 위해 P-Pillar와 N-Pillar영역의 전하량이 동일하게 설정해야 한다. P-Pillar와 N-Pillar영역 의 전하량의 비율을 1:1로 설계하는 것을 전하량 균형(Charge Balance)이라 정의하고 식 (1)과 같은 조건을 만족해야 한다. 식 (1)에  $N_{a}pillar$ 와  $N_{a}pillar$ 는 각 P-Pillar와 N-Pillar 영역의 농도를 의미한다. 따라서 P-Pillar와 N-Pillar 영역의 농도도 같이 동 일하게 설계해야 한다. 식 (1)의 조건을 만족시키는 Super Junction MOSFET은 두 Pillar의 전하량이 같으므로 두 Pillar 영역이 완전 공핍화가 된다. 오 프 상태일 때, 공핍층이 N-Drift 영역을 따라서 수 직으로 확장하는 것과 함께 수평으로도 확장되기 때문에 공핍층의 길이는 P-Pillar 깊이와 넓이에 따라 형성되어 짧은 길이가 공핍화 되기 때문에 N-Drift 영역의 농도를 높게 할 수 있다. N-Drift 영역의 농도를 높게 할 수 있어서, Super Junction MOSFET의 경우 일반적인 MOSFET보다 온 저항 이 작고 항복전압은 유지 할 수 있다[1]-[6].

## 4. Charge Balance 실험 과정

가. 첫 번째 P-Pillar 실험

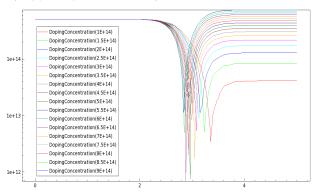

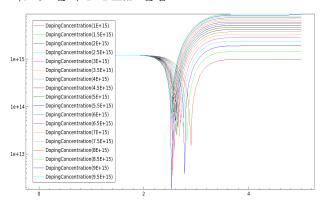

Fig. 4. Doping Concentration (horizontal direction) according to 1st P-pillar concentration variation.

그림 4. 첫 번째 P-Pillar 농도 변화에 따른 Doping Concentration(수평 방향)

첫 번째 P-Pillar의 농도 변화를 통하여 N-Pillar 와의 Charge Balance를 맞춘 실험 그래프이다. 이전에 하나의 P-Pillar 농도로 구조를 만들었을 때의 P-Pillar의 모양이 제일 하단부가 크게 형성되었던 경험을 토대로 농도를 비교적 낮게 실험 하였다. 1E+14부터 9E+14까지 0.5E+14 씩 증가 시켰을때 8E+14의 농도에서 Pillar간의 농도X크기의 비율이 1:1을 이루는 것을 확인 하여 첫 번째 P-Pillar의 농도는 8E+14로 선택하고 두 번째 실험을 진행하였다.

#### 나. 두 번째 P-Pillar 실험

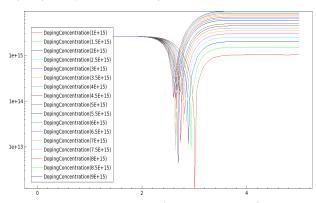

Fig. 5. Doping Concentration (horizontal direction) according to 2st P-pillar concentration variation.

그림 5. 두 번째 P-Pillar 농도 변화에 따른 Doping Concentration(수평 방향)

두 번째 P-Pillar의 농도를 1E+15부터 9.5E+15까지 0.5E+15 씩 변수로 두어 실험하였다. 그 결과 두 번

째 P-Pillar의 농도가 2.5E+15일 때 Pillar간의 농도 X크기의 비율이 1:1임을 확인하였고, 그 값을 선택하고 세 번째 실험을 진행하였다.

#### 다. 세 번째 P-Pillar 실험

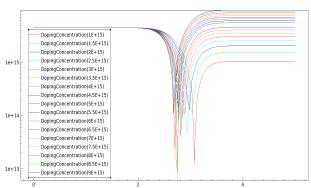

Fig. 6. Doping Concentration (horizontal direction) according to 3st P-pillar concentration variation.

그림 6. 세 번째 P-Pillar 농도 변화에 따른 Doping Concentration (수평 방향)

세 번째 P-Pillar의 농도를 1E+15부터 9E+15까지 0.5E+15 씩 변수로 두어 실험 하였다. 그 결과 세 번째 P-Pillar의 농도가 5.5E+15일 때 Pillar간의 농도×크기의 비율이 1:1임을 확인하였고, 그 값을 선택하고 네 번째 P-Pillar의 실험을 진행하였다.

#### 라. 네 번째 P-Pillar 실험

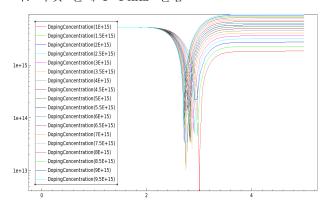

Fig. 7. Doping Concentration (horizontal direction) according to 4st P-pillar concentration variation.

그림 7. 네 번째 P-Pillar 농도 변화에 따른 Doping Concentration(수평 방향)

네 번째 P-Pillar의 농도를 1E+15부터 9E+15까지 0.5E+15 씩 변수로 두어 실험하였다. 그 결과 네 번째 P-Pillar의 농도가 6.5E+15일 때 Pillar간의 농도 ×크기의 비율이 1:1임을 확인 하였고, 그 값을 선택하고 다섯 번째 P-Pillar의 실험을 진행하였다.

# 마. 다섯 번째 P-Pillar 실험

Fig. 8. Doping Concentration (horizontal direction) according to 5st P-pillar concentration variation.

그림 8. 다섯 번째 P-Pillar 농도 변화에 따른 Doping Concentration(수평 방향)

다섯 번째 P-Pillar의 농도를 1E+15부터 9.5E+15까지 0.5E+15씩 변수로 두어 실험하였다. 그 결과다섯 번째 P-Pillar의 농도가 9.5E+15일 때 Pillar간의 농도×크기의 비율이 1:1임을 확인하였다. 이로써 모든 Pillar층의 수평 방향의 농도X크기를 1:1비율로 모두 맞추어 Charge Balance 이론을 적용하는데 마무리 하였다.

# 바. Charge Balance 이론을 적용한 Super Junction MOSFET

Fig. 9. Top Structure of 5-Pillar Deep-Trench MOSFET. 그림 9. 5-Pillar Deep-Trench MOSFET의 상단 구조

위와 같은 실험으로 만들어진 구조의 그림은 그림 9와 같이 형성되었다. 하나의 농도로 이루어진 P-Pillar를 갖는 Deep-Trench 구조와 실험을 통해만들어진 구조의 전계 분포를 비교한 그래프는 그림 10이다. 그 결과 하나의 농도로만 이루어진 구조에서 확인하였던 특정 부위에서만 높은 전계를

집중시키던 현상을 필러 전체로 고르게 형성시킬 수 있었다.

Fig. 10. Comparison of Electric Fields with P-Pillar Structure Changes.

그림 10. P-Pillar 구조 변경에 따른 Electric Field 비교

#### Ⅲ. 결론

본 논문에서는 Super Junction MOSFET에 Charge Balance의 이론적 대입을 시뮬레이션을 통하여 연구하였다.

기본적인 Super Junction MOSFET의 구조는 기존의 Planar Gate Type MOSFET을 이용하여 P-Pillar 형성을 위한 실험 커맨드를 추가하여 구조를 만들었고, 이론을 바탕으로 다양한 변수 값을 통해 900 V급 Super Junction MOSFET의 기본 파라미터를 도출해낼 수 있었다. 도출한 구조를 통해전기적 특성과 전계 집중 특성을 확인하였고 그에따른 이론적 고찰과 실험을 통해 차이점과 해결 방안을 제시하고자 하였다.

P-Pillar를 하나의 층으로 설계한 Deep-Trench 구조에서 확인했던 전계 분포 그래프로 보았을 때, 특정 지점에서 높은 집중도를 확인 하였고, 이와 같은 현상을 완화시키기 위해 Multi-Epi 구조 설계 방법을 인용하여 Deep-Trench 구조에도 P-Pillar를 층을 나누어 설계하고자 하였다. 그 방법으로 식각을 여러 차례 진행하여 각기 다른 농도를 가지는 5개 층의 P-Pillar를 설계할 수 있었다. 그 후에는 Charge Balance 이론을 이용하여 각층의 N-Pillar와 P-Pillar의 농도×크기의 비율을 1:1로 맞추는 실험을 진행하였다. 그 결과, 온 저항은 1%내외로 큰변화 없이, 항복전압 특성에서 879 V보다 10% 이상 향상된 966 V의 항복전압을 갖는 Deep-Trench

구조를 설계할 수 있었다.

필러를 하나의 농도로 지정하여 Pillar간의 일정한 크기를 형성하고 Charge Balance를 전체적으로 맞추기 어려웠던 공정상의 어려움을 시뮬레이션을 통하여 방안을 제시하고자 하였다. Super Junction MOSFET의 연구가 계속해서 진행되고 있는 현재로서, 효율적인 구조의 Super Junction MOSFET의 연구 개발에 도움이 될 것으로 생각된다.

#### References

[1] Lee, Geon Hee, Byoung Sup Ahn, and Ey Goo Kang. "Analysis of Electrical Characteristics According to the Pillar Spacing of 4.5 kV Super Junction IGBT," *Journal of the Korean Institute of Electrical and Electronic Material Engineers*, 33. no.3, pp.173–176, 2020.

DOI: 10.4313/JKEM.2020.33.3.173

[2] Kang, Ey Goo. "Optimal Process Design of Super Junction MOSFET," *Journal of the Korean Institute of Electrical and Electronic Material Engineers*, Vol.27. no.8, pp.501–504, 2014.

[3] Lee, Jung-Hoon, Eun-Sik Jung, and Ey-Goo Kang. "A Study on 600 V Super Junction Power MOSFET Optimization and Characterization Using the Deep Trench Filling," *Journal of the Korean Institute of Electrical and Electronic Material Engineers*, Vol.25, no.4, pp.270–275, 2012.

DOI: 10.4313/JKEM.2012.25.4.270

[4] J. M. Geum, "A study on the optimization of trenchetch and ion implantation designing SiC super junction MOSFET," Dissertation, Korea University, 2016.

[5] Kang, Ey Goo. "Developing of Super Junction MOSFET According to Charge Imbalance Effect." Journal of the Korean Institute of Electrical and Electronic Material Engineers, Vol.27. no.10, pp.613–617, 2014. DOI: 10.4313/JKEM.2014.27.10.613 [6] Kang, Ey Goo. "Electrical Characteristics of Super Junction MOSFET According to Trench Etch Angle of P-pillar," Journal of the Korean Institute of Electrical and Electronic Material Engineers, Vol.27. no.8, pp.497–500, 2014.

# **BIOGRAPHY**

#### Jong-Mun Choi (Member)

2018: BS degree in Photovoltaic Engineering, Far East University. 2020: MS degree in Energy Semiconductor Engineering, Far East University.

2021 ~ present : Ph.D degree in Energy IT Engineering, Far East University.

#### Yoon-Young Huh (Member)

2020: BS degree in Photovoltaic Engineering, Far East University. 2020~present: MS degree in Energy IT Engineering, Far East University.

#### Heon-Seok Cheong (Member)

1991: BS degree in Computer Science and Engineering, Seoul National University of Science and Technology. 1993: MS degree in Computer Science and Engineering, Hongik University. 1999: Ph.D degree in Computer Science and Engineering, Hongik University.

2003~2021: Professor, Far East University. Faculty of Power Devices and ICs

# Ey-Goo Kang (Member)

1993: BS degree in Electrical Engineering, Korea University.

1995: MS degree in Electrical Engineering, Korea University.

2002: Ph.D degree in Electrical Engineering, Korea University.

2003~2021: Professor, Far East University. Faculty of Power Devices and ICs