https://doi.org/10.6113/TKPE.2021.26.3.237

# 순환전류 감소를 위한 새로운 정류회로를 갖는 위상천이 풀브리지 컨버터

최병기<sup>1</sup>, 이우석<sup>1</sup>, 이일운<sup>†</sup>

# A Phase-Shifted Full-Bridge Converter With a New Rectifier Circuit for Reducing Circuiting Current

Byoung-Gi Choi<sup>1</sup>, Woo-seok Lee<sup>1</sup>, and Il-Oun Lee<sup>†</sup>

#### **Abstract**

This research proposes a new rectifier circuit to reduce the circulating current of a phase-shifted full bridge converter. The proposed circuit is a structure in which the output inductor of the secondary rectifier circuit is changed to a coupled inductor in the phase-shifted full bridge with the existing center-tapped rectifier. The parts are rearranged after adding a diode. After applying the proposed circuit, the circulating current to the primary current of the transformer and the voltage stress of the rectifier diode on the secondary side of the transformer are reduced. Accordingly, the snubber loss of the rectifier is improved. By reducing the circulating current and snubber loss, the circuit achieves higher efficiency than conventional circuits. In this research, we present the structure of the proposed circuit, its strengths, and the analysis results from experiments. Furthermore, its effectiveness is verified through the experimental results of a prototype converter with an input of 300-400 V and an output of 50 V/1 kW.

Key words: Circulating current, Phase-shifted full-bridge, DC/DC converter

#### 1. 서 론

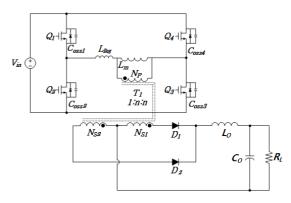

최근 5G 네트워크 장비가 상용화되면서 기존 LTE 중계기보다 같은 공간에 많은 옥외용 중계기를 설치해야하는 어려움과 더불어 옥외용 중계기의 전력 소비량이크게 증가하였다. 이로 인해 중계기에 전원을 공급하는 전원장치의 고효율 성능이 강화되었고, 중계기들이 옥외에 설치됨에 따라 입력전원이 불안정하여 넓은 입력전압범위를 갖는 정류기의 개발이 요구되고 있다. 본 논문은 정류기 개발에 있어 넓은 입력전압범위에서 동작해야 하는 DC/DC 컨버터 회로기술에 관한 내용을 발표한다. 다양한 DC/DC 컨버터 중에서 그림 1의 위상천이풀브리지 컨버터는 영전압스위칭 달성에 따른 높은 스

Fig. 1. Conventional converter.

위칭 주파수 동작이 가능하다는 장점 때문에 정류기의 DC/DC 컨버터로 널리 사용되어왔다. 그러나 입력전압이 넓게 변하는 사양에서, 그림 1의 기존 위상천이 풀브리지 컨버터는 정상입력전압조건 동작시 작은 유효듀티로 인하여 1차측에 큰 순환전류를 발생시키고, 다이오드의 기생성분과 변압기 누설인덕턴스간 공진에 따른 매우큰 전압스트레스를 갖는다<sup>[1]</sup>. 정류단의 높은 전압스트레스는 고전압 정격 다이오드의 사용을 요구하고, 이는 정

Paper number: TKPE-2021-26-3-11

Print ISSN: 1229-2214 Online ISSN: 2288-6281 Corresponding author: leeiloun@mju.ac.kr, Dept. of Electrical Engineering, Myongji University, Korea Tel: +82-31-330-6833 Fax: +82-031-330-6977

Dept. of Electrical Engineering, Myongji University, Korea Manuscript received Nov. 30, 2020; revised Dec. 11, 2020; accepted Jan. 28, 2021

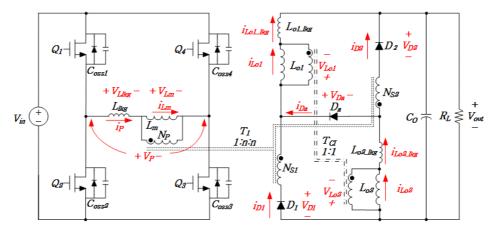

Fig. 2. Proposed converter.

류단 도통손실 증가를 일으키게 된다. 이러한 높은 순환 전류를 감소시키기 위하여 여러 회로들이 제안되었다<sup>[2],[3]</sup>.

제안된 회로들은 순환전류가 감소되고, 1차측 도통손실이 개선된다. 하지만 정류다이오드 전압스트레스 문제는 여전히 존재하고, 추가적인 제어가 필요한 단점이 있다. 더불어 그 연구들이 다이오드 4개로 구성된 풀브리지 정류기를 갖는 위상천이 풀브리지 컨버터에 집중되어 있다. 본 논문에서는 커플더인덕터를 사용한 새로운정류회로를 제안한다. 새로운 정류회로의 적용으로 변압기 1차측 순환전류가 대폭 저감되며, 입출력전압이득이높아져 변압기 권선비 설계가 유리하게 된다. 이는 변압기 1차측 전류스트레스와 2차측 정류다이오드의 전압스트레스 저감을 가능하게 한다.

## 2. 제안 회로

그림 2는 제안된 정류회로를 갖는 위상천이 풀브리지 컨버터를 보여준다. 변압기 1차측은 기존 풀브리지 인버 터로 구성되고 센터탭 변압기를 갖는다. 변압기 2차측 정류회로는 커플드 인덕터를 사용하며, 기존 정류회로에 존재했던 다이오드 2개와 더불어 추가된 다이오드  $D_a$ 를 갖는다. 기존 센터탭 정류기를 갖는 위상천이 풀브리 지 컨버터 부품 수에 비해 다이오드 1개가 추가되었지 만, 앞에서 언급된 제안 회로의 장점으로 정류단 다이오 드  $D_1$ 과  $D_2$ 의 전압정격이 낮아졌고, 또한 추가된 다이 오드  $D_a$ 는 저전류 정격을 가진다. 모든 정류단 다이오 드들이 낮은 전압 스트레스를 가져 스너버회로가 필요 없기 때문에 기존 컨버터에 비해 재료비 측면에서 큰 불리함이 없다고 할 수 있다. 제안 회로의 출력전압 제 어 방식은 기존 위상천이 풀브리지 컨버터와 동일하지 만 1주기 동안 8개의 동작모드를 가지며, 주요 특징과 관련된 모드만 아래 설명하도록 한다.

#### 2.1 제안 회로의 순환전류

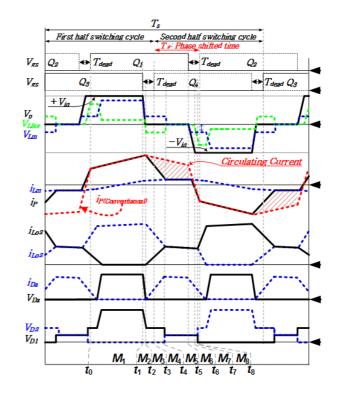

그림 3은 제안 회로에 주요 동작 파형이다. 그림 3에서

Fig. 3. Key operating waveforms of proposed converter in steady state.

기존 회로와 제안 회로의 변압기 1차측 전류  $i_P$ 를 비교하였다. 그림과 같이 기존 회로는  $Q_3$  스위치가 턴 오프되면서 변압기 1차측 전류에 빗금 친 부분에 해당하는 순환전류를 갖는다. 제안 회로에서는 기존 회로에 존재했던 순환전류가 그림 3에서 보듯 저감된다. 그 원리는다음과 같다.

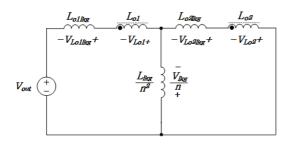

$Q_3$  스위치가 턴 오프되면서 모드 3이 시작된다. 그러면  $V_P$ 는 0V가 되고, 2차측 보조다이오드  $D_a$ 가 턴 온된다. 이 모드에서 2차측 정류회로는 그림 4와 같이 등가회로로 나타낼 수 있다. 커플더인덕터의 누설인덕턴스  $L_{ollkg}$ 와  $L_{o2lkg}$ 가 동일하다고(= $L_{olkg}$ )라고 가정하면,  $V_{Lo1lkg}$ ,  $V_{Lo2lkg}$ 의 전압은 식 (1), (2)와 같이 결정된다.

Fig. 4. Equivalent circuit of the proposed converter Mode 3.

Fig. 5. Voltage gain of conventional and proposed converters.

TABLE I

PROTOTYPE OF CONVENTIONAL

AND PROPOSED CONVERTER

|                |   | Conventional         | Proposed     |

|----------------|---|----------------------|--------------|

| Transformer    |   | 40 T:10 T:10 T       | 40 T:9 T:9 T |

|                |   | (300 [uH])           | (300 [uH])   |

| Inductor       |   | 100 [uH]             | 100 [uH]     |

|                |   |                      | (10T:10T)    |

| Capacitor      |   | 47 uFx6              |              |

| Switches       |   | NTP082N65S3F         |              |

| Diodes         |   | DPG60C300HB          |              |

| RCD<br>snubber | R | UF4004               |              |

|                | С | Capacitor 10 nF/1 kV |              |

|                | D | Register 10 kΩ/20 W  |              |

$$V_{Lo1lkg} = -\frac{L_{olkg}}{2L_{olkg} + 4(L_{lkg}/n^2)} V_{out}$$

(1)

$$V_{Lo2lkg} = \frac{L_{olkg}}{2L_{olkg} + 4(L_{lkg}/n^2)} V_{out}$$

(2)

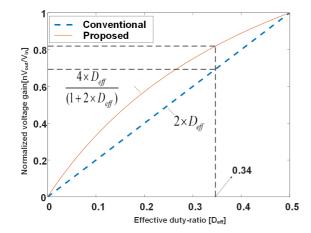

## 2.2 제안 회로의 전압이득

제안 회로의 전압이득은 커플더인덕터 양단에 걸리는 전압에 전압-시간-평형 원리를 적용하여 구한다. 그림 5 는 유효듀티에 관한 전압이득 곡선을 보여준다. 제안 회 로는 기존 회로보다 높은 전압이득을 가지는 것을 알 수 있다. 높은 전압이득으로 인하여 제안 회로는 높은

Fig. 6. Key waveforms of the proposed converter at Vin = 400 V.

Fig. 7. Key waveforms of the conventional converter at Vin = 400 V.

권선비 설계가 가능하다. 그 결과 제안 회로의 2차측 정류다이오드에 전압스트레스가 기존 회로에 비해 훨씬 낮게 된다. 이는 동일한 시정수의 RCD 스너버 회로 사용 시 제안 회로에서의 스너버 손실이 기존보다 훨씬 낮게 됨을 의미하고 효율 측면에서 보다 유리함을 의미한다.

#### 3. 실험 결과

제안된 컨버터의 효율성과 타당성을 검증하기 위하여 제안 회로와 기존 회로의 비교 실험을 진행하였다. 제안 회로와 기존 회로의 설계 사양은 다음과 같다.

1) Input voltage:  $V_{in}$  = 300–400V

2) Output voltage:  $V_{out} = 50$ V

3) Maximum power:  $P_{\text{max}} = 1 \text{kW}$

#### 3.1 동작 파형

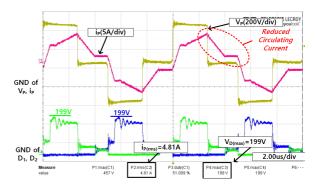

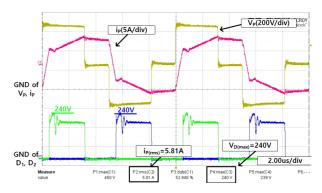

그림 6, 7은 입력 400V, 최대 부하 20A에서 제안된 컨버터와 기존 컨버터의 주요파형을 보여준다. 그림 6에 서와 같이 측정된 모든 파형은 그림 3에 설명된 이론적 파형과 동일하게 나오는 것을 알 수 있다. 그림 6, 7에 서 볼 수 있듯 제안된 컨버터의 순환전류가 대폭 저감 되는 것을 확인할 수 있다. 따라서 그림 6, 7의 변압기

Fig. 8. Loss break down between the proposed converter and the conventional converter.

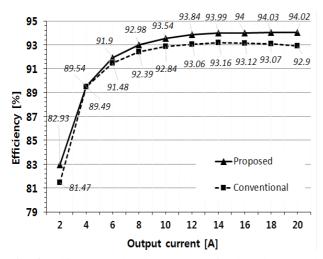

Fig. 9. Effiency graph of the conventional and proposed converter at 400 V input voltage.

1차측 전류  $i_P$  전류를 비교하면 순환전류 감소로 RMS 전류 stress가 저감되는 것을 확인할 수 있다.

#### 3.2 다이오드 전압스트레스

그림 6, 7은 동일한 스너버 회로를 사용하여 입력전압 400V, 출력 50V, 1.0kW 부하 조건에서 정류다이오드의 전압스트레스를 보여준다. 스너버 회로 설계는 표 1에서 볼 수 있다. 그림 6, 7 실험 파형에서 보듯이 제안 회로는 기존 회로보다 높은 입출력이득으로 인하여 높은 변압기 권선비를 가지게 되고, 그 결과 전압스트레스가66V 이상 낮게 된다.

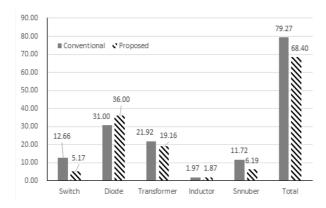

#### 3.3 효율

그림 8은 제안 회로와 기존 회로의 부품별 손실분석 자료이다. 그림에서 볼 수 있듯 제안 회로는 다이오드 1개 의 추가로 인한 손실이 5W 추가된다. 하지만 순환전류 감소에 따른 도통손실 감소와 스너버손실 감소로 총 17W 이상의 손실이 저감되는 것을 확인할 수 있다. 결 과적으로 제안된 컨버터는 그림 9에서 보듯 전 부하 영 역에서 동등 혹은 그 이상의 효율을 달성하게 된다.

#### 4. 결 론

본 논문에서는 커플드인덕터를 사용한 새로운 정류회로를 가진 위상천이 풀브리지 컨버터를 제안하였다. 제안하는 회로는 기존 위상천이 풀브리지 컨버터의 단점인 1차측 순환전류를 저감시켜 변압기와 스위치에서 발생되는 도통손실을 저감할 수 있다. 또한, 제안 회로는 변압기의 높은 입출력이득으로 정류다이오드의 전압스트레스가 기존 회로에 비하여 대폭 저감시킬 수 있는 것이 장점이다. 제안 회로의 동작 특성을 확인하기 위하여 1.0kW급 시제품을 제작하여 기존 회로와 비교 실험을 진행하였다. 실험 결과로부터 제안 회로가 기존 회로와 비교하여 우수한 성능과 특성을 가짐을 확인하였다. 실험 결과를 바탕으로 제안 회로는 입력전압범위가 넓고 고효율을 요구하는 어플리케이션에 적합하다고 할수있다.

본 연구는 2020년도 정부(교육부)의 재원으로 한 국연구재단의 지원을 받아 수행된 기초연구사업임. (NRF-2020R1D1A1B07048209)

# References

- [1] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "Design considerations for high-voltage high-power full-bridge zero-voltage-switched PWM converter," in *Fifth Annual Proceedings on Applied Power Electronics Conference Exposition, Los Angeles, CA, USA*, pp. 275–284, 1990.

- [2] K. S. Jeong, Y. C. Lee, H. K. Kim, C. Park, S. H. Kim, and S. S. Hong, "Switch control method for phase-shift full-bridge converter using active clamp circuit procediengs," in *Korea Institute of Power Electronics Annual Conference*, pp. 163–164, Jul. 2014.

- [3] C. Lee and Y. C. Hong, "A study on energy efficiency improvement of ldc recycling load tester," *Journal of th e Korea Academia-Industrial Cooperation Society*, Vol. 17, No. 10, pp. 86–92, 2016.