# 신호감지회로를 가진 극소형 위상고정루프

박경석, 최영식

# An Ultra Small Size Phase Locked Loop with a Signal Sensing Circuit

Kyung-Seok Park, Young-Shig Choi

요 약 본 논문에서는 신호감지회로(Signal Sensing Circuit : SSC)를 추가하여 2개의 루프로 구성된 단일 커패시터 루프필터를 가진 극소형 위상고정루프(Phase Locked Loop : PLL)를 제안하였다. 위상고정루프 크기를 극단적으로 줄이기 위하여 가장 많은 면적을 차지하는 수동소자 루프필터를 극소형 단일 커패시터(2pF)로 설계하였다. 신호감지회로가 포함된 내부 부궤환 루프 출력이 외부 부궤환 루프의 단일 커패시터 루프필터 출력에 부궤환 역할을 하여 제안한 극소형 위상고정루프가 안정적으로 동작하도록 설계하였다. 위상고정루프 출력 신호 변화를 감지하는 신호 감지 회로는 루프필터의 커패시턴스 전하량을 조절하여 위상고정루프 출력 주파수의 초과 위상변이를 줄였다. 제안된 구조는 기존 구조에 비해 1/78 정도의 작은 커패시터를 가짐에도 불구하고 지터 크기는 10% 정도 차이가 난다. 본 논문의 위상고정루프는 1.8V 180nm 공정을 사용하였고, Spice를 통해 안정하게 동작하는 시뮬레이션 결과를 보여주었다.

**Abstract** In this paper, an ultra small phase locked loop (PLL) with a single capacitor loop filter has been proposed by adding a signal sensing circuit (SSC). In order to extremely reduce the size of the PLL, the passive element loop filter, which occupies the largest area, is designed with a very small single capacitor (2pF). The proposed PLL is designed to operate stably by the output of the internal negative feedback loop including the SSC acting as a negative feedback to the output of the single capacitor loop filter of the external negative feedback loop. The SSC that detects the PLL output signal change reduces the excess phase shift of the PLL output frequency by adjusting the capacitance charge of the loop filter. Although the proposed structure has a capacitor that is 1/78 smaller than that of the existing structure, the jitter size differs by about 10%. The PLL is designed using a 1.8V 180nm CMOS process and the Spice simulation results show that it works stably.

Keywords: Negative Feedback, PLL, Single capacitor loop filter. Signal sensing circuit

#### 1. 서론

최근 반도체의 집적 기술향상으로 칩(Chip) 크기를 줄이기 위한 연구가 계속되고 있다. 많은 반도체 시스템들은 디지털 회로와 아날로그 회로를 같이 사용한다. 디지털 회로의 경우는 집적화가 비교적 쉬워서 크기를 줄이기가 용이하지만 아날로그 회로들은 집적화에 따른 크기를 줄이기 쉽지 않아 칩에서 차지하는 비율이 오히려 늘어나고 있다.[11] 특히 위상고정루프는 칩의 기준 신

호인 클록 신호 생성기 역할을 하여 모든 칩에 들어가고 있다. 위상고정루프를 설계할 때 칩 크기를 결정하는 요소는 안정한 동작을 위해 결정적인 역할을 하는 루프필터에 사용되는 커패시터 용량이다. [2] 충분한 위상여유를 가지는 데 필요한 큰 커패시터 용량으로 인하여 칩 외부에 위치하거나, 칩 내부로 집적화되어도 칩의 상당한 면적을 차지한다.

커패시터의 용량을 줄이기 위한 연구들이 예전부터 지금까지 많이 진행되었다. 두 개의 이득 값을 가진 전

This work was supported by a Research Grant of Pukyong National University. (2021-2023)

<sup>\*</sup>Department of Electronic Engineering, Pukyong National University.

<sup>\*\*\*</sup>Corresponding Author: Department of Electronic Engineering, Pukyong National University (pksildung@pukyong.ac.kr)

Received November 03, 2021 Revised November 07, 2021 Accepted December 01, 2021

압제어발진기(Voltage Controlled Oscillator: VCO) 를 이용하여 유효 커패시터를 증가시켜 작은 커패시터 로도 안정적인 동작이 가능한 회로가 연구되었다.[3] 기 판형 커패시터 용량을 증가시키는 회로와 시간 평균 커 패시터 용량을 크게 하는 회로를 이용하여 작은 용량의 커패시터를 가지고도 큰 커패시터의 효과를 내주는 회 로도 만들어졌다.[4] 2개의 전류원을 통해 유효 커패시터 를 증가시키는 회로도 설계되었다.<sup>[5]</sup> 이러한 구조들은 복수 개의 전류원과 부가적인 회로가 추가되어서 출력 의 잡음 특성에 영향을 줄 수 있다. 복수 개의 루프를 사 용하여 루프필터에 사용되는 커패시터 용량을 줄인 구 조도 연구되었다<sup>[6]</sup>. 이 구조는 복수 개의 루프 사용으로 인하여 전력 소모가 증가한다.

앞서 언급한 아날로그 위상고정루프 뿐만 아니라 면 적을 많이 차지하는 수동 소자 루프필터가 없어서 소형 으로 제작이 가능한 디지털 위상고정루프도 많이 연구 되었다. 인덕터-커패시터 발진기를 기반으로한 오버샘 플링(Oversampling) 디지털 위상고정루프가 연구되었 다.[7] 샘플링된 전압이 많을수록 출력주파수의 정확도가 향상되지만, 그만큼 많은 샘플링회로가 필요하여 칩 면 적이 증가한다. 정수가 아닌 분수 값을 가진 분주기 (Divider)를 이용해 위상 오차를 줄인 디지털 위상고정 루프도 연구되었다.[8] 분주기의 배수(N)가 작을수록 위 상잡음을 개선할 수 있어서 아예 분주기를 사용하지 않 는 회로도 연구되었다.[9][10] 이러한 구조는 분주기가 없 어 그만큼 부수적인 회로가 필요하다. 또한 기준 신호 주파수가 상당히 높은 대역이라 칩 외부 기생 수동 소자 의 영향이 커져서 설계가 용이하지 않을 것이다. 디지털 위상고정루프들은 샘플링 비트수가 높을수록 정교한 동 작 제어가 가능하지만, 그만큼 샘플링 회로가 차지하는 칩의 면적이 커지게 될 수 있다.

제안하는 위상고정루프는 가장 많은 면적을 차지하는 수동 소자 루프필터의 커패시터를 최소화하기 위해 단 일 소형커패시터를 가진 루프필터로 설계되었다. 작은 용량의 커패시터를 가지는 만큼 칩 내부에서 위상고정 루프가 차지하는 면적이 매우 작아졌다. 단일 커패시터 루프필터는 동작이 불안정하게 되므로 이를 보완시켜줄 신호감지회로가 포함된 내부 부궤환 루프를 추가한 구 조를 연구하였다. 이 내부 루프는 외부 루프에 있는 루 프필터에 연결되고 부궤화 역할을 하여 제안된 위상고 정루프를 안정적으로 동작하도록 해준다.

다음에 나올 본론에서는 기존 위상고정루프의 문제점 을 지적하고 이를 개선하기 위해 새로운 구조를 제안할 예정이다. 제안된 구조의 이론과 동작개념에 대한 설명 을 하고 더불어 Spice 시뮬레이션을 통해 제안된 구조 가 시뮬레이션상 잘 동작하는지 확인할 것이다. 끝으로 앞선 내용을 요약하고 제안된 구조가 가지는 장점을 제 시하며 결론을 맺는다.

#### 2 본론

#### 2.1 기존 위상고정루프의 한계

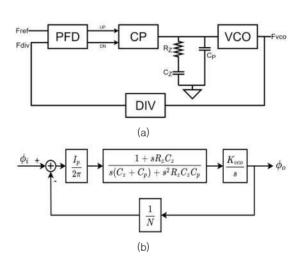

그림 1. (a) 기존 구조의 위상고정루프

(b) 기존 2차 루프 필터를 가지는 위상고정루프 선형 모델

Fig. 1. (a) Conventional PLL

(b) Linear model of conventional PLL with 2nd LF

그림 1은 기존 구조의 2차 루프필터를 가진 위상고정 루프의 구조와 전달 함수이다. 기존 위상고정루프의 전 달 함수는 다음과 같다.

$$\frac{\Phi_o}{\Phi_i} = \frac{\frac{I_p}{2\pi} \frac{1}{sCp} \frac{s+z}{s+p} \frac{K_{vco}}{s}}{1 + \frac{1}{N} \frac{I_p}{2\pi} \frac{s+z}{s+p} \frac{K_{vco}}{s}}$$

(1)

위상여유를 결정하는 z는  $\frac{1}{R_zC_z}$ 이며, p는  $\frac{1}{R_zC_n}$ 이다. 그러므로 기존 구조의 위상고정루프가 안정하게 동작하기 위해서는 칩의 상당한 면적을 차지하는 큰 커 패시터 용량이 필요하다. 작은 크기의 위상고정루프를 제작하기 위해서는 커패시터 용량을 가능한 작게 하는 것이 좋다. 그러나 커패시터가 작아질 경우 기존 구조의 위상고정루프에서는 위상 여유가 감소하여 불안정한 상 태가 되어 잡음과 지터(Jitter) 특성이 나빠지게 된다. 대 역폭을 줄이면 커패시터 용량을 줄일 수 있지만 기존 구 조의 2차 루프 필터를 가지는 위상고정루프에서 커패시 터 용량을 최소화하는 것에는 한계가 있다.

## 2.2 제안된 단일 커패시터 루프필터를 가진 극소형 위상 고정루프

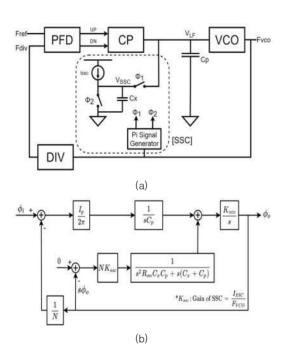

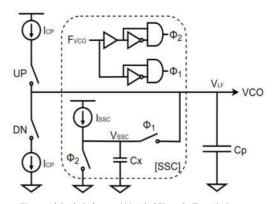

그림 2. (a) 신호감지회로를 도입한 제안된 위상고정루프

(b) 신호감지회로가 포함된 제안된 구조의 선형 모델

Fig. 2. (a) Proposed PLL with SSC

(b) Linear model of Proposed PLL with SSC

그림 2는 제안하는 단일 커패시터 루프필터를 극소형 위상고정루프이다. 위 모델 속 NKsc는 SSC가 포함된 루프의 샘플링 주파수가 외부 루프보다 N배 높다는 의 미이다. 기존 구조의 위상고정루프에서는 단일 커패시터 로 구성된 루프필터를 사용하면 위상여유가 "0"이 되어 전압제어발진기를 구동하는 루프필터 출력 전압(V<sub>LF</sub>)이 수렴되지 않는 동작 상태가 된다. 제안한 새로운 구조의 위상고정루프는 외부 부궤환 루프의 전압제어발진기의 출력 신호, 즉 위상고정루프의 출력 신호 변화를 감지하 는 신호감지회로가 포함된 내부 부궤화 루프을 도입하 여 안정하게 동작하도록 하였다. 아래 수식은 제안된 위 상고정루프 전달함수이다.

$$\frac{\Phi_{o}}{\Phi_{i}} = \frac{\frac{K_{vco}}{s} \frac{I_{p}}{2\pi} \frac{1}{s} \left(\frac{1}{C_{p}}\right)}{1 + \frac{1}{N} \frac{K_{vco}}{s} \frac{I_{p}}{2\pi} \frac{1}{s} \left(\frac{1}{C_{p}}\right) + K_{vco} \frac{NK_{ssc}}{s^{2}R_{on}C_{x}C_{p} + s\left(C_{p} + C_{x}\right)}}$$

(2)

$$H_{OL} = \frac{K_{vco}}{s} \left( \frac{I_p}{2\pi} \frac{1}{s C_p} \frac{1}{N} + \frac{N K_{ssc}}{s R_{on} C_x C_p + C_x + C_p} \right)$$

(3)

기존 구조의 전달 함수와 다르게 도입된 신호감지회 로에 의하여 분모에 또 하나의 변수가 나타난다. 이 변 수에 의하여 전달 함수와 위상여유가 달라지게 된다.

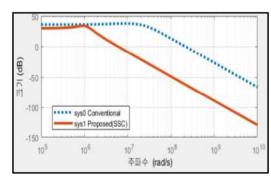

그림 3. 기존 구조와 제안된 구조의 전달 함수

Fig. 3. Conventional and Proposed transfer function

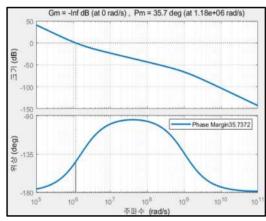

그림 3은 기존 구조와 제안된 구조 전달함수 보드도 이다. 수식(1)과 수식(2)를 통해 MATLAB 시뮬레이션을 진행하였다. 제안된 구조의 전달함수는 기존 구조의 전 달함수와 같은 감소 기울기 값을 보여주고 있다. 수식(3) 은 제안된 PLL의 열린 루프 선형 함수 수식이다. 그림 4를 통해 위상여유를 확인할 수 있다. 단일 커패시터 루 프필터를 사용하였지만 충분한 위상여유를 가질 수 있 다는 것을 보여주고 있다.

그림 4. 제안된 구조의 위상 변화도

Fig. 4. Phase gradient diagram of the proposed structure

#### 2.3 신호감지회로의 역할 및 동작

신호감지회로의 역할은 외부 루프에 부궤환 역할을하 여 하나의 커패시터로 구성된 루프필터로 이루어진 위 상고정루프를 안정적으로 동작하게 도와준다. 그림 2에 서 보듯이 제안하는 위상고정루프는 두 개의 부궤환 루 프로 이루어져 있다. ①외부 부궤환 루프(PFD→CP→LF →VCO→DIV→PFD)가 있고 ②내부 부궤환 루프(VCO →SSC→LF→VCO)로 구성되어 있다. 외부 부궤환 루프. 즉 기존 하나의 부궤환 루프로 위상고정루프가 하나의 커패시터로 구성된 루프필터를 가지게 되면 위상 여유 가 "0"이 되어 동작이 불안하여 전압제어발진기의 주파 수 출력이 매우 불안정하게 된다. 내부 부궤환 루프의 신호감지회로가 위상고정루프 출력 신호인 주파수 변화 를 감지하여 커패시터에 충전된 전하를 조절하여 안정 하게 동작한다.

그림 5. 신호감지회로, 외부 전하펌프와 루프필터 Fig. 5. Schematic of SSC, charge pump and loop filter

그림 5는 신호감지회로의 세부적인 구조다. 전압제어 발진기의 출력주파수를 받아 생성된 ∅1 신호는 외부 루 프필터 Cp에 있는 전하를 충전 혹은 방전시키고, Ø2신 호는 신호감지회로 Cx에 축적된 전하를 방전시키는 역 할을 한다.

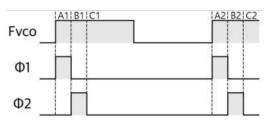

그림 6. 제어 신호 타이밍

Fig. 6. Control signal timing

그림 6은 신호감지회로의 타이밍도이다. 신호감지회 로의 동작은 시간상에서 3부분으로 나눌 수 있다. ①A1 일 때  $\phi$ 1 스위치가 닫히게 되므로  $C_X$ 에 축적된 전하량 에 따라 CP를 충전 혹은 방전하게 된다. ②B1에선 Ø1 스위치가 개방되고  $\emptyset$ 2 스위치가 닫혀서  $C_X$ 에 남은 전 하를 모두 방전하게 된다. ③C1에서 다음 A2까지 Ø1과 ∅2 스위치 모두 개방되어 있으므로 신호감지회로의 전 류원(Issc)으로부터 전하를 받아 Cx가 충전된다. 그리고 다시 A2에서 Cp의 전하를 충전 혹은 방전하므로 루프필 터 출력 전압을 조절할 수 있다.

위상고정루프의 출력 주파수가 상승하면 주기가 감소

하여 전류원 [ssc에 의해 Cx가 충전되는 시간이 짧아지 므로  $C_x$ 에 축적된 전하량이 감소한다. 그러므로 ∅1에 스위치가 닫히면 V<sub>LF</sub>의 전압을 감소시켜 위상고정루프 의 출력 주파수를 하강하도록 해준다. 내부 부궤환루프 가 외부 부궤화 루프에 대하여 부궤화 역할을 하여 전체 위상고정루프가 안정하게 동작하도록 해준다.

그림 7. 신호감지회로의 동작 개념도 Fig. 7. Operation concept diagram of SSC

신호감지회로의 역할은 루프필터 출력 전압 변화 크 기를 조절하는 것이다. 그림 7은 전압제어발진기 출력주 파수가 높아진 경우의 신호감지회로의 동작을 나타낸 개념도이다. UP 신호 구간 동안 루프필터 전압이 상승 한다. V<sub>LF</sub>(a) 는 신호감지회로가 없는 구조에서 루프필 터 출력 전압을 나타낸 것이다. UP 신호 구간 동안 전압 값이 상승하고 루프필터가 하나의 커패시터로 구성되어 전하가 방전되지 않아 기준 신호 한주기 동안 크기가 유 지된다. 신호감지회로 출력 전압 Vssc는 UP 신호에 따 른 전압값의 변화를 보여주고 있다. ∅2와 ∅1 신호 사 이의 시간이 감소하므로 크기가 감소한다. V<sub>LF</sub>(b)는 신 호감지회로가 있는 루프필터 Cp 출력전압을 나타낸 것 으로 루프필터의 전압이  $C_X$ 의 전압 즉,  $V_{SSC}$ 보다 클 경 우 신호감지회로에 내장된 커패시터 Cx로 루프필터의 전하가 방전된다. 그래서 V<sub>IF</sub>(b)는 UP 시간 동안 전압값 이 상승하다가 UP 신호가 사라지면 VLF(a)와는 다르게 루프필터 출력 전압이 감소하게 된다.

아래 수식은 전압제어발진기에서 나오는 출력주파수 의 한 주기당 발생하는 초과위상변위(excessive phase shift)의 수식이다.  $\Delta \phi_{\text{out}}$ 는 초과위상변위,  $K_{\text{vco}}$ 는 전압 발진기이득, ⊿V<sub>LF</sub>(t)는 시간에 따른 루프필터 전압값의 변화량을 의미한다.

$$\Delta \Phi_{out}(t) = K_{vco} \int \Delta V_{LF}(t) dt \quad (4)$$

수식 (4)를 통해  $V_{LF}$ 의 적분값 즉,  $V_{LF}$ 의 면적이 초과 위상변위의 크기를 결정하는 것을 알 수 있다. 한 주기 당 발생하는 초과위상변위가 클수록 위상고정루프의 동 작은 불안정하게 된다. 그러므로 그림 7의 V<sub>LF</sub>(b)처럼 신호감지회로를 추가하여  $\Delta V_{LF}(t)$ 의 적분면적을 줄이게 되면 초과위상변위도 작아지게 되어 위상고정루프가 안 정하게 동작할 수 있게 된다.

#### 2.4 시뮬레이션 결과

제안한 하나의 커패시터로 구성된 루프 필터를 가진 극소형 위상고정루프는 1.8V 0.18μm CMOS 공정 변 수를 사용하여 Spice 시뮬레이션을 진행하였다. 입력 주파수는 31.25MHz이며 출력 주파수는 1.0GHz이다. 시뮬레이션에 사용된 변수는 다음과 같다. 전하펌프 전 류와 신호감지회로 전류는 각각 Icp = 0.6uA와 Issc = 0.06uA이다. 커패시터 크기는 C<sub>X</sub> = 0.1pF, C<sub>P</sub> = 2.0pF이며 전압제어발진기의 기울기는 Kvco = 750MHz/V이다. 2.0pF 가량의 소형 커패시터는 매우 작은 전류만으로 동작이 제어가능하여 전하펌프의 전류 도 0.6uA로 줄여서 설계하였다.

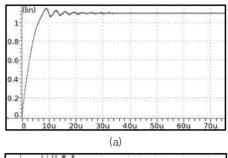

- 그림 8. (a) 루프 필터 출력 전압

- (b) 확대한 루프필터 출력 전압

- (c) 위상 고정 후 더 확대된 루프필터 출력 전압

- Fig. 8. (a) Loop filter output voltage

- (b) Enlarged loop filter output voltage

- (c) Further enlarged loop filter output voltage

그림8은 루프필터전압을 나타낸 그래프이다. 그림 8(a)와 (b)를 통해  $35.0\mu$ s에서 위상 고정이 됨을 알 수 있다. 그림 8(c)는 위상 고정 후 루프필터의 작은 크기의 커패시터가 전하 펌프의 UP/DN 전류의 조그마한 불일 치에도 큰 크기의 펄스가 나타남을 보여주고 있다. 이 펄스 형태의 파형은  $\Delta V_{\rm LF}$ 가 아주 작아서 지터 특성에 큰 영향을 미치지 못한다.

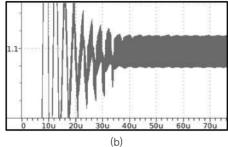

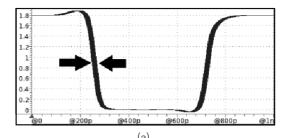

- 그림 9. (a) 기존 구조 전압제어발진기 출력 파형의 아이 다이어그램

- (b) 제안된 구조 전압제어발진기 출력 파형의 아이 다이어그램

- Fig. 9. (a) Eye diagram of the output waveform of the conventional structure voltage controlled oscillator

- (b) Eye diagram of the output waveform of the proposed structure voltage controlled oscillator

표 1. 기존 구조와 제안된 구조의 시뮬레이션 결과 비교 Table 1. Comparison of simulation results of conventional and proposed structures

|             | 기존 구조                     | 제안된 구조                        |

|-------------|---------------------------|-------------------------------|

|             | 150pF(C <sub>P</sub> )+15 | 2.0pF(C <sub>P</sub> )+0.1pF( |

| 커패시터        | $pF(C_Z)$                 | C <sub>X</sub> )              |

|             | $(R_Z = 1.7K\Omega)$      | =2.1pF                        |

| $I_{CP}$    | 500uA                     | 0.6uA                         |

| 위상여유        | 48.6°                     | 35.7°                         |

| 고정시간        | 5.0us                     | 35.0us                        |

| Peak-to-Pea | 90.0                      | 99.0                          |

| k Jitter    | 20.8ps                    | 22.8ps                        |

| RMS Jitter  | 4.04ps                    | 4.56ps                        |

|             |                           | 38.9mW+2.9m                   |

| 소모전력        | 45.0mW                    | W(SSC)                        |

|             |                           | =41.8mW                       |

위상고정루프의 크기가 아무리 작더라도 지터 특성이 좋지 않으면 사용할 수 없다. 표1에서 기존 구조와 제안된 구조의 시뮬레이션 결과값을 비교하였다. 기존 구조와 제안된 구조에서 각작 같은 구조, 같은 성능의 전압 제어발진기를 사용하였다. 제안된 구조에서는 RMS지터 크기가 약간 증가하였지만, 성능적 차이는 크지 않고 면적대비 성능은 오히려 좋아졌다. 그러므로 지터 특성을 크게 고려하지 않는 보급형 클록 생성기로 유용하게 사용할 수 있다. 제안된 구조에서 소모전력의 경우 전체구조에서 총 41.8mW를 소모하며, 새롭게 추가된 신호 감지회로는 2.9mW를 소모하였다. 기존구조와 비교하여 신호감지회로의 추가는 소모전력에 큰 영향을 주지 않는 것으로 나타났다.

#### 3. 결론

본 논문에서 제안하는 위상고정루프는 단일커패시터 루프필터를 가진 이중 부궤환 루프 구조이다. 신호감지 회로가 포함된 내부 부궤환 루프는 외부 부궤환 루프에 대하여 부궤환 역할을 하여 제안된 위상고정루프가 안 정적으로 동작하도록 해준다. 두 개의 내외부 부궤환 루프는 2.0pF 용량의 단일 커패시터 루프필터만으로도 안 정적인 동작이 가능하도록 해준다. 제안된 구조는 기존 구조보다 1/78 정도의 작은 커패시터값을 가짐에도 불구하고, 지터값은 10% 정도차이가 존재하며 소모전력은 10% 정도 감소하였다.

추후에는 제안된 위상고정루프 칩으로 제작하여 시뮬 레이션으로 예측된 성능을 검증하여 신호감지회로가 포함된 2개의 부궤환 루프를 가진 회로의 잠재성을 확인할수 있을 것이다. 이를 이용해 극소형 위상고정루프 설계가 가능함을 보여주며, 또한 커페시터를 칩 내부에 포함하여 집적화가 가능한 극소형 클록 신호 생성기로 사용될수 있다.

#### **REFERENCES**

[1] W. Chen, S. Ray, J. Bhadra, M. Abadir and L. Wang, "Challenges and Trends in Modern SoC Design Verification," IEEE Design &

- Test, vol. 34, no. 5, pp. 7-22, 2017.

- [2] Adesina, Naheem O., and Ashok Srivastava.

"Memristor-Based Loop Filter Design for Phase Locked Loop" Journal of Low Power Electronics and Applications, vol 9, no. 3, pp. 24-36, 2019.

- [3] H. S. Jang, Y. S. Choi, "An available capacitance increasing PLL with two voltage controlled oscillator gains." IEEK SD, vol. 51, no. 7, pp. 1508-1514, 2014.

- [4] Pang-Jung Liu, Chih-Yao Hsu and Yi-Hsiang Chang, "Techniques of Dual-Path Error Amplifier and Capacitor Multiplier for On-Chip Compensation and Soft-Start Function," IEEE Transactions on power electronics, vol. 30, no. 3, pp. 1403- 1410, 2015.

- [5] Pengfei Liao, Ping Luo, Weizhong Chen, Bo Zhang, "Embedded Advanced Capacitor Multiplier Compensation for Two-stage Amplifier with Large Capacitive Loads," Communications, Circuits and Systems (ICCCAS), vol. 2, pp. 362-365, 2013.

- [6] Y. S. Choi, G. H. Han, "An Extremely Small Size Multi-Loop Phase Locked Loop." JKIIECT, vol. 12, no. 1, pp. 1-6, 2019.

- [7] J. -H. Seol, K. Choo, D. Blaauw, D. Sylvester and T. Jang, "A 67-fsrms Jitter, 130 dBc/Hz In-Band Phase Noise, -256-dB FoM Reference Oversampling Digital PLL With Proportional Path Timing Control," IEEE Solid-State Circuits Letters, vol. 3, pp. 430-433, 2020.

- [8] L. Wu, T. Burger, P. Schönle and Q. Huang, "A Power-Efficient Fractional-N DPLL With Phase Error Quantized in Fully Differential-Voltage Domain," IEEE Journal of Solid-State Circuits, vol. 56, no. 4, pp. 1254-1264, 2021.

- [9] K. Grout and J. Kitchen, "A Dividerless Ring Oscillator PLL With 250fs Integrated Jitter Using Sampled Lowpass Filter," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 11, pp. 2337-2341, 2020.

- [10] J. Sharma and H. Krishnaswamy, "A

dividerless reference-sampling RF PLL with -253.5dBc jitter FOM and -67dBc reference spurs", IEEE International Solid-State Circuits Conference. Digest of Technical Papers, pp. 258-259, 2018.

### 저자약력

### 박 경 석 (Kyung-Seok Park)

#### [학생회원]

- 2021년 부경대학교 전자공학과 학사 졸업.

- 2021년 ~ 현재 부경대학교 전자 공학과 석사과정

〈관심분야〉PLL 설계

## 최 영 식 (Young-Shig Choi)

#### [정회원]

- 1982년 경북대학교 전자공학과 학사 졸업.

- 1986년 Texas A&M University 전자공학과 석사 졸업.

- 1993년 Arizona StateUniversity 박사 졸업.

- 1987년 ~ 1999년 현대전자(현 SK Hynix) 책임연구원

- 2003년 ~ 현재 부경대학교 전자공 학과 교수

〈관심분야〉PLL, DLL 설계