https://doi.org/10.6113/TKPE.2020.25.5.412

# GaN MOSFET을 이용한 고밀도, 고효율 48V 버스용 3-출력 Buck Converter 설계

이상민1, 이승환†

# A High Efficiency, High Power-Density GaN-based Triple-Output 48V Buck Converter Design

Sangmin Lee<sup>1</sup> and Seung-Hwan Lee<sup>†</sup>

#### **Abstract**

In this study, a 70 W buck converter using GaN metal-oxide-semiconductor field-effect transistor (MOSFET) is developed. This converter exhibits over 97 % efficiency, high power density, and 48 V-to-12 V/1.2 V/1 V (triple output). Three gate drivers and six GaN MOSFETs are placed in a 1 cm² area to enhance power density and heat dissipation capacity. The theoretical switching and conduction losses of the GaN MOSFETs are calculated. Inductances, capacitances, and resistances for the output filters of the three buck converters are determined to achieve the desired current, voltage ripples, and efficiency. An equivalent circuit model for the thermal analysis of the proposed triple-output buck converter is presented. The junction temperatures of the GaN MOSFETs are estimated using the thermal model. Circuit operation and temperature analysis are evaluated using a circuit simulation tool and the finite element analysis results. An experimental test bed is built to evaluate the proposed design. The estimated switch and heat sink temperatures coincide well with the measured results. The designed buck converter has 130 W/in³ power density and 97.6 % efficiency.

Key words: GaN, Buck converter, PMIC (Power Management Integrated Circuit)

#### 1. 서 론

최근 클라우드, 빅데이터 및 인공지능 등의 영향으로 데이터가 대량으로 생성됨에 따라 이를 관리할 수 있는데이터 센터의 중요성이 급증하고 있다. 대량의 데이터를 처리하기 위해 높은 전력 효율 및 공간 효율성을 가진 데이터 센터가 요구된다. 이에 따라 프로세서의 요구전력과 집적도가 증가하고 있으며, 고전력 및 고밀도 컨버터의 필요성이 대두되고 있다<sup>11</sup>. 하지만 기존의 12V전원 시스템을 이용할 경우 부하의 증가는 많은 저항손실로 이어져 효율 감소를 야기한다. 이러한 전력 변환

및 공급 손실을 줄이기 위해 구글(Google) 등에서는 48  $V_{DC}$  버스의 데이터센터용 아키텍처를 제안하였다 $^{[2]}$ . 구 글에 따르면 48V의 공급 전원을 사용할 경우 12V 전원 시스템에 비해 공급 손실을 16배 줄일 수 있으며, 전력 변환 손실을 30%가량 감소시킬 수 있는 장점이 있다. 이러한 장점 때문에 높은 효율과 전력 밀도를 가지는 48V 버스용 컨버터에 대한 다양한 연구가 이루어지고 있다<sup>[3]-[7]</sup>. Samuel과 Yan-Fei는 12개의 (MOSFET) 을 이용한 48V-to-12V 컨버터의 토폴로지 를 제안하였다<sup>[1]</sup>. 그 결과 97.2% 효율과 2.5kW/in<sup>3</sup> 의 전력 밀도를 가지는 강압형 컨버터를 설계할 수 있었다. 하지만 이런 고밀도 컨버터 설계에 있어 필수적인 발열 및 방열 구조 설계에 대한 논의는 없었다. Osvaldo, Salvatore. Stefano, 그리고 48V-to-12V 공진형 컨버터를 제안하였다<sup>[3]</sup>. 그 결과 약 95.2%의 효율을 가지는 컨버터를 설계할 수 있었으며, 약 500W의 출력에서 컨버터의 동작 온도도 제시하였다. 하지만 컨버터의 방열 구조 설계에 대한 분석은 진행하 지 않았다. Ratul과 Hanh-Phuc는 데이터 서버용 48V-to-

Paper number: TKPE-2020-25-5-10

Print ISSN: 1229–2214 Online ISSN: 2288–6281

<sup>&</sup>lt;sup>†</sup> Corresponding author: seunghlee16@uos.ac.kr, Dept. of Electrical & Computer Engineering, University of Seoul Tel: +82-2-6490-2350

<sup>&</sup>lt;sup>1</sup> Dept. of Electrical & Computer Engineering, University of Seoul

Manuscript received Aug. 10, 2020; revised Aug. 25, 2020; accepted Aug. 28, 2020

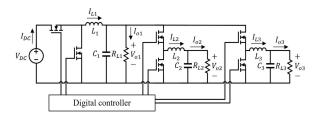

Fig. 1. An equivalent circuit of the triple-output 48 V buck converter.

1V Dual-Phase Multi-Inductor Hybrid(DP-MIH) 컨버터를 제안하였다 $^{[7]}$ . 그 결과 90.9%의 효율을 가지며,  $400W/in^3$ 의 전력 밀도를 가지는 컨버터를 설계할 수 있었다. 하지만 컨버터의 발열 및 방열에 대한 언급은 하지 않았다.

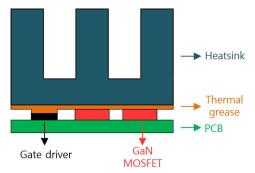

본 논문에서는 GaN(Gallium nitride) eHEMT 타입의 모스펫을 이용한 70W급 48V-to-12V/1.2V/1V의 3-출력 Buck 컨버터의 회로, 고밀도 배치 및 이를 위한 방열 구조 설계안을 제시한다. 3-출력 컨버터는 서버 전원용 12V와 데이터 처리를 위한 프로세서의 전원용 1.2V 및 1V를 공급할 수 있도록 48V-to-12V Buck 컨버터와 12V-to-1.2V, 12V-to-1V Buck 컨버터가 직렬 연결된 (Cascade) 구조로 설계하였다<sup>[8]</sup>. 높은 전력 밀도를 얻기 위해 컨버터 구동을 위한 3개의 half-bridge 드라이브용 게이트 드라이버와 6개의 GaN 모스펫을 1cm²의 면적 안에 배치하였다. 회로 해석을 통해 3-출력 Buck 컨버 터의 스위칭 손실 및 도통 손실을 예측했다. 주파수별 손실 비교를 통해 적정 운전 주파수를 정했다. PCB 기 판을 포함한 열 저항 등가회로를 도출하고, 계산된 컨버 터 손실을 이용해, 70W의 정격 출력 시 GaN 스위치 접 합부(Junction) 의 최고 온도가 110℃ 이내가 되도록 방 열 구조를 설계했다. 설계된 회로의 동작과 방열 구조는 시뮬레이션을 통해 검증했다. 또한 설계된 3-출력 컨버 터를 실제 제작하고, 회로의 동작 및 방열판 온도를 실 험을 통해 검증하였다.

# 2. 48V 버스용 3-출력 Buck 컨버터의 파라메터 선정

#### 2.1 스위치 및 수동 소자 선정 및 배치

그림 1은 본 논문에서 사용된 48V 버스용 Buck 컨버터의 등가회로를 나타낸다. 제시된 DC/DC 컨버터는 세개의 Buck 컨버터로 구성되어 있어 한 개의 48V 입력전압과 세 개의 출력 전압(12V, 1.2V, 1V)을 가진다. 외부 입력 전원과 연결된 첫 번째 Buck 컨버터는 48V의입력 전압을 받아 12V의 출력 전압을 내보낸다. 두 번째 및 세 번째 Buck 컨버터는 첫 번째 Buck 컨버터의출력 전압인 12V를 입력 전압으로 받아 각각 1.2V와1V의 출력 전압을 내보낸다. 각 Buck 컨버터는 최대 5 A의 출력 전류를 내보낼 수 있도록 설계되었다. 그림 1의

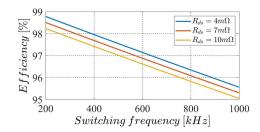

Fig. 2. A theoretical efficiency of converter as the  $R_{ds}(on)$  and switching frequency are increased.

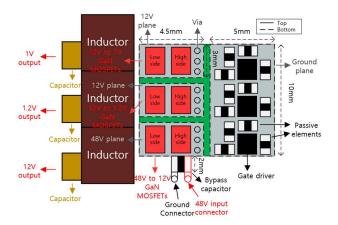

Fig. 3. A top view of the 3-output buck converter.

$R_{L1}, R_{L2}, R_{L3}$  는 각 컨버터 출력 부하의 등가 저항을 나타내고 있다. 모스펫의 전도손실 등가저항  $R_{ds}(on)$ 이 커질수록 도통 손실이 증가하고, 이는 효율 감소로 이어 진다. 모스펫에서만 손실이 발생한다고 가정하였을 때, 전부하 시 스위칭 주파수와  $R_{ds}(on)$ 에 따른 이론적인 컨버터의 효율 그래프가 그림 2에 제시되어 있다. 그래 프에서 알 수 있듯이, 1MHz까지의 스위칭 주파수 구간 에서 95% 이상의 컨버터 효율을 얻기 위해서  $10 \text{m}\Omega$  이 하의  $R_{ds}(on)$ 을 가지는 모스펫을 사용해야 한다. 제안 하는 컨버터의 스위치로는 시판되는 GaN 모스펫 중 입 력 전압의 2배인 100V의 drain-to-source 내전압을 가 지며 최대 16A의 전류 용량과 7m $\Omega$ 의  $R_{ds}(on)$ 을 가지 는 1.5mm×2.5mm 크기의 Efficient Power Conversion (EPC) 사의 epc2045를 선정하였다<sup>[9]</sup>. 게이트 드라이버는 Texas Instruments 사의 half-bridge GaN 모스펫용 드 라이버인 LM5113을 사용하였다<sup>[10]</sup>. 고밀도 회로를 구현 하기 위해 LM5113의 경우 DSBGA 패키지를 사용하였 다. 스위치 6개 및 3개의 게이트 드라이버의 배치는 그 림 3과 같이 했다. 시스템의 집적도를 높이기 위해 1cm<sup>2</sup>의 면적 안에 모두 배치하였다.

Buck 컨버터의 high-side GaN 모스펫의 이론적인 스위칭 손실 및 전도 손실은 각각 (1), (2)을 통해 도출할수 있으며, GaN 모스펫의 총 손실이 스위칭 손실 및 전도 손실의 합과 같다고 가정하면 총 손실은 (3)처럼 표현할 수 있다<sup>[11]</sup>.

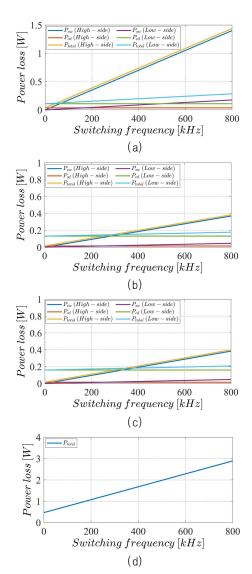

Fig. 4. Theoretical switching and conduction losses of GaN MOSFET (epc2045) of (a) 12 V output, (b) 1.2 V output, (c) 1 V output buck converters, and (d) theoretical total power loss of GaN MOSFETs.

$$P_{SW\_GaN} = \frac{V_{DC}I_o(t_r + t_f)f_{sw}}{2} \tag{1}$$

$$P_{CD,GaN} = DI_o^2 R_{ds}(on) \tag{2}$$

$$P_{D_{-}GaN} = P_{SW_{-}GaN} + P_{CD_{-}GaN}$$

(3)

여기서  $P_{SW\_GaN}$ ,  $P_{CD\_GaN}$  및  $P_{D\_GaN}$ 은 각각 GaN 모스펫에서 발생하는 스위칭 손실, 전도 손실 및 총 손실을 의미한다.  $t_r$  및  $t_f$ 는 각각 GaN 모스펫의 상승 및 하강 시간을 의미한다. 상승 시간은 GaN 모스펫이 단락될 때 드레인과 소스 사이의 전압이 입력 전압의 10%에서 90%까지 증가하는 시간을 의미하며, 하강 시간은 GaN 모스펫이 도통될 때 드레인과 소스 사이의 전압이 입력 전압의 90%에서 10%까지 감소하는 시간을 의미한다.  $f_{sw}$ 는 GaN 모스펫의 스위칭 주파수를, D는 듀티

TABLE I CIRCUIT PARAMETERS OF TRIPLE-OUTPUT BUCK CONVERTER

| Parameter           | Value   | Parameter | Value  |

|---------------------|---------|-----------|--------|

| $f_{sw}$            | 400 kHz | $L_3$     | 4.7 μH |

| $\overline{}V_{DC}$ | 48 V    | $C_1$     | 133 µF |

| $\overline{V_{o1}}$ | 12 V    | $C_2$     | 100 μF |

| $\overline{V_{o2}}$ | 1.2 V   | $C_3$     | 100 µF |

| $\overline{V_{o3}}$ | 1 V     | $R_{L1}$  | 2.63 Ω |

| $L_1$               | 4.7 μH  | $R_{L2}$  | 0.25 Ω |

| $L_2$               | 4.7 μH  | $R_{L3}$  | 0.2 Ω  |

사이클을 의미한다. 전부하 시, 식 (1)~(3)을 이용해 계 산한 GaN 모스펫에서 발생하는 이론적인 스위칭 손실 및 도통 손실의 그래프가 그림 4(a), (b), (c)에 각각 제 시되어 있다. 파란색과 빨간색 선은 각각 윗상 스위치의 스위칭 손실과 도통 손실을 의미하며, 보라색과 초록색 선은 각각 아랫상 스위치의 스위칭 손실과 도통 손실을 의미한다. 노란색 선과 하늘색 선은 각각 윗상과 아랫상 스위치의 스위칭 손실과 도통 손실의 합을 나타낸다. 전 부하 시 세 Buck 컨버터의 출력 전류는 모두 5A로 동 일하며, 그림 4(a)에서 알 수 있듯이 12V 출력 Buck 컨 버터의 경우 1.2V, 1V 출력 Buck 컨버터보다 입력 전압 이 4배 크기 때문에 스위칭 손실 또한 4배 큰 것을 확 인할 수 있다. Buck 컨버터의 아랫상 스위치는 턴 온 시점에서 영전압 스위칭(ZVS) 이 가능하기 때문에 윗상 스위치보다 스위칭 손실이 작다. 하지만 세 Buck 컨버 터 모두 아랫상 스위치의 도통 손실이 윗상 스위치보다 큰 것을 확인할 수 있는데, 이는 아랫상 스위치의 듀티 사이클이 윗상보다 크기 때문이다. 스위칭 주파수가 클 수록 동일한 인덕턴스 및 커패시턴스에 대해 인덕터 전 류 및 출력 전압의 리플이 작아진다. 따라서 스위칭 주 파수가 클수록 컨버터의 소형화에 유리하다. 따라서 그 림 2에 제시된 것처럼 97.5% 이상의 컨버터 효율을 얻 을 수 있고, 컨버터의 소형화에 가장 유리한 400kHz의 스위칭 주파수를 선정하였다.

Buck 컨버터 출력부의 인덕터와 커패시터도 전체 시스템의 물리적인 크기와 연관이 있으므로, 시스템의 고밀도화를 위해 적절한 설계가 필요하다. Buck 컨버터는 전류 연속 모드(Continuous current mode)에서 동작하도록 설계되었으며, 동작 중 부하 변동이 없기 때문에 정격 부하에서 인덕터의 평균 전류는 5A가 된다. 전류의 리플이 평균 전류의 50%가 넘지 않도록 설계하기위해 4.5μH 이상의 인덕턴스를 가지며, 15mm×15mm 가넘지 않고 낮은 DC 저항을 가지는 인덕터가 요구되었다. 이에 13mm×12.8mm의 크기를 가지며 7mΩ의 직류저항(DC resistance)을 가지는 Würth Elektronik 사의 7443551470 인덕터를 선정하였다. 커패시턴스는 평균 출력 전압으로부터 최대 1% 미만의 전압 리플을 가지

Fig. 5. A simulated steady-state waveform of (a) 12 V, (b) 1.2 V, and (c) 1 V output buck converters.

도록 선정되었다. 또한 Buck 컨버터의 높은 효율을 위해 낮은 등가 직렬 저항(Equivalent series resistance)을 가지는 고주파용 필름 커패시터 및 탄탈륨 커패시터 를 사용하였다. 컨버터에 사용된 회로 파라메터는 표 1에 정리되어 있다.

다음으로 선정된 스위치, 인덕터 및 커패시터의 PCB 상의 배치에 대해 고려했다. 입력 전원과 스위치 사이의 거리는 3mm가 되도록 배치하였다. 그림 3에 제시된 것 처럼 입력 전원은 2mm의 두께를 가지는 바이패스 커패 시터를 거쳐 스위치에 인가되기 때문이다. 또한 PCB 패 턴의 저항 성분에 의한 손실의 최소화를 위해서 Buck 컨버터의 인덕터와 스위치와의 거리는 최대한 가까워야 한다. 하지만 인덕터의 면적이 스위치 면적에 비해 약 44배 크기 때문에 3개의 Buck 컨버터에 각 인덕터를 바 로 붙도록 배치하기에는 어려움이 존재하였다. 따라서 Buck 컨버터와 인덕터가 최대한의 밀도를 가지며 Buck 컨버터와 인덕터의 거리가 최소한으로 되도록 배치하였 다. 그 결과 12V 및 1.2V 출력 Buck 컨버터의 인덕터는 스위치와의 거리가 2mm가 되도록 배치하였으며, 1V 출 력 Buck 컨버터의 인덕터는 스위치와 4mm의 거리를 가지도록 배치하였다. 커패시터는 인덕터와 바로 붙도록 배치하여 손실을 최소화했다. 위에서 바라본 3-출력 Buck 컨버터의 배치가 그림 3에 제시되어 있다.

#### 2.2 설계된 회로의 시뮬레이션

앞서 설계한 것처럼 세 개의 Buck 컨버터는 모두 출력 전압의 리플이 최대 1% 이내의 값을 가지도록 설계

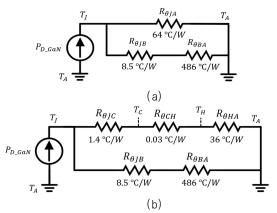

Fig. 6. Equivalent thermal resistance of the converter (a) without heatsink and (b) with heatsink.

Fig. 7. A cross-sectional view of the converter.

되었다. 그림 5(a), (b), (c)는 각각 정상 상태에서의 12V, 1.2V, 1V 출력 Buck 컨버터의 출력 전압 및 전류를 나타낸다. 출력 전압 파형에서 알 수 있듯이, 세 개의 Buck 컨버터 모두 설계 조건을 만족하는 것을 확인할 수 있다.

#### 2.3 설계된 회로의 이론적 방열 해석

제안하는 컨버터에서 발생하는 이론적 손실의 75% 이상이 GaN 모스펫에서 발생하며, 6개의 GaN 모스펫이 1cm<sup>2</sup>의 면적 안에 배치되어 있기 때문에 회로의 이론적 방열 해석은 GaN 모스펫에만 한정했다. 제안하는 컨버 터에 사용된 인덕터의 직류 저항은 7mΩ이며 평균 전류 는 5A이기 때문에 이론적으로 약 0.175W의 손실이 발 생하지만, 이는 6개의 GaN 모스펫에서 발생하는 손실의 약 10% 정도이다. 하지만 인덕터의 체적은 GaN 모스펫 에 비해 약 400배 크므로 방열에 어려움이 없었다. 커패 시터에서 발생하는 손실 또한 GaN 모스펫에 비해 매우 작지만 약 80배 큰 체적을 가지므로 방열에 어려움이 없었다. 그림 6(a)는 열전도 그리스(Grease) 및 방열판이 없을 경우 GaN 모스펫의 열 저항을 이용한 등가회로를 보여준다. 그림 6(a)의 등가회로는 키르히호프의 전류 법칙(Kirchhoff's current law) 을 이용해 (4)처럼 표현할 수 있다.

$$T_{J} = T_{A} + P_{D\_GaN} \times \frac{R_{\theta JA}(R_{\theta JB} + R_{\theta BA})}{R_{\theta JA} + R_{\theta JB} + R_{\theta BA}} \tag{4} \label{eq:4}$$

여기서  $T_J$ 와  $T_A$ 는 각각 GaN 모스펫의 접합부의 온도

Fig. 8. Equivalent thermal resistance circuits of the PCB  $(R_{\theta BA})$  from the (a) 12 V output and (b) 1.2 V and 1 V output GaN MOSFETs to the ambient.

와 주위 대기 온도를 나타낸다.  $R_{\theta JA}$ ,  $R_{\theta JB}$ ,  $R_{\theta BA}$ 는 각각 GaN 모스펫의 접합부로부터 주위 대기까지의 열 저항, GaN 모스펫의 접합부로부터 PCB까지의 열 저항, 그리고 GaN 모스펫이 부착되어 있는 PCB의 열 저항이다. 여기서  $R_{\theta JA}$ 와  $R_{\theta JB}$ 는 제조사의 데이터시트에 제시되어 있다 $^{[9]}$ . 하지만  $R_{\theta BA}$ 는 PCB의 패턴 및 구조에따라 달라지는 값이므로, 추가적인 분석이 필요하다.

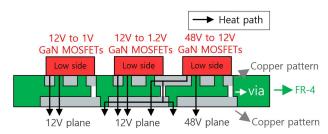

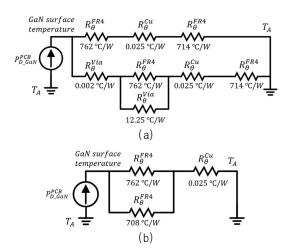

PCB의 열 저항을 추정하려면 PCB의 레이아웃에 따 른 GaN 모스펫에서 발생하는 열의 이동 경로를 파악해 야 한다. 그림 3에 제시된 컨버터의 상부 모습에서 실선 은 PCB의 상부 면에 배치된 소자임을 의미하고, 점선은 하부 면에 레이아웃된 구리층을 의미한다. 하부 면의 좌 측 레이어들은 비아를 통해 상부 면 GaN 모스펫의 드 레인과 연결되어 있다. 즉, 48V 입력 전압과 같은 노드 를 공유하는 한 개의 레이어와 12V 전압과 같은 노드를 공유하는 두 개의 레이어로 구성되어 있다. 또한, 하부 우측 레이어는 접지와 같은 노드를 공유하고 있다. 컨버 터에 흐르는 전류는 접지, 12V 노드, 48V 노드 순으로 크다. 구리 패턴 저항에 의한 손실로 발생하는 발열은 흐르는 전류의 제곱에 비례하므로, 노드에 흐르는 전류 크기의 순으로 하부 레이어의 면적을 다르게 제작하였 다. 하부 면의 레이어들은 방열 성능을 높이기 위해 페 인트를 도포하지 않고 구리층을 공기 중에 노출시켜 놓 았다. 전부하 시 출력 전류가 입력 전류보다 크기 때문 에 GaN 모스펫에서 발생하는 대부분의 열은 Buck 컨버 터의 출력 노드에서 발생한다. 또한 GaN 모스펫에서 발 생하는 열의 대부분은 열 저항이 작은 비아를 통해 PCB 하부로 방출된다. 이러한 점을 감안하였을 때, 그 림 3의 구조를 가지는 Buck 컨버터의 GaN 모스펫에서 발생하는 주된 열의 흐름은 그림 7과 같이 표현될 수 있다. 그림 7에 제시된 것처럼 12V 출력 Buck 컨버터의 GaN 모스펫에서 발생하는 열은 주로 열저항이 낮은 구리

Fig. 9. A cross-sectional view of the converter with heatsink.

패턴과 비아를 통해 PCB 하부 면의 구리층으로 방출된다. 하지만 GaN 모스펫과 FR-4가 맞닿아 있기 때문에 FR-4로도 전도에 의한 열전달이 이루어진다. 따라서 GaN 모스펫의 표면에서부터 총 2개의 열 흐름이 병렬 연결되어있다고 볼 수 있다. 하지만 그림 7에서 알 수 있듯이, PCB 하부 면에 1.2V 및 1V 구리층이 없기 때문에 1.2V 및 1V 출력 Buck 컨버터의 GaN 모스펫에서 발생하는 열 흐름은 12V 출력 Buck 컨버터의 GaN 모스펫과 다른 양상을 갖는다<sup>[12]</sup>. 1.2V 및 1V로 강압하는 Buck 컨버터의 GaN 모스펫과 다른 양상을 갖는다<sup>[12]</sup>. 1.2V 및 1V로 강압하는 Buck 컨버터의 GaN 모스펫은 비아를 통해서 열을 발산하지 못하고, 대부분의 열은 FR-4를 거쳐 PCB의 하부로 전달되기 때문에 GaN 모스펫의 표면으로부터 한 개의 열 흐름을 가진다고 볼 수 있다. 열 저항은 물질의열 전도율과 면적 및 두께를 이용해 도출할 수 있으며,열 저항을 구하는 식이 (5)에 제시되어 있다<sup>[13]</sup>.

$$R_{\theta} = \frac{L}{kA} \tag{5}$$

여기서  $R_{\theta}$ 와 k는 각각 열 저항과 물질의 열전도율을 의미하며, L과 A는 각각 레이어의 두께와 면적을 의미 한다. 그림 7의 열 흐름 경로를 고려한 PCB의 등가 열 저항 회로가 그림 8에 제시되어 있다.  $P_{D\ GaN}^{PCB}$ 는 PCB 로 전달되는 GaN 모스펫의 전력을 의미한다. 주위 대기 온도를 22°C라고 가정할 때, GaN 모스펫의 동작 최대 온도는 150°C이므로 GaN 모스펫의 접합부가 동작 최대 온도를 초과하지 않고 소모할 수 있는 최대 소모 전력 은 약 2.26W가 된다. 이는 6개의 GaN 모스펫에서 발생 하는 손실 전력이 2.26W를 넘어서는 안된다는 것을 의 미한다. 그림 4(d)에서 알 수 있듯이, 컨버터가 400kHz 의 스위칭 주파수로 동작할 경우 6개의 GaN 모스펫에 서 발생하는 손실 전력의 합은 약 1.7W이다. 그림 6(a) 의 열 저항 등가 회로를 이용해 GaN 모스펫의 접합부 온도를 구해보면 약 118°C로 GaN 모스펫의 접합부온도 가 동작 최대 온도를 초과하지 않는 것을 알 수 있다.

Buck 컨버터의 상부 면에 방열판을 부착하였을 때 열 저항 등가회로는 그림 6(b)에 제시되어 있다. 그림 6(b) 의 회로를 KCL을 이용해 수식으로 표현하면 (6)과 같다.

Fig. 10. Simulated temperature of (a) the surface and (b) the cross-section of the converter without heatsink.

$$\begin{split} T_{J} &= T_{A} + P_{D_{-}GaN} \\ &\times \frac{(R_{\theta JB} + R_{\theta BA})(R_{\theta JC} + R_{\theta CH} + R_{\theta HA})}{R_{\theta JB} + R_{\theta BA} + R_{\theta JC} + R_{\theta CH} + R_{\theta HA}} \end{split} \tag{6}$$

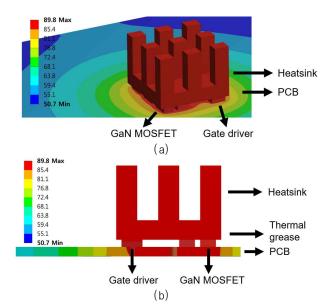

여기서  $R_{\theta,IC}$ ,  $R_{\theta,CH}$ ,  $R_{\theta,HA}$ 는 각각 GaN 모스펫의 접 합부로부터 GaN 모스펫의 케이스까지의 열 저항, 열전 도 그리스의 열저항, 그리고 방열판의 열 저항이다.  $R_{\theta,IC}$ 와  $R_{\theta,HA}$ 는 제조사의 데이터시트를 통해 결정되는 값이다. Buck 컨버터의 게이트 드라이버 및 GaN 모스 펫이 1cm²의 면적 안에 밀집되어 있는 구조이므로, 그 림 9에 제시된 것처럼 제작의 편의성을 위해 게이트 드 라이버 및 GaN 모스펫이 1cm<sup>2</sup>의 표면 면적을 가지는 방열판을 공유하도록 배치하였다. 다만, 게이트 드라이 버와 GaN 모스펫 간의 높이 차이를 보상해주기 위해 열전도 그리스를 두껍게 부착하였다. 36°C/W의 열 저항 을 가지는 방열판을 부착하는 경우, GaN 모스펫의 접합 부가 동작 최대 온도를 초과하지 않고 소모할 수 있는 최대 소모 전력은 최대 2.75W가 된다. 결과적으로 22°C 의 대기 온도에서 GaN 모스펫의 접합부 온도는 89.32°C, 방열판의 표면 온도는 86.8°C가 도출되었다.

#### 3. 유한 해석 요소를 이용한 방열 분석 결과

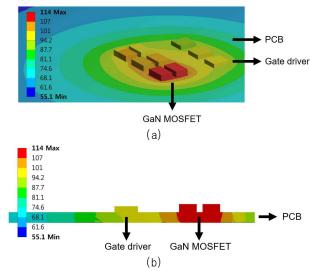

3-출력 벅 컨버터의 방열 구조 성능을 검증하기 위해 시뮬레이션 튤인 ANSYS Mechanical에 그림 3에 제시된 Buck 컨버터의 구조적인 모습을 구현하고, 회로 시뮬레이션을 통해 얻은 GaN 모스펫의 손실 전력을 이용하여 손실 전력에 따른 GaN 모스펫의 발열량과 정상상태에서의 GaN 모스펫의 접합부 온도를 확인하였다. 22℃의 주위 대기 온도와 10W/m²℃ 의 자연 대류 상황을 가정하였으며, 방열판의 재질은 AL 6063-T5를 사용하였다. 그림 10(a)는 열전도 그리스와 방열판이 없을

Fig. 11. Simulated temperature of (a) the surface and (b) the cross-section of the converter with heatsink.

경우 컨버터의 표면 온도를 보여준다. 12V 출력 Buck 컨버터의 GaN 모스펫에서 가장 많은 열이 발생하였으 며. 표면 온도가 최고 114°C까지 상승하는 것을 확인할 수 있다. 그림 10(b)는 컨버터 단면의 열 분포를 보여준 다. GaN 모스펫의 접합부 또한 최고 114°C까지 상승하 는 것을 확인할 수 있다. 이는 이론적으로 계산한 접합 부 온도 118°C와 거의 일치한다. 그림 11(a)은 정상 상 태에서의 Buck 컨버터의 표면 온도 분포를 보여준다. GaN 모스펫 접합부 및 방열판 표면의 최대 온도는 모 두 89.8°C로, 식 (6)를 통해 계산한 방열판 표면의 이론 적인 값인 86.8°C와 오차율 3.3%로 거의 일치하는 것을 확인할 수 있다. 그림 11(b)는 Buck 컨버터 단면의 온도 분포를 보여준다. GaN 모스펫의 접합부 온도 또한 89.8°C까지 상승하는 것을 확인할 수 있다. 이는 이론적 인 GaN 모스펫의 정상 상태 온도인 89.32°C와 거의 일 치한다. 시뮬레이션 결과 GaN 모스펫의 접합부 및 표면 온도, 그리고 방열판의 온도가 거의 동일함을 알 수 있 다. 이는 컨버터의 체적이 작고 방열판의 열 전도도가 높아 정상 상태에서는 열이 고르게 분포하기 때문이다.

#### 4. 실험 결과

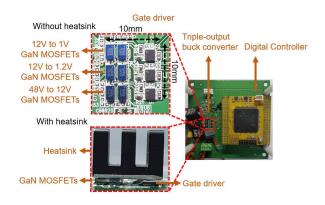

#### 4.1 효율

설계된 Buck 컨버터의 성능을 검증하기 위해 그림 12 와 같이 실험 세트를 제작하였다. 그림 12에서 알 수 있 듯이, 세 개의 게이트 드라이버 및 여섯 개의 GaN 모스 펫은 1cm² 크기의 정사각형 안에 배치하였다. 또한 인덕터와 커패시터를 포함한 모든 회로는 10.5cm² 안에 배치하여 설계된 Buck 컨버터는 방열판을 포함하지 않을 경우 178W/in³의 전력밀도를 가졌으며, 방열판을 포함할 경우 130W/in³의 전력밀도를 가진다. 제작된 실험

Fig. 12. Photo of a test-bed.

세트는 표 1과 값과 동일한 파라메터를 가진다. PCB는 총 8mm의 두께를 가지는 2층 기판으로 만들어졌으며, 동박 두께는 1oz로 제작하였다.

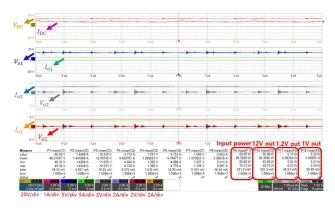

정격 부하를 연결하였을 때 정상 상태에서의 입력 및 출력의 전압과 전류의 파형이 그림 13에 제시되어 있다. 파형에서 알 수 있듯이, 입력 전력은 69.52W, 출력 전력은 67.9W로 약 97.6%의 효율을 얻을 수 있었다. 총 손실은 약 1.62W였으며 12V, 1.2V, 1V 출력 Buck 컨버터의 GaN 모스펫에서 각각 0.75W, 0.28W, 0.28W의 손실이 발생하였다. 인덕터 및 커패시터에서 발생하는 손실은 각각 90mW, 5mW였다.

#### 4.2 방열 성능

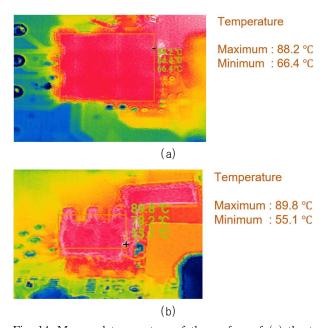

48V 버스용 DC/DC 컨버터의 방열 구조 성능을 검증하기 위해 22°C의 대기 온도 환경에서 컨버터 온도가 포화 상태에 도달할 때까지 동작시킨 뒤, 방열판의 표면 온도를 측정하였다. 그림 14(a)는 상부에서 바라본 방열판의 온도 분포를 보여준다. 실험 결과에서 알 수 있듯이, 방열판 상부의 최대 온도는 88.2°C였으며, 이는 이론및 시뮬레이션 값인 86.8°C, 89.8°C와 비슷한 결과를 보여준다. 컨버터에서 발생한 열이 PCB를 통해 주변으로 전달되기 때문에, 컨버터 주변 PCB 온도가 최소 66.4℃인 것을 확인할 수 있다. 그림 14(b)는 정면에서 바라본 컨버터의 방열판 온도를 보여준다. 방열판 하부에서 방열판의 최대 온도가 89.8°C인 것을 확인할 수 있는데,이는 가장 많은 손실이 발생하는 12V 출력 Buck 컨버터의 GaN 모스펫과 맞닿아 있기 때문이다.

#### 4.3 전력 밀도

본 연구에서 제안한 시스템은 최종적으로 130W/in³의 전력 밀도를 가지는 것으로 나타났다. GaN 모스펫을 이용해 스위치의 집적도를 높였지만 더 높은 전력밀도의 컨버터 설계를 위해 인덕터의 크기를 줄일 필요가 있다. 동일한 스위치를 사용하였을 때, 스위칭 주파수를 1MHz로 높일 경우 이론적인 GaN 모스펫의 총 손실은 (1)~(3)에 의해 3.5W가 된다. 계산된 손실에 따라 GaN 모스펫의 접합부 온도는 그림 6(b)에 의해 약 143°C로

Fig. 13. A measured steady-state waveform of the converter.

Fig. 14. Measured temperature of the surface of (a) the top and (b) the front of the heatsink.

GaN 모스펫의 최대 동작 온도를 초과하지 않으며, 동일한 인덕터 전류 리플 조건을 만족하기 위해 1.8μH의 인덕터가 요구된다. 상용 인덕터들을 이용할 경우, 실험에 사용된 인덕터 체적의 약 64%의 체적(10.1mm×10.8mm)을 가지며 5mΩ의 직류 저항을 가지는 1.8μH의 IHLP4040DZER1R8M11 인덕터를 사용할 수 있으며, 약 473W/in³의 전력 밀도를 가지는 컨버터를 설계할 수 있다. 다만, 스위칭 주파수 증가에 따라 스위치 손실이증가하며, 컨버터의 예상 효율은 94.9%가 도출된다. 따라서 효율과 전력밀도간의 적절한 trade-off 가 필요할 것으로 보인다.

#### 5. 결 론

체적당 손실이 클수록 시간당 발열이 크기 때문에 고 효율, 고밀도 컨버터 설계의 경우 열에 의한 파괴를 막 기 위해 방열 구조가 필수적으로 고려되어야 한다. 본

논문에서는 고전력밀도, 고효율을 가지기 위한 GaN 모 스펫 기반 70W급 48V-to-12V/1.2V/1V의 3-출력 컨버 터의 소자 선정 및 방열 구조 설계안을 제시하였다. 스 위칭 손실 및 도통 손실을 계산하여 97% 이상의 컨버 터 효율을 얻을 수 있는 스위치와 스위칭 주파수를 선 정하였으며, 평균 전류의 50% 미만의 인덕터 전류 리플 및 평균 출력 전압의 1% 미만의 출력 전압 리플을 가 지도록 인덕터 및 커패시터를 선정하였다. 또한 고전력 밀도를 위해 3개의 게이트 드라이버와 6개의 GaN 모스 펫을 1cm<sup>2</sup>의 면적 안에 배치하였으며, 컨버터의 구조 및 PCB 레이아웃에 따른 등가 열 저항 회로를 도출하 여 이론적인 스위치 손실을 계산하였다. 계산된 손실에 따른 방열판의 표면 온도 및 GaN 모스펫의 접합부 온 도를 이론적으로 계산하고, 70W의 정격 출력 시 GaN 모스펫 접합부의 최고 온도가 110℃ 이내가 되도록 방 열 구조를 설계하였다. 설계된 방열 구조는 ANSYS Mechanical 시뮬레이션 및 실험을 통해 검증하였다. 실 험 결과, 컨버터는 97.6%의 효율과 130W/in3의 전력 밀 도를 가졌으며, 방열판의 표면 온도 오차는 최대 3.3% 였다.

본 연구는 2020년도 산업통상자원부 및 산업기술평가관리원(KEIT)의 연구비 지원을 받아 수행한 연구 과제입니다. (No. 20003734)

### References

- [1] S. Webb and Y. Liu, "A zero inductor-voltage 48V to 12V / 70A converter for data centers with 99.1% peak efficiency and 2.5kW / power density," in 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1858–1865, 2020.

- [2] M. H. Ahmed, F. C. Lee, and Q. Li, "LLC converter with integrated magnetics application for 48V rack architecture in future data centers," in *IEEE Conference on Power Electronics and Renewable Energy*, pp. 437–443, 2019.

- [3] O. Zambetti, M. Colombo, S. D'Angelo, S. Saggini, and R. Rizzolatti, "48V to 12V isolated resonant converter with digital controller," in *IEEE Appl. Power Electron. Conf. Expo. (APEC)*, pp. 315–321, Mar. 2017.

- [4] K. Hata, Y. Yamauchi, T. Sai, T. Sakurai, and M. Takamiya, "48V-to-12V dual-path hybrid DC-DC converter," in 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 2279-2284, 2020.

- [5] M. Choi and D. K. Jeong, "A 92.8%-peak-efficiency 60A 48V-to-1V 3-level half-bridge DC-DC converter with balanced voltage on a flying capacitor," in 2020 IEEE International Solid-State Circuits Conference (ISSCC), pp. 296-298, Feb. 2020.

- [6] M. Salato, "Re-architecting 48V power systems with a novel non-isolated bus converter," in 2015 IEEE International Telecommunications Energy Conference (INTELEC), pp. 1-4, Oct. 2016.

- [7] R. Das and H. P. Le, "A regulated 48V-to-1V/100A 90.9%-efficient hybrid converter for POL applications in data centers and telecommunication systems," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1997-2001, 2019.

- [8] Z. Yu et al., "An 800MHz 320mW 16-core processor with message-passing and shared-memory inter-core communication mechanisms," in 2012 IEEE International Solid-State Circuits Conference, pp. 64-65, 2012.

- [9] Efficient Power Conversion, "EPC2045-enhanced mode power transistor," EPC2045 datasheet, Mar. 2020.

- [10] Texas Instruments, "LM5113 5A, 100V half-bridge gate driver for enhancement mode GaN FETs," LM5113 Datasheet, Apr. 2013.

- [11] R. W. Erickson and D. Maksimović, Fundamentals of power electronics, 2nd ed. New York, USA: Springer-Verlag, 2001.

- [12] T. Yang et al., "An integrated liquid metal thermal switch for active thermal management of electronics," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, Vol. 9, No. 12, pp. 2341–2351, Dec. 2019.

- [13] R. K. Shah and D. P. Sekuli, Fundamentals of heat exchanger design, New Jersey, USA: John Wiley & Sons, 2003.

## 이상민(李相旻)

2018년 서울시립대 전자전기컴퓨터공학부 및 경영학부 졸업.  $2018년 \sim 현재$  동 대학원 전자전기컴퓨터공학과 석·박통합과정.

#### 이승환(李承桓)

2004년 서울대 기계항공공학부 및 전기전자 컴퓨터공학부 졸업. 2008년 동 대학원 전기 전자컴퓨터공학부 졸업(석사). 2013년 미국 위스콘신 주립대학 기계공학과(WEMPEC) 졸 업(공박). 2013년~2016년 한국철도기술연구

\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_원 선임연구원. 2016년~현재 서울시립대 전자전기컴퓨터공학 부 부교수. 당 학회 학술위원.