ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 19-03-44

296

# 고속 인터페이스를 위한 원단누화 보상 기술 동향

# Far-End Crosstalk Compensation for High-Speed Interface

이 원 병\*, 공 배 선\*\*

Won-Byoung Lee\*, Bai-Sun Kong\*\*

#### **Abstract**

In a multi-channel single-ended system, the far-end crosstalk (FEXT) due to mutual inductance and mutual capacitance between two adjacent channels critically limit the bandwidth. FEXT causes crosstalk-induced jitter (CIJ) and crosstalk-induced glitch (CIG) which leads to timing margin and voltage margin degradations, respectively. Therefore, FEXT must be compensated in order to increase eye opening and achieve high data-rate. It can be compensated in transmitter by controlling the timing of the data or reshaping the waveform of the signal. Also, FEXT can be compensated in receiver by generating mimicked FEXT using high-pass filter. In this paper, recent techniques to compensate FEXT are investigated, with discussions of their pros and cons.

#### 요 약

멀티채널 단일 종단(single-ended) 환경에서 채널 사이의 상호인덕턴스 및 상호캐패시턴스에 의한 원단누화 현상(FEXT) 은 결정적으로 채널의 대역폭 감소를 일으킨다. 원단누화에 의해 누화-유발 지터(CIJ)와 누화-유발 글리치(CIG)가 생기며 이들은 각각 타이밍 마진 감소와 전압 마진 감소를 일으킨다. 따라서 아이 오프닝 증가와 높은 데이터 전송속도를 얻기 위해서는 원단누화 현상을 보상해야 한다. 원단누화 보상은 송신단에서 타이밍 조절 또는 파형 변형을 통해 보상할 수 있다. 또한, 수신단에서 고역-필터를 사용하여 유사 원단누화 잡음을 만들어 보상하는 방법도 있다. 본 논문에서는 원단누화 보상의최근 기술 동향을 소개하며, 이들의 장점과 단점을 논의한다.

Key words: Single-ended signaling, multi-channel, far-end crosstalk, jitter, transceiver, equalizer

# I . 서론

최근 고속 인터페이스에서는 높은 대역폭을 얻고 자 단일-종단 신호(single-ended signaling) 기법을 사용하여 신호를 전달한다. 하지만 단일-종단 신호 기법은 잡음에 매우 취약하다는 단점을 가지며, 멀 티채널 환경에서는 특히 누화(crosstalk) 잡음이 성 능을 제한하게 된다[1]. 누화 잡음이란 인접한 두 채널 사이의 단위 길이 당 상호 인덕턴스 및 상호 캐패시턴스에 의해 발생하며, 유발되는 방향에 따라 신호의 진행 방향과 같은 방향으로 유발되는 원단누화(far-end crosstalk, FEXT)와 신호의 진행 방향의 반대 방향으로 유발되는 근단누화(near-end crosstalk, NEXT)로 나뉜다. 이 중, 고속 인터페이

E-mail: bskong@skku.edu Tel: +82-31-299-4616

Acknowledgment

This work was supported by the Basic Research Program through the National Research Foundation of Korea funded by the Ministry of Education under Grant NRF-2016R1D1A1B03933605.

Manuscript received Sep. 5, 2019; revised Sep. 27, 2019; accepted Sep. 27, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Department of Semiconductor and Display Engineering, Sungkyunkwan University

<sup>★</sup> Corresponding author

스에서는 신호 전달 시간과 비례하여 잡음의 크기가 커지는 원단누화가 수신단의 신호를 치명적으로 왜곡한다. 원단누화로 인해 피유도(victim) 채널에는 두 채널 사이 천이 모드에 따라 방향이 바뀌는 누화-유발 지터(crosstalk-induced Jitter, CIJ)와 유도 채널(aggressor)의 천이 방향에 따라 극성이 좌우되는 누화-유발 글리치(crosstalk-induced Glitch, CIG)가 있다. CIJ와 CIG는 수신단 신호의아이 오프닝을 감소시켜 대역폭 향상의 걸림돌이되므로 FEXT를 보상하여 아이 마진을 증가시켜야한다. 본 논문은 이 문제를 해결하기 위해 송신단및 수신단에 적용된 기술들과, 이들의 장점 및 단점을 소개하고자 한다.

#### II. FEXT 보상 기법

#### 1. 송신단(TX)에서의 FEXT 보상

송신단의 경우 데이터의 정보를 미리 알 수 있으므로 이를 이용하여 FEXT를 보상할 수 있다. 먼저, 신호의 타이밍을 조절하여 CIJ의 영향을 완화하거나 유발되지 않는 환경을 만들어 FEXT를 보상할 수 있다. 또한, 신호의 천이 모드에 따라 신호의 파형을 변화시켜 보상하거나, 신호의 듀티 사이클을 감지하여 보상하는 방법이 있다. 본 절에서는 위 방법들을 사용하여 송신단에서 FEXT를 보상하는 기술들을 논의한다.

#### 가. 데이터 타이밍 제어를 통한 보상

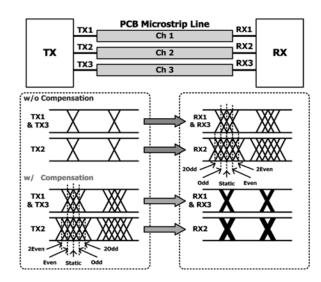

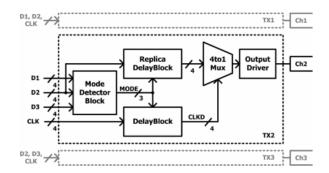

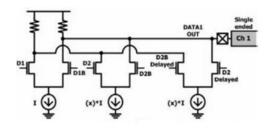

그림 1은 데이터 타이밍 제어를 이용하여 FEXT를 보상하는 기법을 나타낸다[2]. 3-bit의 데이터가들어올 때 인접한 채널과의 천이 모드에 따라 CIJ로 인해 RX2에는 5가지의 서로 다른 타이밍의 데이터를 받게 된다. 이 때, 송신단에서 데이터 타이밍을 조절함으로써 CIJ를 제거할 수 있다. 인덕티브 커플링이 우세한 채널 환경에서는, 천이 모드가 even 모드일 경우 CIJ의 영향에 의해 수신단의 천이 타이밍은 뒤로 밀리게 되므로 타이밍 제어를 통해 even 모드의 송신 타이밍을 해당 양만큼 당김으로써 보상한다. Odd 모드의 경우 반대로 조정할 수있으며, 만약 2-odd 또는 2-even의 경우에는 타이밍 제어 양을 2배 늘림으로써 보상할 수 있다. 그림 2는 데이터 타이밍 제어 기법의 블록선도(block diagram)를 나타낸 그림이다. D1, D2, 그리고 D3

Fig. 1. CIJ compensation with data timing control. 그림 1. 데이터 타이밍 제어를 통한 CIJ 보상

Fig 2. Block diagram of data timing control scheme 그림 2. 데이터 타이밍 제어 기법의 블록선도

가 각각 모드 감지 블록(mode detection block)의 입력으로 인가되며, 5가지의 모드가 3-bit 신호로지연 블록(delay block)에 전달된다. 그 결과 모드를 반영한 지연 클락인 *CLKD*가 데이터를 모드에따라 다른 타이밍에 출력하게 된다. 하지만 타이밍제어 기법의 경우, 지연 회로가 추가적으로 필요할뿐 아니라, 천이 모드 감지기 역시 필요하므로 송신단의 전력 및 면적의 낭비를 야기한다.

#### 나. 스태거드(staggered) 동작을 통한 보상

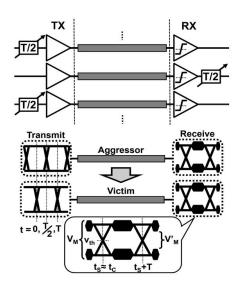

그림 3은 스태거드 동작을 사용하여 CIJ를 제거하는 방법을 나타낸다[3]. 앞의 방법에서 살펴본 바와 같이, CIJ는 인접한 두 채널에서 동시에 천이가일어날 경우 발생한다. 따라서 인접한 두 신호의경우 천이 타이밍을 서로 T/2 만큼 차이를 발생시켜 CIJ의 유발을 피할 수 있다. 그림 3과 같이 송신단에서 한 채널씩 건너뛰며 신호를 T/2 만큼 지연

Fig. 3. CIJ cancellation using staggered scheme. 그림 3. 스태거드 기법을 사용한 CIJ 제거 방법

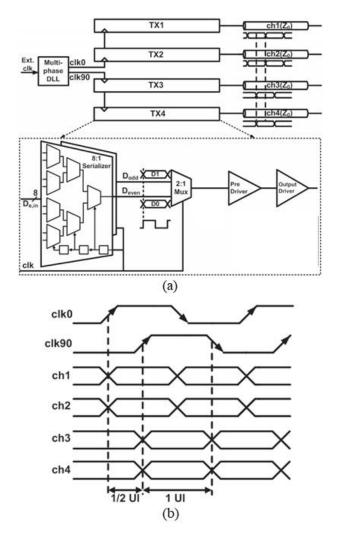

Fig. 4. (a) Block diagram of pair-wise staggering transmitter (b) Timing diagram.

그림 4. (a) 페어-와이즈 스태거링 송신단의 블록 선도, (b) 타이밍 다이아그램

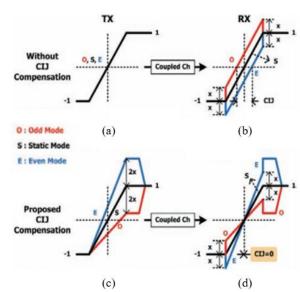

Fig. 5. CIJ compensation with slew-rate control (a) TX signal without compensation, (b) RX signal without compensation, (c) TX signal with compensation, (d) RX signal with compensation.

그림 5. 슬루율 제어를 통한 CIJ 보상 (a) 보상 전 송신단 신호, (b) 보상 전 수신단 신호, (c) 보상 후 송신단 신호, (d) 보상 후 수신단 신호

시킴으로써 인접한 채널끼리 천이 타이밍을 다르게 구현한다. 스태거드 기법의 경우 모드 감지기와 같은 복잡한 회로 없이 구현 가능한 장점이 있지만, CIJ 대신 CIG의 형태로 인접 채널에 간섭을 일으키게 되므로 이를 위한 추가적인 보상이 필요하다는 한계가 있다.

또한, 앞에서 소개한 스태거링을 변형시킨 페어-와이즈 스태거링 기법(pair-wise staggering) 도연구된 바 있다[4]. 페어-와이즈 스태거링은 두 채널씩 스태거링을 시키는 방법으로, 그림 4(a)와 4(b)는 각각 페어-와이즈 스태거링 송신단의 블록선도와 파형을 나타낸다. 페어-와이즈 스태거링의경우 ch2의 관점에서 ch1로부터 CIJ가 유발되는대신 CIG의 영향은 ch3으로부터만 받게 되므로, FEXT의 피크 파워(peak power)를 절반으로 줄일수 있는 장점이 있다. 하지만 역시 CIJ와 CIG를 근본적으로 제거하는 방법이 아니므로, 이들을 보상하는 기법이 추가적으로 필요하다.

다. 파형 변형(waveform shaping)을 통한 보상

신호의 천이 모드에 따라 파형 모양을 적절히 변형하여 CIJ를 보상할 수도 있다. 그림 5는 슬루율을 조정하여 CIJ를 보상하는 기법으로써 [5], 그림

Fig. 6. Slew-rate control circuit. 그림 6. 슬루율을 제어하는 회로

5(a)와 같이 CIJ 보상을 하지 않은 경우에는 그림 5(b)처럼 모드에 따라 천이 타이밍이 당겨지거나 밀리게 된다. 따라서 그림 5(c)와 같이 슬루율을 변 형시켜 천이 응답을 변화시킴으로써 그림 5(d)처럼 지터에 의한 효과를 보상할 수 있다. 그림 6은 슬루율 제어 회로를 나타내며, 주 드라이버(main driver)로 D1/D1B 신호가 인가될 때 이 신호에 천이 크기가 x배 작아진 D2와 D2B\_Delayed 신호가 더해짐으 로써 FEXT를 보상하는 슬루율 제어를 구현할 수 있다. 본 방법은 D2를 통해 직접 슬루율을 조정하 므로 모드 감지 블록 없이 천이 모드에 따라 보상 할 수 있는 장점이 있다. 하지만 본 방법은 슬루율 을 조정하여 수신단의 신호에 수직 방향으로 왜곡 이 생길 수 있으므로 수직 아이-오프닝을 감소시 키는 문제점이 있다. 또한 슬루율 제어 회로가 추 가로 필요하므로 송신단의 면적과 전력 부담이 커 지는 단점을 가지고 있다.

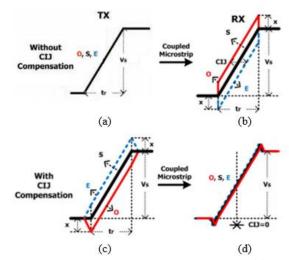

한편, 신호의 천이 모드에 따라 정제된 사각 파형 을 신호의 천이 타이밍에 더함으로써 CIJ를 보상할 수 있으며, 그림 7 은 이러한 파형 추가를 통한 CIJ 보상 기법을 나타낸다[6]. 그림 7(a)와 7(b)를 통해 신호의 천이 모드에 따라 수신단에서 FEXT의 양 만큼 왜곡이 되며, 이를 보상해주기 위해 그림 7(c) 와 같이 사각 파형을 천이 모드에 따라 신호에 추 가할 수 있다. 그 결과 그림 7(d)와 같이 천이 타이 밍이 맞춰짐으로써 CIJ로 인한 효과를 줄인다. 사 각 파형은 그림 6과 유사한 회로로 구현할 수 있으 며, 이 기술 역시 모드 감지 블록 없이 천이 모드에 따라 보상할 수 있는 장점이 있으며, 뿐만 아니라, 슬루율 제어 기법과 달리 아이-오프닝을 감소시키 지 않는 장점이 있다. 하지만 실제 유발되는 FEXT 의 모양은 완벽한 사각 파형이 아니므로 정밀한 보 상에 한계가 있다. 또한, 사각 파형을 발생시키는 파형생성기는 신호를 당기거나 밀어야 하므로 이

Fig. 7. CIJ compensation with waveform addition (a) TX signal without compensation, (b) RX signal without compensation, (c) TX signal with compensation, (d) RX signal with compensation.

그림 7. 파형 추가를 통한 CJ 보상 방법의 파형 (a) 보상 전 송신단 신호, (b) 보상 전 수신단 신호, (c) 보상 후 송신단 신호, (d) 보상 후 수신단 신호

에 맞게 조정된 클락을 인가해야 하므로, 비교적 복잡한 회로가 추가되어야 하는 단점이 있다.

라. 듀티 사이클(Duty Cycle) 감지를 통한 보상

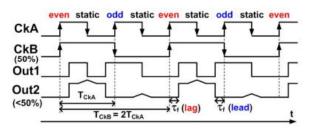

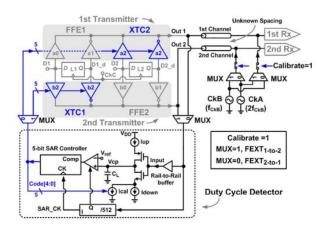

그림 8은 클락의 듀티 사이클 감지를 통해 FEXT를 보상하는 방법을 나타낸다[7]. 그림에서 보다시피, CkA와 CkA의 절반의 주파수를 가지는 CkB의클락 사이에 발생하는 천이 모드에 따라 Out1과 Out2의 듀티 사이클에 왜곡이 생기며, 이러한 왜곡을 통해 FEXT로 인한 지터의 양을 감지하여 Out2를 감지한 양만큼 당기거나 밀어 보상할 수 있다. 그림 9는 듀티 사이클 감지 기법의 회로를 나타낸다. 채널의 수신단 쪽에서 Calibrate 신호에 따라 CkA와 CkB의 클락이 송신단 쪽으로 전달되며, 이때 FEXT로 인한 지터의 양이 듀티 사이클 감지기

Fig. 8. Timing diagram for duty cycle detection. 그림 8. 듀티 사이클 감지 기법의 타이밍 다이아그램

Fig. 9. Circuit for duty cycle detection scheme. 그림 9. 듀티 사이클 감지 기법의 회로

(Duty Cycle Detector) 회로에 의해 FEXT양이 감지된다. 만약 FEXT에 의해 듀티 사이클이 50% 미만의 신호가 듀티 사이클 감지기의 입력으로 들어간다면, CL의 충전량이 증가하게 되며 Vcp가 증가하며, 그 결과 생성된 5-bit의 코드가 a2 또는 b2로 전달되어 FEXT를 보상할 수 있다.

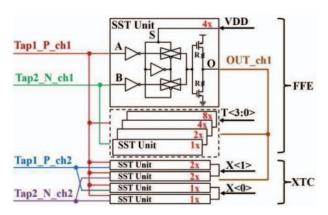

Fig. 10. Duty cycle detection in SST driver. 그림 10. 듀티 사이클 감지형 SST 드라이버에의 응용

그림 10은 듀티 사이클 감지 기법을 Source-Series Terminated(SST) 드라이버에 응용한 예를 나타낸다 [8]. SST 드라이버를 사용함으로써 보다 전력을 줄이며, 병렬로 연결된 SST 드라이버를 통해 프리-앰퍼시스(pre-emphasis) 역할의 Feed-Forward Equalizer (FFE)와 인접 채널로부터 유발되는 FEXT를 보상하는 XTC를 구현할 수 있다. 그림 10의 아래 4개의 SST 드라이버에서 듀티 사이클 감지 기법을 사용하며, X<0:1>을 통해 calibration 된 결과 ch2의 FEXT를 보상할 수 있다. 하지만 이와 같은 듀티사이클 감지 기법의 경우 CkA와 CkB의 클락이 메

인 클락과 별개로 필요하므로 오버헤드가 증가하며, 정밀한 calibration이 이루어져야 하므로 PVT variation 및 잡음에 강하게 만들어야 한다.

#### 2. 수신단(RX)에서의 FEXT 보상

수신단에서는 FEXT에 의해 왜곡된 신호를 직접 보상할 수 있는데, 이는 주로 고역 필터(high-pass filter)를 사용한다. 유도 채널로부터 피유도 채널에 가해지는 FEXT의 정보를 반영하여 유사 FEXT 신호를 고역 필터를 통해 만들 수 있으며, 이를 피 유도 채널로부터 빼 줌으로써 피유도 채널의 FEXT 를 보상할 수 있다.

#### 가. 채널 출력 단에서의 보상

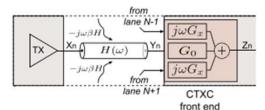

그림 11은 채널 출력 단에서 FEXT를 보상하는 방법을 나타낸다[9]. 멀티채널 환경에서 인접한 채널인 N-1번째 채널과 N+1번째 채널로부터 유발된 FEXT가 N번째 채널의 성능을 저하시키므로, 채널출력단에서 누화 제거 회로인 Crosstalk Canceller (CTXC) 회로를 통해 FEXT를 보상한다. 그림 12는 고역 필터를 사용하여 설계된 CTXC 회로를 나타낸다. 두 개의 고역 필터를 사용하여 위쪽 유발채널인 Vin[n-1]과 아래쪽 유발채널인 Vin[n+1]로부터의 FEXT를 모두 보상할 수 있으며, Vout 단에서 FEXT의 양만큼 해당하는 전류가 빠지는 형태로 보상이 이루어진다. 이 방법은 유도 채널로부

Fig. 11. FEXT compensation at channel output using CTXC block.

그림 11. CTXC 블록을 활용한 채널 출력에서의 FEXT 보상 기법

Fig. 12. Circuit for CTXC block. 그림 12. CTXC 블록의 회로

터 고역 필터를 통해 형성된 유사 FEXT 신호를 피유도 채널에 직접 보상하므로 수신단 보상에 비해 보다 정밀한 장점을 가지고 있다. 하지만, 인접하는 유발 채널들이 고역 필터와 직접 연결됨을 감안하면, 임피던스 매칭이 까다롭다는 단점이 있다. 또한, 전류-모드(current-mode) 구조인 관계로 전력 소모가 클 수 있다는 한계가 있다.

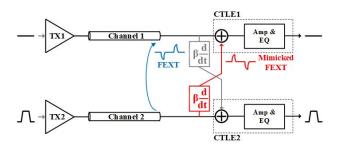

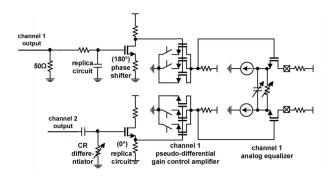

나. Continuous-time linear equalizer 단에서의 보상 그림 13은 수신단에서 고역 필터를 사용하여 Continuous-time linear equalizer (CTLE) 단에서 FEXT를 보상하는 기법을 나타낸다 [10]. 그림에서 보는 바와 같이, channel 1과 channel 2 사이에서 주고받는 FEXT는 미분기를 통해 유도 채널 (channel 2)로부터 형성된 유사 FEXT 신호가 피유도 채널(channel 1)과 합쳐지게 되어 왜곡을 받지 않은 출력 파형을 얻을 수 있다. 그림 14는 본방법의 구체적인 회로 구현을 나타내고 있다. 피유도 채널(channel 1)의 신호와 고역 필터를 거친 유도 채널(channel 2)의 신호가 증폭기에서 합쳐지며, 증폭기의 출력은 Amp & EQ 블록을 통해 보상된 파형이 최종 출력으로 나오게 된다. 이 방법 역시

Fig. 13. FEXT compensation at CTLE using HPF. 그림 13. CTLE 단에서의 HPF를 활용한 FEXT 보상

Fig. 14. Circuit for FEXT compensation at CTLE. 그림 14. CTLE 단에서의 FEXT 보상 회로

Fig. 15. FEXT compensation at DFE (a) Block diagram, (b) Principle of FEXT cancellation.

그림 15. DFE 단에서의 FEXT 보상 (a) 블록선도, (b) FEXT 제거 원리

Fig. 16. Circuit for FEXT compensation at DFE. 그림 16. DFE 단에서의 FEXT 보상 회로

유도 채널로부터 FEXT 정보를 직접 받아 피유도 채널에 직접 보상해줌으로써 보다 정밀한 보상이 가능하다. 그러나 유도 채널과 피유도 채널의 타이 밍을 맞춰주기 위해 복사 회로가 추가적으로 필요하며, 이는 CTLE 전 단인 채널 아웃픗에 위치하는 관계로 임피던스 부정합에 의해 반사 손실이 생길수 있다.

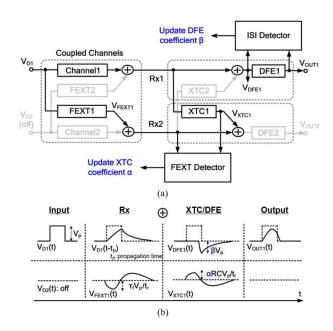

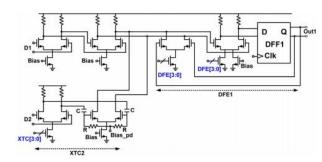

# 다. Decision-feedback equalizer 단에서의 보상

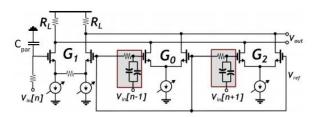

그림 15(a)는 수신단의 Decision-feedback equalizer (DFE)에서의 FEXT 보상 방법의 블록선도를 나타내며, 그림 15(b)는 본 방법의 보상 원리를 파형을 통해 나타낸다[11]. 채널 1로부터 채널 2로 유발되는  $V_{FEXT}$ 에 의해 RX2의 입력 단에 왜곡이 생기게

Table 1. Comparison of FEXT compensation schemes.

| 丑 1. | . FEXT | 보상 기 | l법들의 | 성능 | 비교 |

|------|--------|------|------|----|----|

|------|--------|------|------|----|----|

| Reference              | 09' JSSC<br>[2] | 18' ELEX<br>[4] | 10' CICC<br>[5] | 12' JSSC<br>[6] | 13' JSSC<br>[7] | 15' CICC<br>[8]  | 18' JSSC<br>[9]     | 11' JSSC<br>[10] | 13' JSSC<br>[11] |

|------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|---------------------|------------------|------------------|

| Process                | 180nm           | 65nm            | 180nm           | 130nm           | 65nm            | 65nm             | 32nm                | 130nm            | 65nm             |

| XTC type               | TX DTC          | TX PWS          | TX SRC          | TX<br>WA        | TX DCD          | TX SST<br>w/ DCD | RX HPF<br>@ ch. out | RX HPF<br>@ CTLE | RX HPF<br>@ DFE  |

| Number of channels     | 3               | 4               | 2               | 2               | 2               | 4                | 8                   | 2                | 2                |

| Channel Attenuation    | N/A             | N/A             | N/A             | -5.0dB          | -5.9dB          | N/A              | -30.0dB             | -9.0dB           | -14.3dB          |

| Data-rate              | 4.0Gb/s         | 6.0Gb/s         | 5.0Gb/s         | 7.2Gb/s         | 7.5Gb/s         | 20.0Gb/s         | 7.0Gb/s             | 5.0Gb/s          | 7.5Gb/s          |

| Supply                 | 1.8V            | N/A             | 1.8V            | 1.2V            | 1.2V            | 1.2V             | 1.0V                | 1.2V             | 1.2V             |

| Power(pJ/bit/lane)     | 28.4            | N/A             | 11.5            | 4.5             | 1.8             | 0.9              | 8.0                 | 2.4              | 3.5              |

| Area(mm <sup>2</sup> ) | 0.70            | N/A             | 0.08            | 0.06            | 0.03            | 0.05             | 0.01                | 0.03             | 0.03             |

된다. 이때 고역 필터로 구성된 XTC1 회로에 의해 유사 FEXT 신호인  $V_{XTCI}$  신호가 생성되며, DFE 내부에서  $V_{XTCI}$  신호와  $V_{FEXTI}$  신호가 더해져 FEXT의 영향을 줄인다. 그림 16은 수신단의 DFE 단에서의 FEXT 보상 회로를 나타낸다. 유도 신호 인 D2는 증폭기와 고역 필터를 거쳐 피유도 신호 인 D1의 DFE 회로의 탭으로 연결된다. 그 결과, D1 신호에 유도된 FEXT 신호는 탭에 의해 제거 된다. 이 방법 역시 유도 신호로부터 유사 FEXT 신호를 직접 만들어 제거한다는 점에서 정확도가 높지만, 두 채널 신호의 타이밍을 맞추기 위해 전 치 증폭기(pre-amplifier)가 필요하다는 단점이 있 다. 또한, 고역 필터가 DFE단의 탭 형태로 구현되 어야 하므로 DFE의 면적이 증가한다. 표 1은 지금 까지 검토한 FEXT 보상 기법들의 성능을 비교하 여 정리한 결과이다.

#### Ⅲ. 결론

본 논문은 송신단 또는 수신단에서의 여러 가지 FEXT 보상 기술을 소개하였다. 효율적인 FEXT 보상은 보다 높은 데이터 전송 속도를 제공함으로 써 차세대 메모리 인터페이스 설계에 결정적인 역할을 할 것이므로 지속적인 연구를 통한 기술 발전이 필요하다.

# References

[1] S. Lee et al., "A 5 Gb/s Single-Ended Parallel

Receiver With Adaptive Crosstalk–Induced Jitter Cancellation," in *IEEE JSSC*, vol.48, no.9, pp. 2118–2127, 2013. DOI: 10.1109/JSSC.2013.2264618 [2] H. Jung *et al.*, "A 4 Gb/s 3-bit Parallel Transmitter With the Crosstalk–Induced Jitter Compensation Using TX Data Timing Control," in *IEEE JSSC*, vol.44, no.11, pp.2891–2900, 2009. DOI: 10.1109/JSSC.2009.2028917

[3] K. Sham *et al.*, "I/O Staggering for Low-Power Jitter Reduction," *2008 38th EMC*, Amsterdam, pp.1226–1229. 2008.

DOI: 10.1109/EUMC.2008.4751682

[4] Ahn, Jeong-Keun et al., (2018). Pair-wise staggering transmitter for single-ended parallel signaling. IEICE ELEX. 15.

DOI: 10.1587/elex.15.20171238.

[5] H. Jung *et al.*, "A slew-rate controlled transmitter to compensate for the crosstalk- induced jitter of coupled microstrip lines," *IEEE CICC 2010*, San Jose, CA, pp.1-4, 2010.

DOI: 10.1109/CICC.2010.5617597

[6] H. Jung *et al.*, "A Transmitter to Compensate for Crosstalk–Induced Jitter by Subtracting a Rectangular Crosstalk Waveform From Data Signal During the Data Transition Time in Coupled Microstrip Lines," in *IEEE JSSC*, vol.47, no.9, pp.2068–2079, 2012.

DOI: 10.1109/JSSC.2012.2197233

[7] S. Kao et al., "A 7.5-Gb/s One-Tap-FFE

Transmitter With Adaptive Far-End Crosstalk Cancellation Using Duty Cycle Detection," in IEEE JSSC, vol.48, no.2, pp.391-404, 2013.

DOI: 10.1109/JSSC.2012.2227604

[8] S. Yuan et al., "A 4×20–Gb/s 0.86pJ/b/lane 2–tap–FFE source–series–terminated transmitter with far–end crosstalk cancellation and divider–less clock generation in 65nm CMOS," 2015 IEEE CICC, pp.1–4, 2015.

DOI: 10.1109/CICC.2015.7338414

[9] C. Aprile et al., "An Eight-Lane 7-Gb/s/pin Source Synchronous Single-Ended RX With Equalization and Far-End Crosstalk Cancellation for Backplane Channels," *in IEEE JSSC*, vol.53, no.3, pp.861-872, 2018.

DOI: 10.1109/JSSC.2017.2783679

[10] T. Oh *et al.*, "A 6-Gb/s MIMO Crosstalk Cancellation Scheme for High-Speed I/Os," in *IEEE JSSC*, vol.46, no.8, pp.1843-1856, 2011.

DOI: 10.1109/JSSC.2011.2151410

[11] S. Kao *et al.*, "A 10-Gb/s Adaptive Parallel Receiver With Joint XTC and DFE Using Power Detection," in *IEEE JSSC*, vol.48, no.11, pp.2815–2826, 2013. DOI: 10.1109/JSSC.2013.2282116

# BIOGRAPHY

# $Won\text{-}Byoung\ Lee\ (\mathrm{Member})$

2018: BS degree in Semiconductor Systems Engineering, Sungkyunkwan University. 2018~Current: Pursuing the MS degree in Semiconductor Display

degree in Semiconductor Display Engineering, Sungkyunkwan University.

# Bai-Sun Kong (Member)

1996: PhD degree in Electrical Engineering, KAIST. Currently, Professor in the Department of Semiconductor Systems Engineering, College of Information and Communication Engineering, Sungkyunkwan University.