ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 19-03-43

288

## 고속 듀오바이너리 송수신단 설계기술 동향

# Recent Trends on High-Speed Duobinary Transceiver Architecture

남 한 민\*, 공 배 선\* \*

Han-min Nam\*, Bai-Sun Kong\*\*

#### **Abstract**

This paper describes high-speed duobinary transceiver design techniques which are widely used to increase data-rate despite limited channel bandwidth. At high data-rate, signal level is severely degraded as signal frequency becomes larger than the channel bandwidth. Mathematically, a duobinary signal has lower frequency components compared to a Non-Return-to-Zero signal for the same data-rate. Therefore, by using the duobinary signaling, the signal loss can be effectively reduced in physical channel environment as compared to the Non-Return-to-Zero signaling. The mathematical basis of duobinary signaling, and its applications to high-speed transceiver design are investigated in this paper.

#### 요 약

본 논문에서는 데이터 전송 속도를 제한하는 채널의 대역폭 문제를 해결하기 위한 방법으로 널리 사용되는 고속 듀오바이 너리(duobinary) 송수신단 설계기술 동향을 서술한다. 고속 전송 환경에서는 전송 신호의 주파수가 채널의 대역폭보다 커지게 되어 신호의 손실이 극심해지는 문제가 생긴다. 듀오바이너리 신호는 같은 전송속도를 가지는 Non-Return-to-Zero 신호와 비교했을 때 수식적으로 더 낮은 주파수 대역폭을 가진다. 따라서 고주파 신호일수록 손실정도가 커지는 실제 데이터 채널 환경에서 듀오바이너리 신호기법을 사용함으로써 신호 손실을 효과적으로 줄일 수 있다. 이러한 듀오바이너리 신호기법의 수학적 분석과 더불어 듀오바이너리 신호기법을 고속 송수신단 설계에 적용한 여러 방법들에 대해 탐구한다.

Key words: channel bandwidth, duobinary, equalizer, high data-rate system, I/O interface

#### I . 서론

최근 빅-데이터 등의 원활한 대용량 통신을 위해 고속 통신 기술이 크게 관심을 받고 있다[1]. 이렇 게 데이터 전송 속도가 빨라지는 추세에서 일반적 으로 온-칩 대역폭보다 칩과 칩 사이의 오프-칩 네 트워크 대역폭이 전체 시스템의 속도를 결정한다 [2]. 오프-칩 네트워크 대역폭이 제한되는 이유 중 에는 칩과 칩을 연결하는 채널의 대역폭 문제가 가 장 주요하게 작용한다. 신호의 주파수가 올라감에

st Department of Semiconductor and Display Engineering, Sungkyunkwan University

★ Corresponding author

E-mail: bskong@skku.edu, Tel: +82-31-290-7690

Acknowledgment

This work was supported by the Basic Research Program through the National Research Foundation of Korea funded by the Ministry of Education under Grant NRF-2016R1D1A1B03933605.

Manuscript received Sep. 5, 2019; revised Sep. 24, 2019; accepted Sep. 27, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

따라 채널의 표피 효과(skin effect)와 유전 손실 (dielectric loss)로 인한 신호의 손실은 점점 커지게 되고 그 결과 채널의 대역폭이 제한된다.

이런 채널의 대역폭 문제를 해결하는 방법 중 하나로 듀오바이너리 신호기법이 널리 사용될 수 있다[3]-[10]. 듀오바이너리 신호기법은 신호의 주파수 스펙트럼을 절반으로 줄일 수 있다[3]. 이를 통해 신호의 주파수 성분이 낮아지고 그 결과 제한된 대역폭을 가지는 채널 환경에서도 신호 손실이 줄어들게 된다. 즉, 고속 동작이 필요한 오프-칩 인터페이스에서는 듀오바이너리 신호기법을 적용하여이득을 볼 수 있다. 아래에 서술할 본론에서는 듀오바이너리 신호기법을 적용하여 기득을 볼 수 있다. 아래에 서술할 본론에서는 듀오바이너리 신호기법을 적용한 방법들에 대해서 소개한다.

#### Ⅱ. 듀오바이너리 신호기법

#### 1. 듀오바이너리 신호기법의 수학적 분석

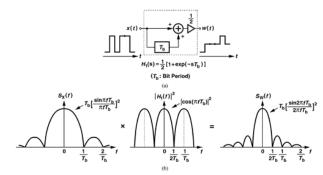

본 절에서는 수학적 선형 모델을 통한 듀오바이 너리 신호기법의 동작원리를 서술한다. 그림 1(a)에 서 볼 수 있듯이, 일반 Non-Return to Zero (NRZ) 2진 신호를 듀오바이너리 신호기법을 통해 부호화 한 신호는 다음 수식 (1)과 같다.

$$w[n] = \frac{1}{2}(x[n] + x[n-1]) \tag{1}$$

여기서 w의 경우 현재 듀오바이너리 신호이고, x는 NRZ 신호를 나타낸다[3]. 수식 (1)에서 볼 수 있듯이 NRZ 신호가 변하지 않으면 듀오바이너리 신호는 '0'이나 '1'을 가지고, NRZ 신호가 천이할 경우는 듀오바이너리 신호는 '1/2' 값을 갖게 되어신호의 기울기가 작아진다. 듀오바이너리 신호기법은 이렇게 신호의 주파수 성분을 낮출 수 있다.

이를 조금 더 수식적으로 분석하기 위해 그림 1(b)와 같이 듀오바이너리 부호화 과정을 주파수 영역에서 생각해 볼 수 있다. 식(1)의 전달함수를 주파수 영역에서 나타내면

$$H_1(f) = \frac{W(f)}{X(f)} = 1 + e^{-j2\pi f T_b}$$

(2)

으로 나타 낼 수 있다. 여기서  $T_b$ 는 하나의 UI의 주기를 나타낸다. 이를 통해 NRZ 신호의 주파수

스펙트럼을 알 때 NRZ 신호를 부호화한 듀오바이 너리 신호의 주파수 스펙트럼을 식 (3)과 같이 구 할 수 있다.

Fig. 1. (a) Linear model of duobinary signaling (b) Frequency spectrum of duobinary encoding process.

그림 1. (a) 듀오바이너리 신호기법의 선형 모델 (b) 주파수 스펙트럼으로 나타낸 듀오바이너리 부호화 과정

$$\begin{split} S_W(f) &= |H_1(f)|^2 \cdot S_X(f) \\ &= \cos^2(\pi f T_b) \cdot T_b \bigg[ \frac{\sin(\pi f T_b)}{\pi f T_b} \bigg]^2 \\ &= T_b \bigg[ \frac{\sin(2\pi f T_b)}{2\pi f T_b} \bigg]^2 \end{split} \tag{3}$$

여기서  $S_X(f)$ 와  $S_W(f)$ 는 각각 NRZ 신호의 주파수 스펙트럼과 이를 듀오바이너리 신호로 변환하였을 때의 주파수 스펙트럼을 나타낸다[3]. 식 (3)에서 알 수 있듯이, 듀오바이너리 신호의 주파수 대역폭 은 NRZ의 1/2배이므로 제한된 대역폭을 가진 채널 에서도 신호 손실을 줄일 수 있다.

앞서 살펴보았듯이 듀오바이너리 신호기법은 주 파수 대역폭을 반으로 압축할 수 있는 장점을 가진 다. 하지만 전압 준위가 2-준위인 NRZ 신호와 다 르게 듀오바이너리 신호는 전압 준위가 3-준위라 는 단점을 가지고 있다. 이로 인해 듀오바이너리 신호는 전압 잡음 여유(voltage noise margin)가 NRZ 신호에 비해 반으로 작아지게 된다.

#### 2. 듀오바이너리 송수신단 설계 기법

가. 듀오바이너리 신호 직접 전송 기법

#### (1) TX FIR 필터를 이용한 전송

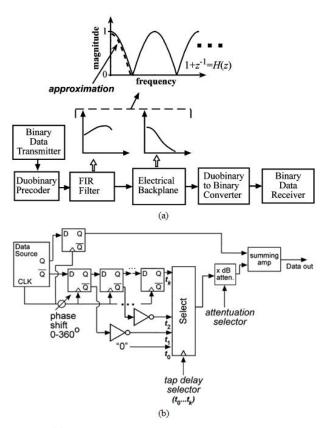

듀오바이너리 신호기법을 회로로 구현하기 위해서는 식(2)처럼 대역-통과 필터(band-pass filter)가 무한히 반복되는 필터를 이용해야 한다. 하지만실제 채널은 주파수 특성상 저역 필터(low-pass filter)로 작용하므로 채널을 통과한 신호가 정확히 듀

오바이너리 신호가 되도록 하는 것은 불가능하다. 이 때, 그림 2(a)의 점선부분으로 근사(approximation)시킨 필터를 설계하여 듀오바이너리 신호기법을 구현한 방법이 제안된 바 있다[4]. 보통 신호의 대부분의 에너지가 저주파 부근에 있다는 점을 생각하면 여기서 사용된 근사는 합리적이라 할 수 있다.이 근사 그래프는 단순한 저역 필터와 비슷한 특성을 가지므로 듀오바이너리 부호화에 실제 채널을이용할 수 있다.만약, 채널의 주파수 특성과 듀오바이너리 부호화 과정이 요구하는 주파수 특성이다를 경우에는 전체 주파수 전달 특성이 이 근사그래프가 되도록 FIR 필터를 사용할 수 있다. 그림 2(b)는 이를 위해 구현한 2-탭 FIR 필터이다.주어진 채널에 적합한 2-탭 FIR 필터의 2번째 탭 지연시간은 다음과 같다.

Fig. 2. (a) Architecture of duobinary transceiver using FIR filter (b) 2-tap FIR filter.

그림 2. (a) FIR filter를 사용한 듀오바이너리 송수신단 구조 (b) 2-탭 FIR 필터

$$t_n = nT_b + \tau \ (0 < \tau < T_b) \tag{4}$$

여기서  $T_b$ 는 하나의 UI의 주기를 나타낸다. n은 플립플롭을 이용한 디지털 지연계수를 나타내며

그림 2(b)의 tap delay selector를 이용해 원하는 지연된 신호를 선택할 수 있다.  $\tau$ 는  $T_b$ 보다 작은 지연을 조절하기 위한 아날로그 지연을 나타내고, 그림 2(b)의 phase shift를 통해 조절할 수 있다[4]. 이런 방식으로 2번째 탭의 지연시간과 크기를 자유롭게 조절하여 전체적인 주파수 전달 특성이 듀오바이너리 신호 변환에 적합하게 되도록 한다.

| TX <sub>IN</sub>                   |                                      | 1+z-1            | 1/(1+z <sup>-1</sup> ) |                                             |  |

|------------------------------------|--------------------------------------|------------------|------------------------|---------------------------------------------|--|

| Previous bit (ex. D <sub>E</sub> ) | Present bit<br>(ex. D <sub>0</sub> ) | V <sub>TIA</sub> | Selected reference     | RX <sub>OUT</sub><br>(ex. RD <sub>o</sub> ) |  |

| 1                                  | 1                                    | 2                | V (4.5)                | 1                                           |  |

|                                    | 0                                    | 1                | V <sub>H</sub> (1.5)   | 0                                           |  |

| 0                                  | 1                                    | 1                | N/ (0 m)               | 1                                           |  |

|                                    | 0                                    | 0                | V <sub>L</sub> (0.5)   | 0                                           |  |

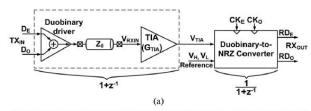

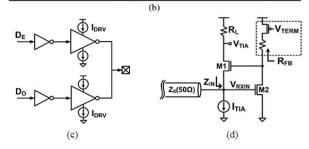

Fig. 3. (a) Architecture of duobinary transceiver using data summation (b) Data flow operation (c) Duobinary driver (d) TIA circuit diagram.

그림 3. (a) data summation을 활용한 듀오바이너리 송수신단 구조 (b) 데이터 흐름도 (c) 듀오바이너리 드라이버 (d) TIA 회로

하지만 기존의 2-tap FIR 필터에 비해 차지하는 면적과 소모하는 전력이 매우 크다는 문제점이 있다. 더불어, FIR 필터는 송신단에 구현되므로 듀오 바이너리 부호화를 위한 FIR 필터의 지연과 크기를 보정(calibration)하기 위해서는 수신단의 데이터가 필요하다. 이 때문에 FIR 필터의 자동 보정이어렵다는 단점이 있다.

#### (2) Data summation을 이용한 전송

송신단에서 데이터의 현재 값과 이전 값을 더하여 듀오바이너리 부호화를 구현할 수 있다[5]. 그림 3(a)는 이 방식대로 듀오바이너리 신호를 구현하는

전체적인 블록선도를 나타낸다. Duobinary driver 는 송신단에서 듀오바이너리 신호를 만들어 채널로 출력한다. TIA는 수신단 종단저항(termination resistor)을 정확히 50Ω이 되도록 하고 수신신호를 증폭한다. Duobinary-to-NRZ Converter는 듀오바이너리 신호를 다시 NRZ신호로 복호(decode)한다. 이 전체 회로의 구체적인 데이터 동작흐름은 그림 3(b)에 나타나있다.

Fig. 4. (a) Architecture of duobinary transmitter using serializer (b) Data timing diagram (c) SEL 2:1. 그림 4. (a) 직렬기를 이용한 듀오바이너리 송신단 구조 (b) 데이터 타이밍도 (c) SEL 2:1 회로

이 기법은 듀오바이너리 신호기법의 기본적 장점을 취함과 동시에 2-갈래 시간-인터리빙(2-way time-interleaving) 송신단에 필요한 여러 회로를 듀오바이너리 드라이버로 대체함으로써 신호 송신 전력을 감소시킬 수 있다[5]. 더불어 듀오바이너리 드라이버를 표시한 그림 3(c)와 같이, 송신단 종단저항을 제거하여 출력저항을 키우고 이를 통해 출력단의 전력 손실을 줄였다. 이 때 송신단 임피던스 매칭이 되지 않아 반사가 생기는 문제가 있지만 수신단에 Transimpedance Amplifier(TIA)를 사용하여

수신단의 입력신호를 증폭시키는 방법으로 이를 해결하였다. 하지만 그림 3(d)에 표시된 수신단의 TIA에는 궤환 회로(feedback loop)가 존재하고 결국 이에 의해 주파수 한계점이 생기게 된다는 단점이 있다. 이 문제점은 입력이 가파르게 천이할 경우 더욱 두드러진다. 또한 채널의 roll-off 특성을 듀오바이너리 부호화 과정에 사용하지 못하는 단점이 있다.

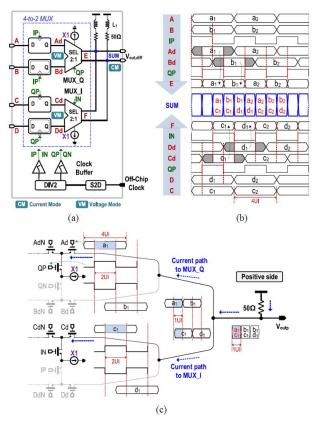

#### (3) Serializer를 활용한 전송

quarter-rate 방식의 송신단에는 채널로 데이터를 송신하기 위해 직렬화(serialize) 과정이 필요하다. 이 때, 마지막 직렬화 과정과 전류방식 덧셈기를 복합하여 듀오바이너리 신호기법을 구현한 방법이 그림 4(a)에 나타나있다[6]. 기존의 quarter-rate 방식의 송신단은 직렬화를 위해 4-to-1 멀티플렉서를 이용하지만 이 방법은 파란 점선에 표시된 4-to-2 MUX를 사용한다. 이를 최종 단에서는 전류 덧셈을 통해 듀오바이너리 신호로 부호화하게 된다. 그림 4(b)는 언급한 동작과정에 대해 자세히 나타낸다. 여기서 SEL 2:1 회로는 그림 4(c)와 같이 전류-모드 논리(current-mode logic, CML) 방식으로 구현하여 뒤의 전류 덧셈을 용이하게 할 뿐만 아니라 멀티플렉서의 지연시간을 완화시킨다.

이 기법은 언급한 대로 직렬기(Serializer)와 전류 덧셈기를 복합하는 방식으로 직렬기 최종 단에 필요한 멀티플렉서를 제거할 수 있으므로 면적과 전력의 관점에서 이득을 얻을 수 있다. 또한 간단한 방식의 CML 멀티플렉서를 사용하여 내부 회로의 대역폭을 키움과 동시에 전압신호를 전류신호로 변환하게 되므로 추가적인 전압-전류 변환기를 사용하지 않아도 된다는 장점을 가진다. 하지만 이역시 채널의 roll-off 특성을 듀오바이너리 부호화과정에 사용하지 못한다는 단점이 있고, 직렬화 과정에서 각각의 회로에 쓰이는 클록신호의 알맞은타이밍을 맞추는 설계가 고속으로 동작할수록 어려워진다는 문제점이 있다.

#### 나. Precoder를 활용한 듀오바이너리 신호 구현

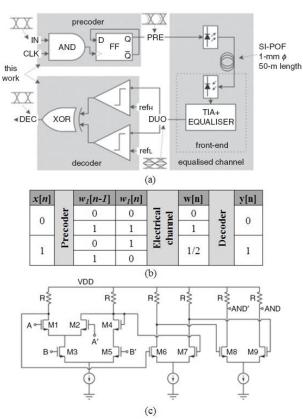

#### (1) AND 방식 precoder를 사용한 구현

듀오바이너리 신호기법의 경우 식 (1)과 같이 전 데이터를 사용하여 부호화를 하므로 에러가 다음 bit으로 전달되는 문제가 생긴다. 이 문제를 해결하 는 방법 중에 송신단에서 듀오바이너리 부호화를 수행하기 전에 그림 5(a)와 같이 precoder를 사용 하는 방법이 있다[7]. 이 때 precoder는

Fig. 5. (a) Architecture of duobinary transceiver using AND precoder (b) Data flow (c) SCL AND

그림 5. (a) AND 방식 precoder를 활용한 듀오바이너리 송수신단 구조 (b) 데이터 흐름도 (c) SCL AND

$$w_1[n] = w_1[n-1] \oplus x[n] \tag{5}$$

을 회로로 구현해야 한다. 이 때 x는 NRZ 신호이고,  $w_1$ 은 x를 precoder를 통해 precoding한 신호이다. 그 결과 그림 5(b)와 같이, 이전 데이터와의 연계성이 없어지므로 에러 전달 문제가 사라지게 된다. 이 때, 식 (5)의 구현을 논리식대로 XOR을 이용하면 궤환 경로가 생기게 되어 임계시간 조건이생기게 된다. 이를 여기서는 AND와 D-플립플롭을통해 구현하였다. 이 때 AND과 D-플립플롭은 source-coupled logic (SCL) 방식으로 구현하였으며 그림 5(c)는 SCL AND를 나타낸다.

언급한대로 AND를 사용한 precoder를 통해 사전 부호화과정에서 생기는 궤환 루프를 제거하여 임계시간 조건 문제를 해결할 수 있다. 또한 클록 신호를 입력으로 받는 AND 게이트의 경우는 SCL

Fig. 6. (a) Architecture of duobinary transmitter using parallel precoder (b) Parallel precoder

그림 6. (a) Parallel precoder를 활용한 듀오바이너리 송신단 구조 (b) 병렬 precoder

방식을 사용하여 빠르게 동작하도록 하였다. 하지만 여기에 사용된 논리회로는 full-rate으로 동작하므로 매우 고속으로 동작해야 한다. 이를 위한 SCL 방식 회로의 경우, 전력소모가 크고 면적을 많이 차지한다는 단점이 존재한다.

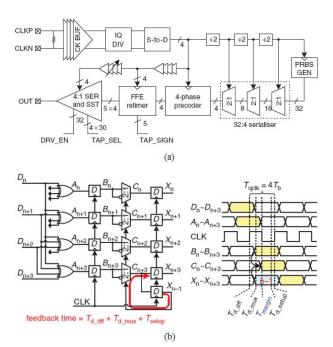

#### (2) Parallel precoder를 사용한 구현

그림 6(a)는 precoder를 사용한 quarter-rate 송 신단의 블록선도이다. 식 (5)의 precoding을 quarterrate 송신단에서 그대로 구현할 경우, 궤환 루프가 복잡해지는 문제가 있는데 이를 완화하기 위해 다 음처럼 식을 전개할 수 있다[8].

$$\begin{aligned} w_{1}[n] &= w_{1}[n-1] \oplus x[n] \\ w_{1}[n+1] &= w_{1}[n-1] \oplus x[n] \oplus x[n+1] \\ w_{1}[n+2] &= w_{1}[n-1] \oplus x[n] \oplus x[n+1] \\ &\oplus x[n+2] \\ w_{1}[n+3] &= w_{1}[n-1] \oplus x[n] \oplus x[n+1] \\ &\oplus x[n+2] \oplus x[n+3] \end{aligned} \tag{6}$$

이 식 (6)을 회로로 구현한 것이 그림 6(b)에 나타난 병렬 precoder이다.

병렬 precoder의 경우  $w_1[n-1]$ 만 궤환해 주면 되므로 궤환 경로가 그림 6(b)의 적색 화살표와 같이 간단해지고 하나의 멀티플렉서만 지나므로

$$4T_b > T_{dff} + T_{mux} + T_{setup} \tag{7}$$

과 같이 임계시간이 완화된다. 여기서  $T_{\rm eff}$ ,  $T_{\rm mux}$ 는 각각 D-플립플롭, 멀티플렉서의 지연시간이고,  $T_{\rm setup}$ 은 D-플립플롭의 셋업 시간이다. 하지만 4-입력 XOR 게이트가 사용되므로 고속 XOR의 경우 전력 소모가 심각할 수 있다. 더불어  $w_1[n]$  신호를 생성하기 위해서는 입력 XOR을 하지 않아도 되지만 타이밍을 맞추기 위해 4-입력 XOR을 사용하므로 전력이 낭비된다는 문제점이 있다.

Fig. 7. (a) Architecture of duobinary receiver using CDR-Assisted DFE (b) DFE waveform

(b)

0

time

그림 7. (a) CDR-assisted DFE를 활용한 수신단 구조 (b) DFE의 파형

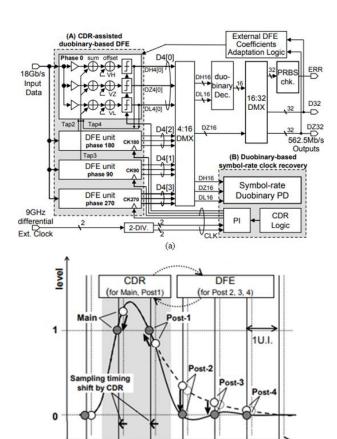

다. DFE를 활용한 듀오바이너리 신호 구현 기법 (1) CDR-Assisted DFE를 활용한 수신단

그림 7(a)는 clock data recovery(CDR)로 보조한 decision-feedback equalizer(DFE)가 포함된 전체 quarter-rate 듀오바이너리 수신단 구조를 나타낸다[9]. 기존의 경우 DFE를 통해 첫 번째 포스트-커서에 의한 ISI를 제거한다[11]. 하지만 여기에서는

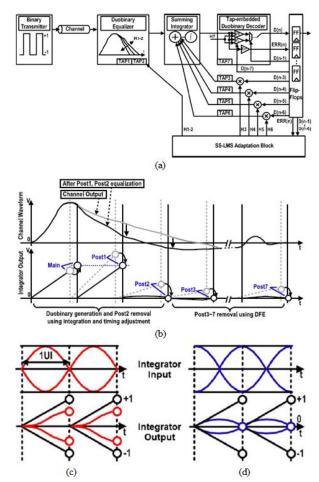

Fig. 8. (a) Architecture of integrating duobinary DFE RX (b) Single-bit response (c) Integrating DFE waveform (d) Integrating duobinary DFE waveform

그림 8. (a) 적분 듀오바이너리 DFE 수신단 구조 (b) 단일 -bit 응답 (c) 적분 DFE 파형 (d) 적분 듀오바이너 리 DFE 파형

첫 번째 포스트 커서를 DFE에서 처리하지 않고, 클록신호를 움직여 그림 7(b)에 나타낸 파형과 같이 첫 번째 포스트-커서의 크기를 주-커서와 같게하는 방식으로 듀오바이너리 신호기법을 구현한다. 즉, 이전 데이터와 현재 데이터를 더하는 회로 없이 ISI를 이용하여 중첩의 원리를 통해 듀오바이너리 신호기법을 구현하게 되므로 더욱 간단하게 구현할 수 있다.

첫 번째 포스트-커서를 듀오바이너리 부호화에 활용함으로써 추가적인 이득을 얻을 수 있다. 먼저, 첫 번째 포스트-커서의 ISI를 DFE를 이용해 제거하는 것이 아니므로 상대적으로 큰 전류를 사용하는 첫 번째 DFE 탭을 없앨 수 있다. 더불어 첫 번째 탭이 DFE에서 삭제되므로 DFE의 중요한 이슈인 임계 시간critical timing)을 완화시킬 수 있다.

Table 1. Performance comparison.

표 1. 성능 비교

|                                  | TMTT'05<br>[4]                | JSSC'14<br>[5]                  | TCASI'18<br>[6] | EL'17<br>[7]                      | EL'18<br>[8]                  | ISSCC'09<br>[9]                   | JSSC'17<br>[10]                       |

|----------------------------------|-------------------------------|---------------------------------|-----------------|-----------------------------------|-------------------------------|-----------------------------------|---------------------------------------|

| Process                          | -                             | 65nm                            | 65nm            | 180nm                             | 55nm                          | 90nm                              | 45nm                                  |

| Supply(V)                        | 1.2                           | 1.05                            | 1.2             | 1.8                               | _                             | 1.2                               | 1.1                                   |

| Channel<br>Configura-tion        | 6"<br>point-to-point<br>(FR4) | 0.6"<br>point-to-point<br>(FR4) | -               | 50m<br>point-to-point<br>(SI-POF) | 3"<br>point-to-point<br>(FR4) | 9.8"<br>point-to-point<br>(low-ε) | 4.72"<br>4-drop<br>(7-slave)<br>(FR4) |

| Max. speed (Gb/s/lane)           | 10                            | 6.4                             | 36              | 3.125                             | 12.8                          | 18                                | 5.8                                   |

| Signal<br>Swing(mV)              | 125                           | 80                              | 366<br>(diff)   | 185                               | 35                            | _                                 | 410<br>(diff)                         |

| Energy<br>Efficiency<br>(pJ/bit) | -                             | 0.6                             | 1.3             | 9.1                               | 7.6                           | 5.6                               | 2.5                                   |

| Area (mm²)                       | -                             | 0.033<br>(TX+RX)                | 0.037<br>(TX)   | 0.030<br>(precoder,<br>decoder)   | 0.053<br>(TX)                 | 0.202<br>(RX)                     | 0.087<br>(RX)                         |

| Fraction of baud rate            | full-rate                     | half-rate                       | quarter-rate    | full-rate                         | quarter-rate                  | quarter-rate                      | half-rate                             |

하지만 이 기법은 주-커서와 포스트-커서의 크기가 같아야 하는데 고주파 잡음이 있게 되면 이에의해 각각의 커서 크기가 매 순간 흔들리게 되어 듀오바이너리 신호기법을 제대로 구현할 수 없다. 다시 말해, 이 방법은 고주파 잡음에 상당히 취약하다는 문제점을 안고 있다.

#### (2) Integrating DFE를 활용한 수신단

고주파 잡음 문제를 해결하기 위해 수신단 측에 전류 적분 DFE와 듀오바이너리 신호기법을 결합한 적분 듀오바이너리 DFE 수신단이 제안된 바 있다[10]. 그림 8(a)는 적분 듀오바이너리 DFE의 전체적인 블록선도를 나타낸다. Duobinary Equalizer를 통해서는 주-커서와 첫 번째 포스트-커서의 Summing Integrator의 출력값이 같게 되도록 하여 듀오바이너리 신호기법을 구현하고 두 번째 포스트 커서의 적분 출력값은 상쇄되도록 한다. 그 이후의 포스트 -커서는 DFE를 통해 제거하여 잡음에 견고한 수신기를 구현하였다. 그림 8(b)는 적분 듀오바이너리 DFE 수신단의 동작을 단일 펄스 응답 파형으로나타낸 것이다.

전류 적분 DFE는 첫 번째 DFE 탭의 부담이 커지는 단점이 있는데, 여기서는 듀오바이너리 신호기법과 결합하여 첫 번째 탭을 DFE로 처리하지 않

도록 하여 해당 이슈를 해결하였다. 또한 기존의 전류 적분 DFE의 경우, 그림 8(c)와 같이 입력-신호 종속(input-data dependency) 문제가 발생하는데[11], 적분 듀오바이너리 DFE는 그림 8(d)와 같이 입력-신호 종속 문제를 해결할 수 있다. 하지만그림 8(d)에서 볼 수 있듯이 적분기의 출력이 3-준위를 가지므로 듀오바이너리의 본질적 문제인 전압 잡음 여유가 NRZ 신호기법에 비해 줄어든다는단점 역시 가지게 된다. 표 1에서는 현재까지 살펴본 듀오바이너리 신호기법을 구현한 기법들의 성능을 비교하였다.

#### Ⅲ. 결론

본 논문에서는 고속 I/O 인터페이스를 위한 해결 책으로 듀오바이너리 신호기법에 대해 논의하였다. 직접 듀오바이너리 신호를 전송하는 방법과 precoder를 사용하여 듀오바이너리 신호를 구현하는 방식에 대해 탐구하였다. 추가적으로 DFE를 활용해 듀오바이너리 신호기법을 구현하는 방법 또한 살펴보았다. 이러한 기술들을 통해 고속 송수신단에서 듀오바이너리 신호기법을 구현하여 신호의 대역폭을 줄임으로써 기존보다 고속 동작에 유리함을 확인할 수 있었다.

#### References

[1] Y. Lu *et al.*, "Design Techniques for a 66 Gb/s 46 mW 3-Tap Decision Feedback Equalizer in 65 nm CMOS," *IEEE JSSC*, vol.48, no.12, pp.3243-3257, 2013.

DOI: 10.1109/JSSC.2013.2278804

[2] P. K. Hanumolu *et al.*, "Equalizers for High-Speed Serial Links," *JHSES*, vol.15, no.2, pp.429–458, 2005. DOI: 10.1142/S0129156405003259

[3] J. Lee *et al.*, "Design and Comparison of Three 20-Gb/s Backplane Transceivers for Duobinary, PAM4, and NRZ Data," in *IEEE JSSC*, vol.43, no.9, pp.2120–2133, 2008.

DOI: 10.1109/JSSC.2008.2001934

[4] J. H. Sinsky *et al.*, "High-speed electrical backplane transmission using duobinary signaling," *IEEE TMTT*, vol.53, no.1, pp.152–160, Jan. 2005. DOI: 10.1109/TMTT.2004.839326

[5] S.-M. Lee, *et al.*, "An 80 mV-Swing Single-Ended Duobinary Transceiver With a TIA RX Termination for the Point-to-Point DRAM Interface," *IEEE JSSC*, vol.49, no.11, pp.2618-2630, 2014.

DOI: 10.1109/JSSC.2014.2359665

[6] Y. Chen *et al.*, "A 36-Gb/s 1.3-mW/Gb/s Duobinary-Signal Transmitter Exploiting Power-Efficient Cross-Quadrature Clocking Multiplexers With Maximized Timing Margin," *IEEE TCAS-I*, vol.65, no.9, pp.3014-3026, 2018.

DOI: 10.1109/TCSI.2018.2829725

[7] J. Aguirre *et al.*, "3.125 Gbit/s CMOS transceiver for duobinary modulation over 50-m SI-POF channels," *Electronics Letters*, vol.53, no.4, pp. 258–260, 2017. DOI: 10.1049/el.2016.4539

[8] H. Ko *et al.*, "Single-ended voltage-mode duobinary transmitter with feedback time reduced parallel precoder," *Electronics Letters*, vol.54, no.15, pp.936-937, 2018. DOI: 10.1049/el.2018.5021 [9] K. Sunaga *et al.*, "An 18Gb/s duobinary receiver with a CDR-assisted DFE," *IEEE ISSCC*, pp. 274-275, 2009. DOI: 10.1109/ISSCC.2009.4977414 [10] H.-W. Lim *et al.*, "A 5.8-Gb/s Adaptive Integrating Duobinary DFE Receiver for Multi-

Drop Memory Interface," *IEEE JSSC*, vol.52, no.6, pp.1563–1575, 2017.

DOI:10.1109/JSSC.2017.2675923

[11] T. O. Dickson *et al.*, "A 12–Gb/s 11–mW Half–Rate Sampled 5–Tap Decision Feedback Equalizer With Current–Integrating Summers in 45–nm SOI CMOS Technology," *IEEE JSSC*, vol.44, no.4, pp.1298–1305, 2009.

DOI: 10.1109/JSSC.2009.2014733

### **BIOGRAPHY**

#### Han-min Nam (Member)

2018: BS degree in Semiconductor Systems Engineering, Sungkyunkwan University.

2018~Current: Pursuing the MS degree in Semiconductor Display Engineering, Sungkyunkwan University.

#### Bai-Sun Kong (Member)

1996: PhD degree in Electrical

Engineering, KAIST.

Currently, Professor in the

Department of Semiconductor

Systems Engineering, College of

Information and Communication

Engineering, Sungkyunkwan University.