https://doi.org/10.6113/TKPE.2018.23.3.153

# 고효율 및 고전력밀도 3-레벨 LLC 공진형 컨버터

구현수<sup>1</sup>, 김효훈<sup>2</sup>, 한상규<sup>†</sup>

# High-Efficiency and High-Power-Density 3-Level LLC Resonant Converter

Hyun-Su Gu<sup>1</sup>, Hyo-Hoon Kim<sup>2</sup>, and Sang-Kyoo Han<sup>†</sup>

#### **Abstract**

Recent trends in high-power-density applications have highlighted the importance of designing power converters with high-frequency operation. However, conventional LLC resonant converters present limitations in terms of high-frequency driving due to switching losses during the turn-off period. Switching losses are caused by the overlap of the voltage and current during this period, and can be decreased by reducing the switch voltage. In turn, the switch voltage can be reduced through a series connection of four switches, and additional circuitry is essential for balancing the voltage of each switch. In this work, a three-level LLC resonant converter that can operate at high frequency is proposed by reducing switch losses and balancing the voltages of all switches with only one capacitor. The voltage-balancing principle of the proposed circuit can be extended to n-level converters, which further reduces the switch voltage stress. As a result, the proposed circuit is applicable to high-input applications. To confirm the validity of the proposed circuit, theoretical analysis and experimental verification results from a 350 W-rated prototype are presented.

Key words: 3-level converter, High efficiency, High frequency, High power density, LLC resonant converter

### 1. 서 론

최근 초소형 및 초고밀도 전원장치가 제품의 핵심기술로 부상하고 있다. 이를 위해 전력변환컨버터 내 큰부피를 차지하는 리액티브 소자의 소형화를 위해서는 고주파수 구동이 필수적이다<sup>[1]</sup>. 하지만 스위치는 턴 온 및 턴 오프 시 스위치 양단전압과 전류의 중첩에 의해 매 스위칭 주기별로 스위칭 손실이 발생하며, 주파수가증가할수록 비례하여 스위치의 심각한 손실과 발열을 발생시킨다. 이러한 스위칭 손실은 스위치 양단전압을 저감시켜 전압과 전류의 중첩되는 크기와 시간을 줄임으로써 확연히 개선할 수 있다. LLC 공진형 컨버터의 영전압스위칭(Zero Voltage Switching, ZVS)을 통해 턴 온

(a) conventional (b) Switch voltage reduction Fig. 1. The voltage and current of the switch in turned off period.

시 손실이 발생하지 않지만, 여전히 턴 오프 시에 손실은 존재한다. 그림 1(a)은 일반적인 LLC 공진형 컨버터의 스위치 턴 오프 시, 스위치의 양단전압과 전류 및손실을 나타내고 있다. 동일한 조건에서 그림 1(b)와 같이스위치 양단전압이 절반으로 낮아지면 동일한 전류임에도 불구하고 전압의 크기가 절반으로 줄어들고, 중첩되는 시간인 tf 또한 tf'으로 저감되기 때문에 이론적으로 턴 오프 손실은 스위치 양단전압 저감 비인 절반 이상으로 저감할 수 있다. 또한 스위치의 내압을 저감함에따라 우수한 성능의 스위치 사용이 가능하여 작은 Ciss

$<sup>\</sup>begin{matrix} \mathbf{i}_{ds} \cdot \mathbf{V}_{ds} \\ \\ \mathbf{i}_{ds} \cdot \mathbf{V}_{ds} \end{matrix} \qquad \begin{matrix} \mathbf{i}_{ds} \cdot \mathbf{V}_{ds} \\ \\ \mathbf{i}_{ds} \cdot \mathbf{V}_{ds} \end{matrix}$

Paper number: TKPE-2018-23-3-1

Print ISSN: 1229-2214 Online ISSN: 2288-6281

<sup>†</sup> Corresponding author: djhan@kookmin.ac.kr, POESLA, School of Electrical Eng., Kookmin University

Tel: +82-2-910-5467 Fax: +82-2-910-4449

School of Electrical Eng., Kookmin University

Network Access Business Unit, Technical support, FAE, Pulse Electronics.

Manuscript received Feb. 1, 2018; revised Feb. 13, 2018; accepted Mar. 14, 2018

<sup>—</sup> 본 논문은 2017년 전력전자학술대회 우수추천논문임

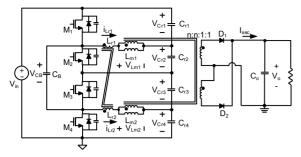

Fig. 2. Proposed 3-level LLC resonant converter.

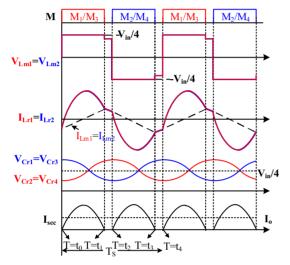

Fig. 3. Key waveforms of the proposed circuit.

R<sub>ds(on)</sub>을 통하여 스위치의 게이트 구동 손실 및 도통 손실을 저감할 수 있다. 하지만 기존 3-레벨 컨버터는 스위치 양단전압 저감 및 전압 평형을 위한 부가적인 액티브 소자의<sup>[2],[3]</sup> 추가가 불가피하여 손실 및 체적 저감에 한계를 갖는다. 따라서 본 논문에서는 4개 스위치의 직렬연결을 통한 스위칭 손실 저감 및 단 하나의 커패시터를 이용하여 모든 스위치의 전압평형을 이룰 수 있는 고효율 및 고전력밀도 3-레벨 LLC 공진형 컨버터를 제안한다.

#### 2. 제안 3-레벨 LLC 공진형 컨버터

#### 2.1 제안회로 모드 분석

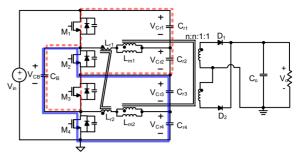

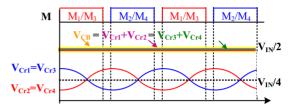

그림 2는 제안 3-레벨 LLC 공진형 컨버터를 나타낸다. 제안회로는 4개의 스위치( $M_1$ - $M_4$ )가 직렬로 연결되며, 이와 병렬로 4개의 공진 커패시터( $C_{r1}$ - $C_{r4}$ )가 직렬로 연결된다. 두개의 공진 인덕터와 두개의 트랜스포머는 그림과 같이 각각 직렬로 연결되며, 밸런싱 커패시터( $C_B$ )는 스위치  $M_1/M_3$ 의 source 사이에 위치하여 연결된다. 그림 3은 제안회로의 정상상태 주요파형을 나타내며, 4개 스위치는  $M_1/M_3$  스위치가 동시에 턴 온 되고,  $M_2/M_4$  스위치가 동시에 턴 온 되며, 스위칭 동작에 따라 동작은 4개 모드로 나눌 수 있다. 제안 컨버터의 모드 해석의 편의를 위해 다음과 같은 가정을 한다.

- 1) 출력 전압  $V_O$ 와 밸런싱 커패시터 전압  $V_{CB}$ 는 일정할 만큼 출력 커패시터  $C_O$ 와 밸런싱 커패시터  $C_B$ 는 충분히 크다.

- 2) 그림에 도시한 기생성분을 제외한 모든 기생성분은 제외한다.

- 3) 모든 MOSFET의 출력 커패시턴스 Coss는 동일하다.

- 4) 모든 공진 커패시터(C<sub>r1</sub>, C<sub>r2</sub>, C<sub>r3</sub>, C<sub>r4</sub>)의 커패시턴스 는 C<sub>r</sub>로 동일하다.

- 5) 공진 인덕터 $(L_{r1}, L_{r2})$ 의 인덕턴스는  $L_r$ 로 동일하며, 트랜스포머 $(L_{ml}, L_{m2})$ 의 자화인덕턴스는  $L_m$ 으로 동일하다.

- 6) 2차 측 동기정류기는 다이오드로 표현하다.

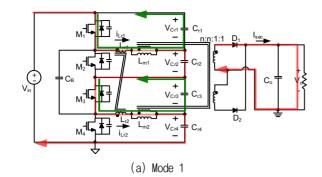

Mode  $1(t_0-t_1)$ : 스위치  $M_1/M_3$ 이 턴 온될 때, Mode 1이 시작된다. 공진 인덕터의 전류  $i_{Lr1}$ ,  $i_{Lr2}$ 는 그림 4(a)와 같이 공진 커패시터와 공진하며 사인파 형태로 증가한다. 이를 통해 공진 커패시터  $V_{Cr1}$ ,  $V_{Cr2}$ 의 전압은 감소하고,  $V_{Cr2}$ ,  $V_{Cr4}$ 의 전압은 증가한다. 이 때, 공진 주파수는 식 (1)과 같다. 2차 측 다이오드  $D_1$ 은 도통되며, 식 (2)와 같이 공진 인덕터 전류와 자화 인덕터 전류의 차이가 턴 비가 고려되어 2차 측 다이오드를 통해 흐른다. 트랜스포머 1차 측 전압  $V_{Lm}$ 은  $+V_{in}/4$ 로 클램프되며, 자화 인덕터 전류는  $+V_{in}/4$  전압이 인가되어 선형적으로 상승한다.

$$f_r = \frac{1}{2\pi\sqrt{2L_rC_r}}\tag{1}$$

$$i_{D1} = n(i_{Lr} - i_{Lm}) \tag{2}$$

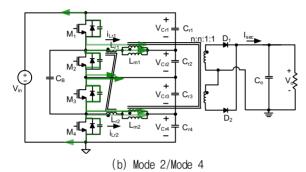

Mode  $2(t_1-t_2)$ : 스위치  $M_1/M_3$ 이 턴 오프될 때, Mode 2가 시작된다. 공진 인덕터 전류와 트랜스포머 자화 인덕터 전류가 동일해지는 순간으로, 2차 측 다이오드  $D_1$ 에는 전류가 흐르지 않으므로  $D_1$ 은 턴 오프 된다. 이때, 트랜스포머 자화 인덕터는 공진에 참여하며, 공진주파수는 자화 인덕턴스를 포함한 식 (2)의 공진주파수를 갖는다. Mode 2 구간은 dead time으로 매우 짧아 선형으로 감소하는 것처럼 보이게 된다. 이 때, 자화 인덕터의 전류는 식 (4)와 같으며 그림 4(b)와 같이  $M_1/M_3$ 스위치의 출력 커패시터를 창전시킴으로써 식 (5)의 조건이 만족될 때,  $M_2/M_4$ 스위치는 ZVS가 가능하다[4].

$$f_{r2} = \frac{1}{2\pi\sqrt{2(L_m + L_r)C_r}}$$

(3)

$$i_{Lm\_pk} = \frac{V_{in}}{L_m} \frac{T_s}{16}$$

(4)

$$i_{Lm\_pk} > \frac{2\,V_{in}\,C_{oss}}{t_{dead}} \tag{5}$$

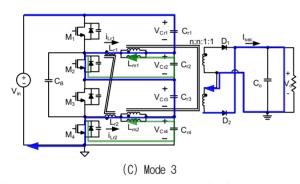

Fig. 4. Mode operations of the proposed circuit.

Mode  $3(t_2-t_3)$ : 스위치  $M_2/M_4$ 가 턴 온될 때, Mode 3이 시작된다. 공진 인덕터의 전류  $i_{Lrl}$ ,  $i_{Lr2}$ 는 그림 4(c)와 같이 공진 커패시터와 공진하며 사인파 형태로 감소한다. 이를 통해 공진 커패시터  $V_{Crl}$ ,  $V_{Cr2}$ 의 전압은 증가하고,  $V_{Cr2}$ ,  $V_{Cr4}$ 의 전압은 감소한다. 이 때, 공진 주파수는 Mode 1과 동일하게 식 (1)과 같다. 2차 측 다이오드  $D_2$ 는 도통되며, 식 (6)과 같이 공진 인덕터와 자화 인덕터 전류의 차이가 턴 비가 고려되어 2차 측 다이오드를통해 흐른다. 트랜스포머 1차 측 전압  $V_{Lm}$ 은  $-V_{in}/4$ 로 클램프되며, 자화 인덕터 전류는  $-V_{in}/4$  전압이 인가되어 선형적으로 감소한다.

$$i_{D2} = n(i_{Ix} - i_{Im}) \tag{6}$$

Mode  $4(t_3-t_4)$ : 스위치  $M_2/M_4$ 가 턴 오프될 때, Mode 4가 시작된다. 공진 인덕터 전류와 트랜스포머 자화 인덕터 전류는 동일해지면, 2차 측 다이오드  $D_2$ 에는 전류가 흐르지 않으므로  $D_2$ 는 턴 오프 된다. 이 때, 트랜스포머자화 인덕터는 공진에 참여하며, 공진 주파수는 자화

Fig. 5. The conduction pathes of the proposed circuit by voltage balancing principle.

Fig. 6. The key waveform for the proposed circuit voltage balancing principle.

인덕턴스를 포함한 식 (2)의 공진 주파수를 갖는다. Mode 4 구간은 Mode 2와 동일한 원리로  $M_1/M_3$  스위치는 ZVS가 가능하다. 차후 제안회로는 Mode 1부터 Mode 4까지의 동작을 반복한다.

#### 2.2 제안회로의 전압평형 원리

앞서 모드분석과 같이 스위치  $M_1/M_3$ 가 턴 온 시, 그림 5의 점선과 같은 경로로 도통하며 KVL(Kirchhoff's Voltage Law)에 의해 식 (7)이 만족한다.

$$V_{CB} = V_{Cr1} + V_{Cr2} (7)$$

반대로  $M_2/M_4$ 가 턴 온 시, 그림 5의 실선과 같은 경로로 KVL에 의해 식 (8)이 만족한다.

$$V_{CB} = V_{Cr3} + V_{Cr4} (8)$$

상기 동작을 매 주기 교번동작 함으로써 식 (9)가 도 출된다.

$$V_{CB} = V_{Cr1} + V_{Cr2} = V_{Cr3} + V_{Cr4}$$

(9)

또한, 스위칭 동작에 관계없이 입력전압(V<sub>in</sub>)과 공진 커패시터(C<sub>r1</sub>-C<sub>r4</sub>)의 KVL에 의해 식 (10)이 도출된다.

$$V_{in} = V_{Cr1} + V_{Cr2} + V_{Cr3} + V_{Cr4} \tag{10} \label{eq:10}$$

상기 식 (9)와 (10)에 의해 식 (11)이 도출된다.

$$V_{CB} = V_{Cr1} + V_{Cr2} = V_{Cr3} + V_{Cr4} = \frac{V_{in}}{2}$$

(11)

Fig. 7. Multi-level expansion principle of the proposed circuit.

이를 통해 그림 6과 같이 공진 커페시터의 전압은 스위칭 동작에 의해 공진하는 전압임에도 불구하고, 밸런싱 커페시터의 전압  $V_{CB}$ 과  $V_{Crl}$ ,  $V_{Cr2}$ 의 전압의 합과  $V_{Cr3}$ ,  $V_{Cr4}$ 의 전압의 합이 모두 동일함을 알 수 있다. 따라서 공진 커페시터와 병렬로 연결된 모든 스위치 전압첨두치를 입력전압의 절반으로 보장됨을 알 수 있다.

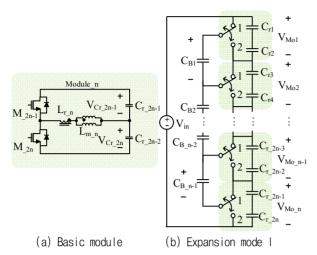

#### 2.3 제안회로의 멀티레벨 확장 원리

그림 7은 제안회로의 멀티레벨 확장 원리 설명을 위한 기본 모듈과 함께 멀티레벨 LLC 공진형 컨버터를 나타내었다. 제안회로는 기본 모듈과 밸런싱 커패시터  $C_B$ 의 추가만으로 멀티레벨 컨버터로 확장이 가능하며, 동시에 전압 평형을 보장하므로 확장에 용이한 구조적특성을 가진다. 하나의 기본 모듈은 그림 7(a)에 보이는 바와 같이 스위치  $2^{11}(M_{2n-1},\ M_{2n})$ , 공진 커패시터  $2^{11}(C_{r_2n-1},\ C_{r_2n})$ , 공진 인덕터  $1^{11}(L_{r_n})$ , 트랜스포머  $1^{11}(T_n)$ 로 구성된다. 이 때, 밸런싱 커패시터는 각 모듈을 그림 7(b)와 같은 구조를 보이게 된다. 제안된 멀티레벨 LLC 공진형 컨버터는 기본 모듈  $1^{11}(T_r)$ 를 연결하여  $1^{11}(T_r)$ 를 구성하며,  $1^{11}(T_r)$ 를 가장하며,  $1^{11}(T_r)$ 를 가장하며,  $1^{11}(T_r)$ 를 연결하여  $1^{11}(T_r)$ 를 가장하며,  $1^{11}(T_r)$ 를 가장되다.

앞서 제안회로와 동일하게 스위치 구동은 홀수( $M_1$ ,  $M_3$ ,…,  $M_{2n-1}$ ) 스위치와 짝수( $M_2$ ,  $M_4$ ,…,  $M_{2n}$ ) 스위치가 동시에 구동된다. 홀수 스위치 구동 시, 그림 7(b)에서 스위치가 '1'에 위치하면, 각각의 밸런싱 커패시터 전압은 다음과 같은 수식이 성립한다.

$$V_{CB \ n-1} = V_{Cr \ 2n-3} + V_{Cr \ 2n-2}$$

(n=2, 3, 4,···) (12)

반대로, 짝수 스위치 구동 시, 그림 7(b)에서 스위치가 '2'에 위치하면, 각각의 밸런싱 커패시터 전압은 다음과 같은 수식을 만족한다.

$$V_{CB \ n-1} = V_{Cr \ 2n-1} + V_{Cr \ 2n} \quad (n=2, 3, 4, \cdots)$$

(13)

상기 동작으로부터 식 (14)가 도출된다.

$$V_{CB\_n-1} = V_{Cr\_2n-3} + V_{Cr\_2n-2} = V_{Cr\_2n-1} + V_{Cr\_2n}$$

(14)

여기서. n은 2 이상의 정수이다.

또한, 스위칭 동작에 관계없이 입력전압 $(V_in)$ 과 공진 커패시터의 KVL에 의해 식 (15)가 도출되다.

$$V_{in} = V_{Cr1} + V_{Cr2} + \cdots + V_{Cr\_2n-1} + V_{Cr\_2n}$$

(15)

상기 식 (14)와 (15)에 의해 식 (16)이 도출된다.

$$V_{CB_{-}n-1} = V_{Cr_{1}} + V_{Cr_{2}} = \dots = V_{Cr_{-}2n-1} + V_{Cr_{-}2n} = \frac{V_{in}}{n}$$

(16)

이를 통해 공진 커패시터와 병렬로 연결된 모든 스위치 양단전압 첨두치를  $V_{in}/n$ 으로 모듈 수에 비례하게 더욱 감소시킬 수 있다.

#### 3. 제안회로 분석 및 설계

#### 3.1 제안회로 입출력 전압변환비

제안회로 입출력 전압변환비의 이론적 분석을 위해 다음과 같은 가정을 한다.

- 1) 회로 내 모든 전압 및 전류는 스위칭 주파수의 기본 파 성분인 사인파만 존재한다.

- 2) 스위칭 주파수는 공진 주파수와 동일하다.

- 3) 1차 측으로 반영된 부하의 등가 임피던스(R<sub>el</sub>, R<sub>e2</sub>) 는 R<sub>e</sub>로 동일하다.

제안회로의 턴 비는 부하의 변화에 따른 스위칭 주파수의 변화가 없는 공진탱크의 전압변환비 1을 기준으로 선정한다. 제안회로의 트랜스포머 양단에 걸리는 전압을  $\pm(V_{in}/4)$  기준으로 트랜스포머의 턴 비가 선정되며, 공진 탱크의 전압변환비를 고려하면 식 (17)과 같이 나타낼수 있다.

$$\frac{V_{in}}{4} = nV_O \Rightarrow \frac{V_O}{V_{in}} = \frac{1}{4n}H(j\omega_s) \tag{17}$$

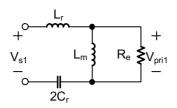

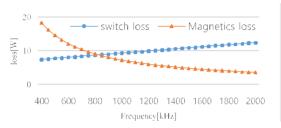

제안 3-레벨 LLC 공진형 컨버터의 등가회로는 그림 8과 같다. 이 때, 입력전압과 1차 측으로 반영된 부하의 등가 임피던스는 다음과 같이 나타낼 수 있다.

$$V_{s1} = \frac{V_{in}}{\pi} sin(\omega_s t)$$

(18)

$$R_e = \frac{8}{\pi^2} n^2 R_O {19}$$

Fig. 8. Equivalent circuit of proposed converter.

Fig. 9. The voltage conversion ratio by the  $\lambda$  and  $Q_e$ .

이를 이용하여 공진탱크의 전압변환비를 도출하면 다 음과 같다[5]

$$\frac{V_{pri1}}{V_{s1}} = H(j\omega_s) = \frac{1}{\sqrt{(1 + \lambda(1 - \frac{1}{F^2}))^2 + (Q_e(F - \frac{1}{F}))^2}}$$

(20)

이때.  $Q_e = Z_0/R_e, \lambda = L_r/L_m, F = f_e/f_r, Z_0 = \sqrt{L_r/(2C_r)}$  of  $\Gamma$ .

식 (17)과 식 (20)을 이용하여 도출한 제안회로의 입 출력전압변환비는 식 (21)과 같다.

$$\frac{V_O}{V_{in}} = \frac{1}{4n\sqrt{(1+\lambda(1-\frac{1}{F^2}))^2 + (Q_e(F-\frac{1}{F}))^2}}$$

(21)

λ의 변화에 따른 공진탱크의 전압변환비는 그림 9(a) 와 같으며, Qe의 변화에 따른 공진탱크의 전압변화비는 그림 9(b)와 같다. 그림 9(a)에 보이는 바와 같이 λ가 커 질수록 작은 주파수 변화를 통해 큰 전압변환비를 얻을

TABLE I EQUATIONS FOR LOSS ANALYSIS

|           | Loss                      | Equation    |                                                                                        |

|-----------|---------------------------|-------------|----------------------------------------------------------------------------------------|

| Switch    | Primary<br>MOSFET         | Conduction  | $i_{sw\_rms}^2$ • $R_{ds(on)\_sw}$                                                     |

|           |                           | Turn off    | $\frac{1}{2} \bullet \frac{V_{in}}{2} \bullet i_{Lm\_peak} \bullet t_f \bullet f_{sw}$ |

|           |                           | Gate driver | $C_{iss\_sw}$ • $V_{gs\_sw}^2$ • $f_{sw}$                                              |

|           | Secondary<br>SR<br>MOSFET | Conduction  | $i_{SR\_rms}^2$ • $R_{ds(on)\_SR}$                                                     |

|           |                           | Gate driver | $C_{\!iss\_S\!R} ullet V_{gs\_S\!R}^2 ullet f_{sw}$                                    |

| Magnetics | Transformer               | Core        | $P_{cv}$ • $volume_{trans.}$                                                           |

|           |                           | Copper      | $(i_{Lr\_rms}^2 + i_{SR\_rms}^2) \cdot R_{dc\_trans.}$                                 |

|           | Inductor                  | Core        | $P_{cv}$ • $volume_{inductor}$                                                         |

|           |                           | Copper      | $i_{Lr\_rms}^2$ • $R_{dc\_inductor}$                                                   |

수 있다. 하지만, λ가 크다는 것은 자화 인덕턴스가 작다 는 의미이므로 순환전류와 도통전류가 커져 손실이 증가 하는 단점이 있다. 또한, 그림 9(b)에 보이는 바와 같이 Qe가 작을수록 동작 주파수 범위가 넓으며, 전압변환비 가 큰 것을 알 수 있다. 하지만, Q<sub>o</sub>가 작다는 것은 자화 인덕턴스가 작다는 의미이므로 순환전류와 도통전류가 커져 손실이 증가하는 단점이 있다. 따라서 본 논문에서 는 입출력 전압변환비를 만족시킬 수 있으며 손실이 작 은 스위칭 주파수 및 공진탱크의 최적설계를 진행하였다.

#### 3.2 제안회로 손실 분석 및 설계

표 1은 제안회로의 주요 손실요소인 스위치 손실과 자성체 손실을 나타내었으며, 스위치 손실은 1차 측 스 위치의 도통손실, 턴 오프 손실, 게이트 드라이버 손실  $\frac{V_{pri1}}{V_{s1}} = H(j\omega_s) = \frac{1}{\sqrt{(1+\lambda(1-\frac{1}{P^2}))^2 + (Q_e(F-\frac{1}{P}))^2}}$  (20) 과 2차 측 동기정류기의 도통 손실, 게이트 드라이버 손실 실을 구하였다 $^{[6]}$ . 제안회로는 스위칭 주파수와 공진 주 실을 구하였다<sup>[6]</sup>. 제안회로는 스위칭 주파수와 공진 주 파수가 동일한 F=1인 지점에서 동작한다고 가정하였으 므로, 1차 측 스위치는 ZVS 턴 온 되기 때문에 턴 온 손실을 제거하였으며, 2차 측 동기정류기는 바디 다이오 드가 도통한 이후 턴 온이 되고, 전류가 0이 된 이후 스 위치가 꺼지는 ZCS 턴 오프 이므로, 턴 온 및 턴 오프 손실을 제거하였다. 또한, 자성체의 경우 주요 손실인 동손과 철손을 고려하였다. 철손은 스테인메츠 방정식을 통해 도출하였으며, 동손은 DC 손실을 고려하여 권선 저항의 손실을 구하였다<sup>[7]</sup>.

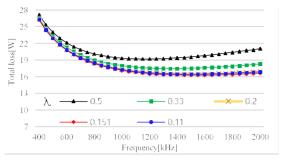

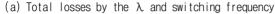

> 제안회로는 스위칭 주파수(400kHz~2MHz) 및 λ(0.11 ~0.5)를 기준으로 스위치 손실 및 자기소자 손실분석을 통해 설계를 진행하였다. 그림 10(a)는 λ 및 주파수 변화 에 따른 손실분석 결과, λ=0.151에서 가장 손실이 작은 것을 알 수 있다. 이를 통해 λ=0.151일 때, 스위칭 주파 수에 따른 스위치 손실 및 자기소자 손실은 그림 10(b)과

# (b) Switch & magnetics losses by the switching frequency @ $\lambda$ =0.151

Fig. 10. Loss analysis of proposed circuit by the  $\lambda$  and switching frequency.

TABLE II PRINCIPAL PARAMETERS FOR PROPOSED CIRCUIT

| Items                              | Values       |  |

|------------------------------------|--------------|--|

| Input voltage                      | $390 V_{dc}$ |  |

| Output voltage                     | 19.5V        |  |

| Output power/current               | 350W/17.95A  |  |

| Turn ratio                         | 5:5:1:1      |  |

| $L_m(L_{m1}=L_{m2})$               | 15.15uH      |  |

| $L_r(L_{r1}=L_{r2})$               | 2.29uH       |  |

| $C_r(C_{r1}=C_{r2}=C_{r3}=C_{r4})$ | 5.5nF        |  |

TABLE III

COMPARISON OF MOSFET CHARACTERISTICS

ACCORDING TO VDS

| Items                                                     | IPL60R360P6S | BSC16DN25NS3 |

|-----------------------------------------------------------|--------------|--------------|

| Drain-source voltage breakdown voltage (V <sub>ds</sub> ) | 650V         | 250V         |

| Continuous drain current (I <sub>d</sub> )                | 11.3A        | 10.9A        |

| Drain-source on-state resistance $(R_{ds(on)})$           | 0.36Ω        | 0.165Ω       |

| Input capacitance (C <sub>iss</sub> )                     | 1010pF       | 690pF        |

같다. 표 1의 수식에 보이는 바와 같이 주파수가 증가함에 따라 스위치 손실을 계속 증가하는 것을 알 수 있으며, 자기소자 손실의 경우 주파수 증가에 따라 감소하는 것을 알 수 있다. 제안회로는 손실 분석 결과를 토대로 1MHz를 구동 주파수로 선정하였으며, 자화인덕턴스는 1차 측 MOSFET의 ZVS 조건을 만족시켜주는 값으로 15.15uH를 사용하였으며, 공진 인덕턴스는  $\lambda$ =0.151을 만

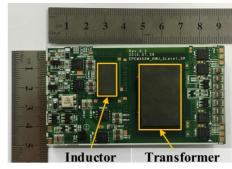

(a) Top-view

(b) Cross-view

Fig. 11. 350W-prototype of proposed circuit.

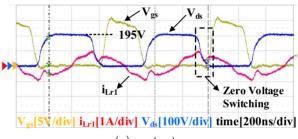

(a) no load

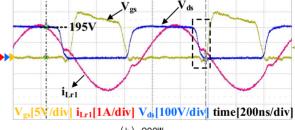

(b) 200W

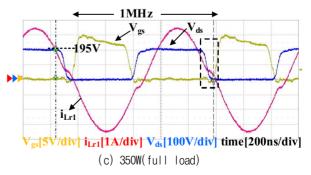

Fig. 12. Experimental waveforms of proposed converter (Vgs, Vds, iLr1).

족하는 2.29uH를 사용하였다. 공진 커페시턴스는 스위칭 주파수와 동일한 공진 주파수를 만족시켜주기 위하여 5.5nF으로 선정하였다.

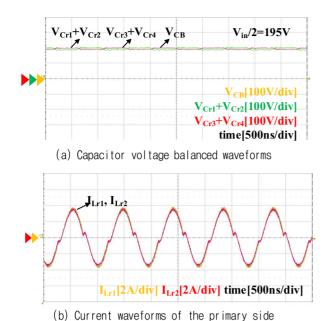

Fig. 13. Voltage and current balancing waveforms @ full load.

#### 4. 제안 3-레벨 LLC 공진형 컨버터 실험결과

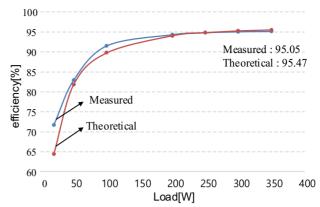

제안 3-레벨 LLC 공진형 컨버터의 타당성 검증을 위 해 그림 11과 같이 350W급 1MHz 시작품을 제작하였으 며, 실험에 사용된 주요 파라미터는 표 2와 같다. 트랜 스포머의 턴 비는 입출력 관계식을 이용하여 5:5:1:1로 선정하였다. 표 3은 하나의 일례로 일반적인 LLC 공진 형 컨버터에 적용되는 650V 내압의 MOSFET와 제안회 로에 적용된 250V 내압의 MOSFET를 비교한 표이다. 앞서 설명한 바와 같이 제안회로에 적용된 MOSFET는 작은 C<sub>iss</sub>, R<sub>ds(on)</sub>을 통하여 스위치의 게이트 구동 손실 및 도통 손실이 저감되는 장점을 갖는다. 그림 12는 부 하 별 제안회로의 M4 스위치의 Gate 양단전압, 드레인-소스 양단전압 및 1차 측 공진 인덕터 전류를 나타내었 다. 앞서 고찰한 바와 같이 자화인덕턴스에 의한 ZVS가 무부하 조건을 포함한 모든 부하조건에서 만족하며, 스 위치 양단전압 또한 모든 조건에서 입력전압의 절반인 195V로 클램프 되는 것을 알 수 있으며, 350W에서 스 위칭 주파수는 1MHz로 동작하는 것을 확인하였다. 그 림13은 밸런싱 커패시터를 이용한 전압평형과 공진 인 덕터의 전류 평형이 보장되는 파형을 나타내고 있다. 그 림 13(a)에 보이는 바와 같이 밸런싱 커패시터 전압과  $C_{r1}$ ,  $C_{r2}$  커패시터 전압의 합, 그리고  $C_{r3}$ ,  $C_{r4}$  커패시터 전압의 합이 모두 동일하게 입력전압의 절반인 195V로 일정하게 유지되는 것을 확인하였다. 또한 그림 13(b)에 보이는 바와 같이 트랜스포머 1차 측 공진 인덕터 전류 가 모두 동일한 것을 알 수 있다. 그림 14는 부하에 따 른 이론적 분석 및 실측 효율을 비교하였다. 그림 14에 보이는 바와 같이 이론적 분석과 실측 효율이 전반적으로 근사하다는 결과로부터 앞서 이론적 분석을 통해 고찰된

Fig. 14. Theoretical and measured efficiency comparison by load.

제안회로의 우수성과 각부 소자 설계가 타당함을 알 수 있다. 제안회로는 최대 부하인 350W에서 95.05%의 고효율을 달성하였으며, 제안회로의 체적을 고려하였을 때, 106W/in<sup>3</sup>의 고전력밀도를 달성하였다.

#### 5. 결 론

본 논문에서는 스위치의 전압 스트레스 저감을 통해 스위치의 손실을 저감시킬 뿐만 아니라 1MHz의 고주파 수 구동으로 리액티브 소자를 소형화시킴으로써 고효율 및 고전력밀도를 달성할 수 있는 3-레벨 LLC 공진형 컨버터를 제안하였다. 350W급 시작품을 제작하여 이론 적 분석의 타당성을 제시하였으며, 실험을 통하여 스위 치 양단전압이 정확히 입력전압의 절반으로 클램프되며 모든 부하 조건에서 스위치의 ZVS 동작과 전압평형 및 전류평형이 보장되는 것을 확인하였다. 최대 효율은 95.05%를 달성하였으며, 전력밀도는 106W/in<sup>3</sup>로 고전력 밀도를 달성하였다. 뿐만 아니라 밸런싱 커패시터와 기 본 모듈의 추가만으로 멀티레벨 LLC 공진형 컨버터로 확장에 용이한 구조적 특성을 가진다. 따라서 기본 모듈 의 추가로 전압 스트레스를 V<sub>in</sub>/n으로 더욱 저감 가능하 므로 입력전압이 높은 다양한 어플리케이션에 널리 응 용될 것으로 예상된다.

본 논문은 SoluM Inc.의 Module Power 개발사업과 한국항공우주연구원의 정지궤도복합위성 개발사업(NTIS-2011-0030431) 지원에 의하여 연구되었음을 밝힙니다.

#### References

T. Baltynov, V. Unni, and S. E. Madathil, "The world's first high voltage GaN-on-Diamond power semiconductor devices," *Solid-State Electronics* 125, pp. 111-117, Jul. 2016.

- [2] Y. Gu, Z. Lu, L. Hang, Z. Qian, and G. Huang, "Three-level LLC series resonant DC/DC converter," IEEE Trans. Power Electron., Vol. 20, No. 4, pp. 781–789, Jul. 2005.

- [3] F. Canales, P. Barbosa, C. Aguilar, and F. C. Lee, "A high-power-density DC/DC converter for high-power distributed power systems," in Proc. IEEE PESC, pp. 11–18, Jun. 2003.

- [4] B. Lu, W. Liu, Y. Liang, F. C. Lee, and J. D. van Wyk, "Optimal design methodology for LLC resonant converter," in *Proc. IEEE APEC*, pp. 533–538, Apr. 2006.

- [5] R. W. Erickson and D. Maksimovic, Fundamentals of power electronics(2nd edition), Springer Science+Business Media New York, 2004.

- [6] C. H. Yang, T. J. Liang, K. H. Chen, J. S. Li, and J. S. Lee, "Loss analysis of half-bridge LLC resonant converter," in *Future Energy Electronics Conference (IFEEC)*, pp. 155–160, Nov. 2013.

- [7] C. W. T. Mclyman, Transformer and inductor design handbook, Marcel Dekker, 2004.

## 구현수(具泫秀)

1989년 2월 1일생. 2013년 국민대 전자정보 통신대학 전자공학부 졸업. 2015년 동 대학 원 전자공학부 졸업(석사). 2015년 ~현재 동 대학원 전자공학부 박사과정.

#### 김효훈(金孝勳)

1990년 4월 19일생. 2015년 국민대 전자정 보통신대학 전자공학부 졸업. 2017년 동 대 학원 전자공학부 졸업(석사). 2017년 ~현재 Pulse electronics 기술지원팀 FAE.

#### 한상규(韓翔圭)

1973년 12월 14일생. 1999년 부산대 전기공학과 졸업. 2001년 한국과학기술원 전자전산학과 졸업(석사). 2005년 동 대학원 전자전산학과 졸업(공박). 2005년 한국과학기술원 정보전자연구소 박사후연구원. 2005년 ~현재 국민대 전자공학부 교수.