# Individual DC Voltage Balancing Method at Zero Current Mode for Cascaded H-bridge Based Static Synchronous Compensator

## Zezhou Yang\*, Jianjun Sun<sup>†</sup>, Shangsheng Li\*\*, Zhiqiang Liao\* and Xiaoming Zha\*

**Abstract** – Individual DC voltage balance problem is an inherent issue for cascaded H-bridge (CHB) based converter. When the CHB-based static synchronous compensator (STATCOM) is operating at zero current mode, the software-based individual DC voltage balancing control techniques may not work because of the infinitesimal output current. However, the different power losses of each cell would lead to the individual DC voltages unbalance. The uneven power losses on the local supplied cell-controllers (including the control circuit and drive circuit) would especially cause the divergence of individual DC voltages, due to their characteristic as constant power loads. To solve this problem, this paper proposes an adaptive voltage balancing module which is designed in the cell-controller board with small size and low cost circuits. It is controlled to make the power loss of the cell a constant resistance load, thus the DC voltages are balanced in zero current mode. Field test in a 10kV STATCOM confirms the performance of the proposed method.

**Keywords**: Static Synchronous Compensator (STATCOM), FACTS, High voltage power converters, Multilevel converter, Voltage Source Converter (VSC), DC voltage control

#### 1. Introduction

Cascaded H-bridge (CHB) multilevel converter is the most popular topology for static synchronous compensator (STATCOM) in medium high voltage system, owing to its ability of achieving high voltage and high power with low rate switches. The Individual DC voltage balancing problem is an inherent issue of CHB-multilevel converter, and maintaining the DC voltages at a rated value is the fundament for a STATCOM to function properly [1-5]. When the STATCOM is operating at zero current mode (such as stand by status), the main cause of individual DC voltage unbalance is the uneven power losses of different H-bridge cells, including the uneven losses in capacitors, absorption circuits, switching devices, diodes and drive circuits.

Many individual DC voltage balancing control strategies have been proposed and they can be divided into two categories. The first category is based on internal individual voltage controllers [5-11]. By detecting the output current, these methods regulate the fundamental output voltages respectively to control the fundamental energy exchange of each cell. The second category is the sorting method [12, 13], such as predictive sorting algorithm [14-16], distributed commutations modulation [17, 18]. These methods can realize DC voltage balance in the modulation progress by selectively distributing the PWM pulse (or carrier) to cells depending on the DC voltage rank list and the current

detection.

However, these individual DC voltage balancing control methods may not work when a star-connected STATCOM is operating at the zero current mode. The zero current mode means the STATCOM has been started up and connected to the grid but the output current is nearly zero. This mode is frequent when the STATCOM is in debugging or stand by stage. The current is too low to be accurately extracted from the noise in zero current mode, so all these aforementioned individual DC voltage balancing methods may not function properly. In addition, delta-connected STATCOM may suffer less for this problem, because there can be a circling current within the delta-connected three phases without any grid power exchange, so aforementioned DC voltage balancing methods can still be utilized. But the circling current induced power loss will decrease the efficiency.

Ref. [19] has proposed a modified sorting algorithm to balance DC voltages in zero current mode by commutating the pulses in the middle of every switching periods. But the doubled switching frequency is the main drawback of this method, which greatly increases the power loss and imposes a heavy strain on the heat dissipation, especially in high voltage applications. Thus, the industrial methods to maintain DC voltage balance in zero current mode are mainly based on hardware, such as parallel resistors (or with an additional switch) on the DC bus. These hardware modules are designed to balance the power losses of each cell, thereby balancing the DC voltages. These methods are easy to be implemented, but the additional components induce some drawbacks on the cost, size and efficiency.

This paper focuses on the individual DC voltage balance

<sup>†</sup> Corresponding Author: School of Electrical Engineering Wuhan University Wuhan, China. (jjsun@whu.edu.cn)

School of Electrical Engineering Wuhan University Wuhan, China.

<sup>\*\*</sup> Wuhan Keliyuan Electric Co., Ltd. Wuhan, China. Received: March 23, 2017; Accepted: September 4, 2017

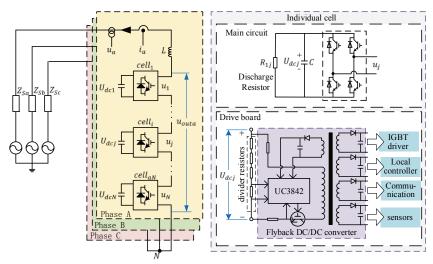

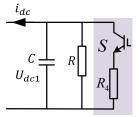

Fig. 1. Structure of star-connected STATCOM and individual H-bridge cell

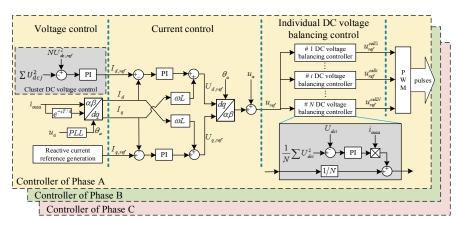

Fig. 2. CHB based STATCOM control system composed of three loops, i.e., cluster voltage control loop (outer loop), current control loop (inner loop) and individual DC voltage balancing loop

problem of a star-connected STATCOM (see Fig. 1) at zero current mode. Firstly, the power loss model of the STATCOM is built, and the traditional DC voltage balancing methods are briefly analyzed. Secondly, the reason of voltage unbalance in zero current mode is analyzed. Thirdly, based on the analysis, a small size and low cost module is designed in the cell-controller board to balance the DC voltages. A series of experiments are carried out to verify the validity of the method. At last, a comparison is carried out among 3 methods: the proposed controllable resistor on the cell-controller board, the parallel resistor on the DC bus and the controllable resistor on the DC bus. Which indicates that the proposed method is the most economical choice for the DC voltage balancing of the STATCOM at zero current mode.

## 2. Star Connected Statcom and its Control System

Fig. 1 shows the structures of a typical star-connected

STATCOM and the individual H-bridge cell.  $Z_{sa}$ ,  $Z_{sb}$ ,  $Z_{sc}$  are the impedances of the grid;  $u_a$ ,  $u_b$ ,  $u_c$  are the sampled voltages of the point of common connection (PCC);  $i_{outa}$ ,  $i_{outb}$ ,  $i_{outc}$  are the sampled output currents of the STATCOM; L is the output filter of the STATCOM;  $u_{outa}$ ,  $u_{outb}$ ,  $u_{outc}$  are the overall voltages of the cascaded chains; N is the number of the H-bridge cells in a chain;  $u_1$ ,  $u_2 \cdots u_j \cdots u_N$  are the output voltages of each Hbridge cell;  $u_{dc1}$ ,  $u_{dc2} \cdots u_{dcj} \cdots u_{dcN}$  are the DC bus voltages of each H-bridge cell in a chain.

To implement the measurement, communication, control and gate drive of the four IGBTs, a local cell-controller is required in every cell and usually supplied by a 15V (or 24V) DC source. Due to the high voltage level of the CHBbased STATCOM, it is impossible to introduce the 15V DC sources from somewhere else into the H-bridge cell. Hence, all the cell-controllers are local supplied by the DC capacitor of the H-bridge with a small DC/DC converter (e.g. fly-back converter in Fig. 1).

Fig. 2 displays the overall control block diagram of CHB-based STATCOM. It is a dq-based multi-loop control

strategy, where the outer loop is designed to generate the daxis and q-axis reference current, and the inner loop aims at controlling the output current to follow its reference. To obtain all the dq quantities, a Phase Lock Loop (PLL) is used to estimate the transformation angle  $\theta$  of the grid voltage. Since the dq transformation is synchronized with the grid voltage, the d-axis and q-axis can be defined as active power axis and reactive power axis, respectively. Consequently, the d-axis reference current  $I_{d-ref}$  can be used to control the total capacitor voltages of each cluster; and the q-axis reference  $I_{q-ref}$  is a given reactive current output instruction, or it is generated by the controlling of the AC grid voltage.

The energy based cluster DC voltage control [2] is designed for compensating the STATCOM losses. The inner current control loop is a typical dq decoupling current controller based on PI regulators. It generates d-axis and q-axis reference voltage. By transforming them into abc coordinate system, the original modulation references of the three phases are obtained. Ideally, the original modulation reference should be simultaneously applied to all the H-bridge cells in one cluster.

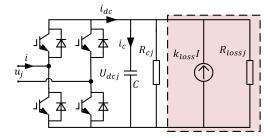

To keep the STATCOM stable, the DC voltage balancing control is also necessary to compensate the uneven power loss of different cells. Usually, the power loss of the H-bridge cell can be modeled as in Fig. 3. It is divided into the series-loss and the parallel-loss. The series-loss is positively correlated to the AC current amplitude I and modeled as the current source  $k_{loss}I$ , including IGBT conduction losses, switching losses and output filter loss. The parallel-loss is positively correlated to the DC voltage and modeled as the resistor  $R_{lossj}$ , including the IGBT offstate losses, the capacitor loss, etc.

Based on the power loss model, the power flow in the H-bridge cell is derived as (1), where  $R_j = R_{cj} / / R_{lossj}$ .

$$u_{j}(t)i(t) = U_{dcj}(t)C\frac{dU_{dcj}(t)}{dt} + \frac{U_{dcj}^{2}(t)}{R_{i}} + U_{dcj}(t)k_{loss}I \quad (1)$$

By ignoring the switching frequency ripples, the AC output voltage and current of the H-bridge cell are simplified into (2) and (3), where  $\varphi_j$  is the power angle of the AC output. Thus, (1) is simplified into (4).

$$u_{j}(t) = U_{j} \sin \omega t = M_{j} U_{dcj}(t) \sin \omega t$$

(2)

Fig. 3. Power loss model of the cell

$$i(t) = I\sin(\omega t + \varphi_j) \tag{3}$$

$$C\frac{dU_{dcj}(t)}{dt} = \frac{1}{2}M_{j}I[\cos\varphi_{j} - \cos(2\omega t + \varphi_{j})] - \frac{U_{dcj}(t)}{R_{j}} - k_{loss}I$$

(4)

Since this paper concentrates on the long time DC voltage balancing issue of the CHB converter, the second harmonic power ripple can be ignored, hence, the power flow function is simplified into (5).

$$C\frac{dU_{dcj}(t)}{dt} = \frac{1}{2}M_{j}I\cos\varphi_{j} - \frac{U_{dcj}(t)}{R_{i}} - k_{loss}I$$

(5)

The left side of (5) represents the charge current of the DC capacitor, and the components on the right side of (5) represent the DC current provided by the AC side, the current of the parallel-loss, and the current of the series-loss

In the steady state, (5) should equal 0 to keep the DC voltage stable. Under a symmetrical control and modulation method, the AC side power exchange of each cell is considered to be the same. On the other hand, the uneven power loss caused by the divergence of the components in different cells is unavoidable. It means that when the Eq. (5) of some cells equals 0, some others must not. This explains the reason for DC voltage unbalance.

Eq. (5) also shows the opportunities for DC voltage balancing methods. There are two parts in (5),  $M_j cos \phi_j$  and  $R_j$ , can be controlled to make (5) equal 0. Which signifies two different kinds of DC voltage balancing strategies: the AC side software-based DC voltage balancing strategy and the DC side hardware-based DC voltage balancing strategy.

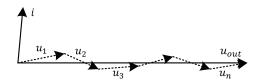

There are different kinds of software-based DC voltage balancing methods [2-13] (including the one in Fig. 2), but, directly or indirectly, they all act up to the principle as shown in Fig. 4. According to the detected fundamental current phase and DC voltages, these methods change the AC side voltage of each cell to control the AC side power exchange.

However, when the AC side current is too low to be detected accurately from the noise, the output of these DC voltage balancing controllers would deviate. It makes the software-based DC voltage balancing controller invalid under zero current mode.

The hardware-based DC voltage balancing methods

**Fig. 4.** Sketch of the software-based DC voltage balancing strategy

adjust the power loss resistor  $R_i$  by adding a shunt connected resistor or a switching resistor branch to the DC bus. These methods do not depend on the output current, so their function is not limited by the operating point of the STATCOM, and they can still work under zero current mode. But the hardware based methods have significant drawbacks on cost and size, due to the high voltage resistors and switches in the added branch. The purpose of this paper is to propose a novel low voltage hardwarebased method to overcome these drawbacks.

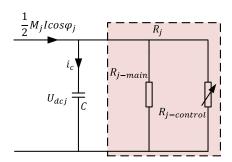

### 3. DC Voltage Unbalance Analysis at Zero Current Mode

Because the output current is almost zero, the serieslosses presented by the current source is negligible at the zero current mode. The parallel-loss represented by  $R_i$ includes two parts: the power loss on the main circuit components (including the power loss on the discharge resistor  $R_{cj}$ ) and the power loss on the local cell-controller, which are modeled as resistor  $R_{j-\text{main}}$  and resisitor  $R_{j-\text{control}}$ , respectively. However, the power losses on the cell-controller board should be specially considered, because it is neither positively correlated to the output current nor the DC voltage. The power losses of the sensor, digital controller, communication model and the drive circuits are almost constant, so the local cellcontroller board is nearly a constant power load. Hence, the resistor  $R_{j-\text{control}}$  is a variable resistor.

**Table 1.** parameters of the tested H-bridge cell

| Main circuit                   |             |  |  |  |  |

|--------------------------------|-------------|--|--|--|--|

| IGBT mode                      | FF450R17ME4 |  |  |  |  |

| DC Capacitor value             | 4×600 uf    |  |  |  |  |

| IGBT switching frequency       | 600 HZ      |  |  |  |  |

| Rated AC voltage (RMS)         | 481V        |  |  |  |  |

| Rated AC current (RMS)         | 247A        |  |  |  |  |

| Rated DC voltage               | 840V        |  |  |  |  |

| DC discharge resistor          | 50kΩ        |  |  |  |  |

| cell-controller                |             |  |  |  |  |

| MOSFET of flyback              | IRF640NS    |  |  |  |  |

| Switching frequency of flyback | 50 kHz      |  |  |  |  |

| Local controller chip          | CPLD 1270   |  |  |  |  |

| IGBT drive chip                | M57962AL    |  |  |  |  |

Fig. 5. Power loss model of the cell at zero current mode

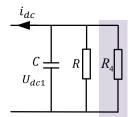

According to (5) and ignoring the series-losses, the model of the H-bridge cell is changed into the one as in Fig. 5.

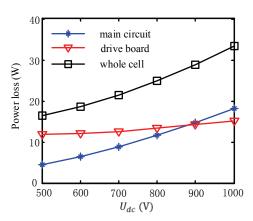

We carried out a series of experimental tests to measure the power losses of the whole cell and the cell-controller in zero current mode, respectively. At the same time, the power losses on the main circuit are calculated consequently. The parameters of the tested H-bridge cell are as shown in Table 1. The data of the test results are shown in Fig. 6.

Fig. 6 verified that the power loss on the main circuit is nearly in direct proportion to the DC voltage, while the power loss on the cell-controller board is almost a constant power load. And it also shows that the total power losses on an H-bridge at the zero current mode are about tens of watts.

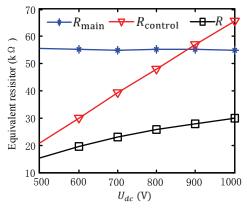

By the data in Fig. 6, the equivalent resistances of these power losses can be easily calculated. The curves of  $R_{j-\text{main}}$ ,  $R_{j-\text{control}}$  and  $R_{j}$  versus DC voltage are presented in Fig. 7. They reveal that the main circuit is nearly a constant resistance load, while the cell-controller is nearly a constant power load. And the overall equivalent resistor  $R_i$  is positively correlated to the DC voltage.

Fig. 6. Power losses under different DC voltages in zero current mode

Fig. 7. Equivalent resistors under different DC voltages in zero current

Fig. 8. Equivalent circuit of the cascaded chain at zero current mode

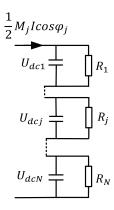

Because the current  $\frac{1}{2} M_j I \cos \varphi_j$  are the same for all the cells in one CHB chain, we can connect the power loss model of each cell in series. Hence the equivalent circuit of the CHB chain is obtained as in Fig. 8.

By solving the Eq. (5), the expression of the DC voltage is obtained as (6). After a long time at zero current mode, the DC voltage is as (7).

$$U_{dcj}(t) = \frac{1}{2} M_j I \cos \varphi_j R_j - \frac{1}{2} e^{-t/CR_j}$$

(6)

$$U_{dcj} = \lim_{t \to \infty} U_{dcj}(t) = \frac{1}{2} M_j I \cos \varphi_j \cdot R_j$$

(7)

Thus, we have (8).

$$\frac{U_{dcj}}{R_i} = \frac{1}{2} M_j I \cos \varphi_j \tag{8}$$

According to the model in Fig. 8, we have (9).

$$\frac{U_{dc1}}{R_1} = \frac{U_{dc2}}{R_2} = \dots = \frac{U_{dcj}}{R_j} = \dots = \frac{U_{dcN}}{R_N}$$

(9)

It shows that the equivalent resistors  $R_i$  work as a voltage-sharing circuit. According to the voltage sharing principle (9), the ratios among DC voltages are the same with the ratios among the resisters.

If the cell-controller is not considered,  $R_i$  only involves  $R_{j-\text{main}}$  which is a constant resistor. Thus the DC voltages will reach a stable state corresponding to (9). Because  $R_{i-\text{main}}$  may vary from cell to cell, the stable value of the DC voltages may be different. However the difference will not be very big, which is acceptable in the zero current mode.

If the cell-controller is considered, influenced by the variable resistor  $R_{j-\text{control}}$ , the overall equivalent resistor  $R_{j}$ decreases with the decrement of the DC voltage, vice versa. Assuming the DC voltage of one cell is a little higher than others, the  $R_i$  would also be a little higher than that of

others. Then, according to the voltage sharing principle (9), the DC voltage of the cell would become much higher, which would lead to a much higher  $R_i$ . Thus a positive feedback is constituted, resulting in the divergence of DC voltages. Although the power loss differences among the cells are small, when the STATCOM keeps operating at the zero current mode for a long time, this positive feedback loop would pose a high risk of crash on the system.

## 4. The DC Voltage Balancing Module in the Cell-Controller Board

Theoretically, we can choose an appropriate resistor to adjust the power loss of the cell to a unified value, thus the DC voltage can be balanced at the zero current mode. But the power losses of the cells would vary with time because the parameters of the components may change with temperature and many other factors during the life time of the STATCOM. The resistor chosen at first may mismatch the requirement of the loss balancing after a period of time. So, it is invalid to use different resistors to adjust the power loss of the cells. This problem is overcame by the adaptive load designed in this paper. Moreover, to use the same resistor and switch in all cells helps a lot for the manufacture processes.

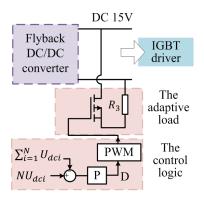

The proposed DC voltage balancing module is essentially an adaptive load implemented by low voltage MOSFET and resistors in the cell-controller board as shown in Fig. 9. This module only works at zero current mode. The working principle of the module is adaptively increasing the power loss on the cell-controller when the DC voltage is higher than the average value. DC voltage of the cell  $U_{dci}$ is compared with the average DC voltage of the cluster  $\frac{1}{N} \Sigma U_{dci}$ . The difference of them is transferred into a duty rate D through a P (or PI) controller. The duty rate D is used to control the switch-on time of the MOSFET through a PWM modulator. If the  $U_{dci}$  is larger than the average, the MOSFET is turned on to increase the power loss on the cell. The parameters of the P (or PI) controller can be used to set the adjusting speed of the module. By

Fig. 9. The schematic of the module in the cell-controller board

this process, the overall equivalent resistance R is adaptively reduced to the average value, which results in balanced DC voltages.

Theoretically, the rated power of the voltage balancing module should be greater than the maximum deviation of the power losses on different cells.

The power loss of 12 H-bridge cells at zero current mode are measured under 840V DC voltage. Table 2 presents the results. It shows that the power loss deviation of these cells is 2.2W, which means the rated power of the adaptive load should be higher than 2.1 W.

Reasonably, higher rated power of the adaptive load means higher DC voltage balancing ability. However, the rated power of the adaptive load is limited by the power rate of the DC/DC supply on the local controller board.

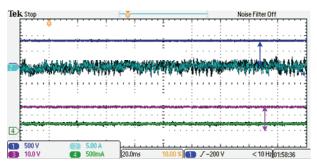

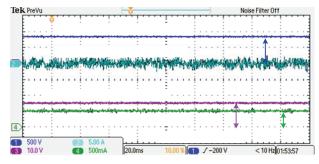

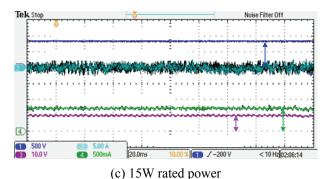

The rated power of the fly-back converter in the local controller board is usually designed to be 20W-50W. But the adaptive load is connected to one of the output ports of the fly-back converter, so the rated power of the adaptive load should be limited lower. The parameters of the flyback converter used in this paper are as shown in Table 3. In order to evaluate the impact of the adaptive load on the output of the fly-back converter, three different adaptive loads, 2.25 W, 7.5 W, and 12.5W, are implemented on the local controller board. By keeping the switch of the adaptive load on, the adaptive loads consumed the rated power. The results are recorded as in Fig. 10.

Fig. 10 shows that high rated power of the adaptive load module would distort the DC bus voltage of the IGBT driver, which puts the operation of the main circuit at risk. So the rated power of the adaptive load module should be designed as low as possible in the precondition of being larger than the power losses deviation of the H-bridge cells at zero current mode. Thus, we chose the 2.25W adaptive load module for the STATCOM in this paper.

The layout of the 2.25W adaptive load module is as shown in Fig. 11. Because the close loop control based module do not highly depend on the precision of the resister, a normal 5% tolerance resister can be adopted. The

**Table 2.** Power loss deviation at zero current mode

| Cell # | Total loss | Controller loss | Cell # | Total loss | Controller loss |

|--------|------------|-----------------|--------|------------|-----------------|

| 1      | 27.8       | 11.5            | 7      | 28.3       | 12.1            |

| 2      | 27.7       | 11.8            | 8      | 28.4       | 11.8            |

| 3      | 28.2       | 12.5            | 9      | 26.7       | 11.3            |

| 4      | 27.5       | 12.1            | 10     | 26.3       | 11.0            |

| 5      | 26.4       | 11.2            | 11     | 27.5       | 12.4            |

| 6      | 27.2       | 11.7            | 12     | 28.4       | 12.3            |

**Table 3.** Paramiters of the fly-back converter

| Item                                 | Value   |

|--------------------------------------|---------|

| Controller chip                      | UC3842  |

| MOSFET                               | 2SK1317 |

| Switching frequency                  | 20 kHz  |

| Rated power of the converter         | 40 W    |

| Capacitor on the IGBT driver bus     | 1000 μF |

| Rated voltage of the IGBT driver bus | 15 V    |

control logic can also be easily realized in the local control chip of the cell-controller. The parameters are shown in table 2. The local CPLD sends out the switching signal, then through the amplification and isolation of a photo coupler, the switching signal is used to drive the MOSFET. Fig. 11 shows that the size of the proposed module is very small, and the Table 4 shows that its price is very low. These are two most important advantages of the proposed

(a) 2.25W rated power

(b) 7.5W rated power

Fig. 10. Impact of the adaptive load with different rated powers on the Hbridge cell and its local supply converter in the controller board

**Table 4.** Parameters of the proposed module

| Item                       | Value               |  |

|----------------------------|---------------------|--|

| MOSFET model               | 4N90C               |  |

| MOSFET drive               | photocoupler TLP421 |  |

| Resister $R_3$             | 102Ω                |  |

| MOSFET switching frequency | 1 kHz               |  |

| Rated power                | 2.25 W              |  |

| Size                       | 15×40 mm            |  |

| Cost                       | \$ 0.7              |  |

Fig. 11. The layout of the module in the cell-controller board

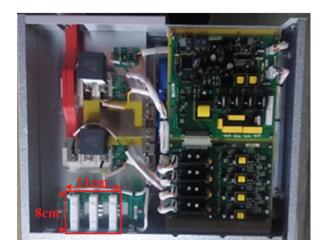

Fig. 12. 12-cell-cascaded 10 kV STATCOM

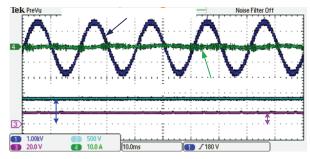

Fig. 13. Basic operating conditions of the STATCOM at zero current mode

method.

This adaptive load module has been verified in a 12-cellcascaded 10 kV STATCOM product as shown in Fig. 12. The STATCOM was started up and connected to a 10 kV grid. Some measurements, including the CHB-chain voltage, the AC output current, the DC voltage of one Hbridge cell, and the voltage of 15 V bus in the cell, are presented in Fig. 13 to demonstrate the basic operating conditions at zero current mode. There was still a low amplitude AC current, but it was seriously distorted due to the switching harmonics and sensor noise.

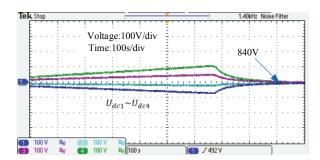

At first, the DC voltage balancing module was deactivated. Since the differences among the power losses on cell-controllers are much smaller than the power level

Fig. 14. DC voltage divergency and the effection of proposed module

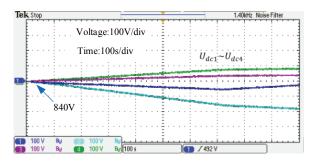

Fig. 15. DC voltgae divergency when the power loss deviation exceeds the ability of the adaptive load

of the DC capacitor, it cost a long time before the divergence of DC voltages becoming significant. Then the DC voltage balancing module was enabled, and the DC voltages were rebalanced in about 5 minutes. The experimental results are shown in Fig. 14.

In order to observe the phenomenon when the power deviation exceeds the rated power of the adaptive load module, we shunt connected a  $100k\Omega$  resistor to the DC bus of one cell. Therefore the power loss of this cell was increased and exceeded the range of the adaptive load module. By repeating the experiment processes, we got the results as in Fig. 15. When the adaptive load module was enabled, the DC voltage divergence of the changed cell was decelerated but not stopped, and the DC voltage balancing progresses of other cells were also influenced.

## 5. Comparison of Three Hardware Based Dc **Voltage Balancing Schedules**

To demonstrate the superiority of the novel method, a comparison is made among the proposed method and the other two hardware based methods. Besides the proposed module in the cell-controller board, the other two methods are a single resistor (as in Fig. 16(a)) and a branch composed of a resistor and a switch in series (as in Fig. 16(b)), which are installed on the DC bus.

A parallel resistor (as shown in Fig. 17) on the DC bus is a popular method. The mechanism is also the voltage sharing principle as shown in Fig. 8. Usually, a high

Fig. 16. Other two hardware based individual DC voltage balancing methods, i.e., (a) a single parallel resistor and (b) a parallel branch composed of a resistor and a switch in series

Fig. 17. H-bridge cell with a parallel resistor on the DC bus

precision resistors are used for the high accuracy of equal voltage sharing. Note the parallel of R and  $R_4$  as  $R_{total}$ . Since the deviation of equivalent resistor R still exists, the additional parallel  $R_4$  can only decrease the deviation of  $R_{total}$ , but not eliminate it. This non-ideal method will also cause the DC voltage divergence if the zero current mode lasts long enough. Moreover, for better balance of  $R_{total}$ , the value of  $R_4$  should be chosen as small as possible, which poses a contradiction on power loss and DC voltage balance.

A parallel branch composed of a resistor and a switch in series is also a controllable load which can function as the proposed module. However, this branch has some advantages and disadvantages induced by the direct connection to the DC bus. The rated voltage of both the switch S and the resistor R4 should be higher than the rated DC voltage. Compared with the module in the cellcontroller board, to achieve the same DC voltage balancing power, the cost is higher and the size is bigger. On the other hand, the advantage of this branch is that it can be designed with higher rated power to enhance better power adjusting ability. However, the divergence of the power losses among the cells are only several watts at zero current mode, and the proposed module is enough for balancing them. Hence it is not necessary to design a high power hardware based DC voltage balancing branch.

The comparative results of the three methods are

**Table 5.** Comparison of the three hardware based methods

| Methods            | Advantages             | Disadvantages          |  |

|--------------------|------------------------|------------------------|--|

| A single parallel  |                        | High loss;             |  |

| resistor on DC bus | Simple                 | Big size;              |  |

| (Fig. 16 (a))      |                        | No-ideal balancing.    |  |

| A parallel branch  | High power rate for DC | High post:             |  |

| on DC bus          | voltage balancing;     | High cost;<br>Big size |  |

| (Fig. 16 (b))      | Ideal balancing.       |                        |  |

| A cell-controller  | Ideal balancing;       | Limited power rate     |  |

| boardbased module  | Small size;            | for DC voltage         |  |

| (Fig. 9)           | Low cost.              | balancing.             |  |

concluded as in Table 3. It shows that the proposed DC voltage balancing module is the most economical method for DC voltage balance of STATCOM at the zero current mode.

#### 6. Conclusions

In this paper, a novel method is proposed to guarantee the DC voltage balance of STATCOM at the zero current mode. Detailed analysis is provided for explaining the DC voltage unbalance mechanism in the CHB chain at zero current mode. The uneven power losses of the cells are the major cause of the individual DC voltage unbalance. Due to constant power load character of the drive board, the DC voltages would finally divergence in zero current mode. The typical DC voltage balancing control methods are restricted by the infinitesimal output current. A cellcontroller board based DC voltage balancing module is proposed to adaptively adjust the power losses of each H-bridge cell. Compared with other DC voltage balancing modules which are directly connected to the DC bus, the proposed method is the most economical method. Experimental results are in good agreements with the theoretical analysis and have confirmed the effectiveness of the proposed method.

#### Acknowledgements

The work is sponsored by Natural Science Foundation of China (51777145) and State Grid Corporation of China science and technology project: Key technologies and equipment of DC step-up power collection and integration for large-scale PV Station.

#### References

- [1] E. Behrouzian, M. Bongiorno and R. Teodorescu, "Impact of switching harmonics on capacitor cells balancing in phase-shifted PWM based cascaded Hbridge STATCOM," IEEE Transactions on Power Electronics, vol. 32, no. 1, pp. 815-824, Jan. 2017.

- [2] Z. Yang, J. Sun, S. Li, M. Huang, X. Zha, Y. Tang,

- "An adaptive carrier frequency optimization method for harmonic energy unbalance minimization in Cascaded H-bridge based active power filter," *IEEE transaction on power electronics*, in press.

- [3] L. Xiong and F. Zhuo, "A novel DC voltage balancing method for cascaded STATCOM," 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, pp. 924-929, 2013.

- [4] Xiong, L.; Zhuo, F., "Chopper controller based DC voltage control strategy for cascaded multilevel STATCOM," *in Journal of Electrical Engineering & Technology*, vol. 9, no. 2, pp. 576-588, 2014.

- [5] H. C. Chen and P. T. Cheng, "A DC bus voltage balancing technique for the cascaded H-bridge STATCOM with improved reliability under grid faults," *IEEE Transactions on Industry Applications*, vol. 53, no. 2, pp. 1263-1270, March-April 2017.

- [6] G. Farivar, B. Hredzak, V. Agelidis, "Decoupled control system for cascaded H-bridge multilevel converter based STATCOM," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 1, pp. 322-331, Jan. 2016.

- [7] A. Fernandez, P. Rodriguez, G. Escobar, C. Pozos, and J. Sosa, "A model-based controller for the cascade H-bridge multilevel converter used as a shunt active filter," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 11, pp. 5019-5028, Nov. 2013.

- [8] J. Barrena, L. Marroyo, M. Vidal, and J. Apraiz, "Individual Voltage Balancing Strategy for PWM Cascaded H-Bridge Converter-Based STATCOM," *IEEE Transactions on Industrial Electronics*, vol. 55, no. 1, pp. 21-29, Jan. 2008.

- [9] J. J. Jung; J. H. Lee; S. K. Sul; G. T. Son; Y. H. Chung, "DC capacitor voltage balancing control for deltaconnected cascaded H-bridge STATCOM considering unbalanced grid and load conditions," *IEEE Trans*actions on Power Electronics, in press.

- [10] Z. Liu, B. Liu, S. Duan, and Y. Kang, "A novel dc capacitor voltage balance control method for cascade multilevel STATCOM," *IEEE Transactions on Power Electronics*, vol. 27, no. 1, pp. 14-27, Jan. 2012.

- [11] Y. Liu, C. Farnell, H. A. Mantooth, J. C. Balda, "Modular Multilevel Converter with High-Frequency Transformers for Interfacing Hybrid DC and AC Microgrid Systems," in Proc. IEEE International Symposium on Power Electronics for Distributed Generation Systems, May, 2014.

- [12] S. Fan, K. Zhang, J. Xiong, and Y. Xue, "An improved control system for modular multilevel converters with new modulation strategy and voltage balancing control," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 358-371, Jan. 2015.

- [13] M. Alvarenga and J. Pomilio, "Voltage balancing and commutation suppression in symmetrical cascade multilevel converters for power quality applications,"

- *IEEE Transactions on Industrial Electronics*, vol. 61, no.11, pp. 5996-6003, Nov. 2014.

- [14] K. Ilves, L. Harnefors, S. Norrga, and H. Nee, "Predictive sorting algorithm for modular multilevel converters minimizing the spread in the submodule capacitor voltages," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 440-449, Jan. 2015.

- [15] C. Townsend, T. Summers and R. Betz, "Multigoal heuristic model predictive control technique applied to a cascaded H-bridge STATCOM," *IEEE Transactions on Power Electronics*, vol. 27, no. 3, pp. 1191-1200, Mar. 2012.

- [16] C. Townsend, T. Summers, J. Vodden, et al., "Optimization of switching losses and capacitor voltage ripple using model predictive control of a cascaded H-bridge multilevel STATCOM," *IEEE Transactions on Power Electronics*, vol. 28, no. 7, pp. 3077-3087, Jul. 2013.

- [17] L. Tarisciotti, P. Zanchetta, A. Watson, S. Bifaretti, J. Clare, and P. Wheeler, "Active DC voltage balancing pwm technique for high-power cascaded multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 11, pp. 6157-6167, Nov. 2014.

- [18] S. Bifaretti, L. Tarisciotti, A. Watson, et al., "Distributed commutations pulse-width modulation technique for high-power AC/DC multi-level converters," *IET Power Electronics*, vol. 5, no. 6, pp. 909-919, 2012.

- [19] E. Behrouzian, M. Bongiorno, R. Teodorescu, and J. Hasler, "Individual capacitor voltage balancing in H-bridge cascaded multilevel STATCOM at zero current operating mode," in the 17th European Conference on Power Electronics and Applications, Geneva, Sept. 2015.

**Zezhou Yang** was born in 1990. He received the B.Eng. degree in Electrical Engineering and Automation from Wuhan University, Wuhan, China, in 2013. He is currently working toward the Ph.D. degree at Wuhan University, Hubei, China. His current research interests include multilevel converters,

multi-carrier modulation techniques, and power quality analysis and control.

Jianjun Sun was born in 1975. He received the B.Eng. degree from Wuhan University of Hydraulic and Electrical Engineering, Wuhan, China, in 1997, and then he received the M.Eng. and Ph.D. degrees from Wuhan University, Wuhan, China, in 2000 and 2007, respectively. He is now working

in the School of electrical engineering of Wuhan University as an associate professor and the deputy director of Motor and Power Electronics Center. He is also an associate director of Wuhan power supply society. His current research interests include modeling and analysis of highpower power-electronic system, operation and control of microgrid, and power quality analysis and compensation.

Shangsheng Li received the B.Eng., M.Eng., and Ph.D. degrees in electrical engineering from Wuhan University, Wuhan, China, in 2004, 2006, and 2016, respectively. His research interests include high-power converters such as static synchronous compensators, active power filters and high-power experi-

mental source techniques.

**Zhiqiang Liao** was born in 1996, Hubei Province, China. Since 2014, he has been an undergraduate student in the School of Electrical Engineering, Wuhan University, Wuhan, China, majoring in Electrical Engineering and Automation. His current research interests include power electronic

converters, semiconductors for power electronics, and renewable energy.

Xiaoming Zha was born in Huaining, Anhui Province, China, in 1967. He received B.S., M.S., and Ph.D. degrees in electrical engineering from Wuhan University, Wuhan, China, in 1989, 1992, and 2001. He was a postdoctoral fellow in University of Alberta, Canada from 2001 to 2003. He has been a

faculty member of Wuhan University since 1992, and became a professor in 2003. He is now deputy dean in the school of electrical engineering from Wuhan University, Wuhan, China. His research interests include power electronic converter, the application of power electronics in smart grid and renewable energy generation, the analysis and control of microgrid, the analysis and control of power quality, and frequency control of high-voltage high-power electric motors.