https://doi.org/10.7236/JIIBC.2017.17.5.193

JIIBC 2017-5-27

# 의료용 센서 네트워크를 위한 저전력 델타 시그마 디지털 주파수 합성기 설계

## A Low-Power Design of Delta-Sigma Based Digital Frequency Synthesizer for Bio Sensor Networks

배정남\*, 김진영\*\*

Jung-Nam Bae\*, Jin-Young Kim\*\*

요 약 본 논문에서는 델타 시그마를 이용하여 고분해능의 주파수 튜닝 범위를 가지는 저전력 디지털 주파수 합성기를 제안한다. 의료 기기용 센서 장치는 배터리 사용 시간의 제약으로 인해 저전력, 고성능 RF (Radio Frequency) 트랜시버를 필요로 한다. 반도체 공정의 미세화로 인한 디지털 회로 설계 기법의 발전으로, 이전의 아날로그 회로 설계의 한계를 극복하고, 고성능의 집적화가 가능해 지고 있다. 따라서, 전력 소모를 줄이기 위해 디지털 회로 기반의 주파수 합성기를 설계했다. 높은 주파수 분해능을 가지기 위해 델타 시그마 변조기를 링 발진기에 적용하여, 소수부 튜닝을 구현했다. 모의실험을 통해 제안된 구조가 전력 및 분해능에서 우수한 성능을 보임을 확인하였다.

**Abstract** In this paper, we present a low-power delta-sigma based digital frequency synthesizer with high frequency resolution for bio sensor networks. Biomedical radio-frequency (RF) transceivers require miniaturized forms with a long battery life and low power consumption. For the technology scaling, digital circuits have become preferable compared to analog circuits because of the aggressive cost, size, flexibility, and repeatability. Therefore, the digital circuits based on standard-cell library are used to reduce a power consumption. Additionally, a delta-sigma is used for making fractional frequency tuning range. From the simulation, we confirmed that proposed scheme has good performance in accordance with power and frequency resolution.

Key Words: Digital Frequency Synthesizer, Delta-Sigma, Ring Oscillator, Low-Power, Bio Sensor

#### 1. 서 론

의료 기기용 RF (Radio Frequnecy) 트랜시버는 긴 배 터리 사용 시간과 저전력 소비를 갖는 소형화된 형태를 필요로 한다. 402~405MHz 범위을 갖는 MICS (Medical Implant Communication Service) 주파수 대역은 체내 전 파 환경에서 우수한 신호 품질을 통해 적절한 크기와 전력 소비를 가지고, 같은 대역 내에 있는 다른 무선 주파수에 간섭이 적기 때문에, 의료 기기용 RF 트랜시버에서 널리 사용되고 있다 [1].

현재 배터리 수명에 대한 제한으로 인해, 의료 기기용 RF 트랜시버는 기준을 만족하는 성능을 달성하는 선에

<sup>\*</sup>정회원, 오사카대학교 전자공학과

<sup>\*\*</sup>정회원, 광운대학교 전자융합공학과

접수일자: 2017년 10월 1일, 수정완료: 2017년 10월 13일 게재확정일자: 2017년 10월 13일

Received: 1 October, 2017 / Revised: 10 October, 2017 /

Accepted: 13 October, 2017(available online)

<sup>\*\*</sup>Corresponding Author: jinyoung@kw.ac.kr

Dept. of Electronic Convergence Engineering, Kwangwoon University, Korea

서 최소한의 전력을 소비하도록 최적화해야 하지만, 낮 은 전력 소비와 집적화 설계는 이식용 RF 트랜시버 설계 에서 가장 중요한 해결 과제이다.

반도체 공정 미세화의 급속한 발전을 통해, 디지털 회로 설계는 크기, 비용, 설계의 유연성 및 반복성 측면에서 많은 장점을 나타내기 때문에, 아날로그 회로 설계에 비해 각광받고 있다. 의료 기기용 무선 통신 시스템에서 요구되는 완전 통합형 트랜시버는 디지털 설계 접근 방식을 통해 달성 될 수 있다<sup>[2]</sup>.

주파수 합성기는 RF 프론트 엔드 설계에서 가장 중요한 블록 중 하나이고, 다양한 무선 통신 시스템에서 사용되고 있다. 현재도 차지 펌프 기반의 아날로그 주파수 합성기가 많이 사용되고 있지만, 디지털 기반의 주파수 합성기는 프로세스 및 온도 변화에서도 저전압의 동작 호환성을 제공하기 때문에, 아날로그 방식에 비해 훨씬 더많은 관심을 끌고 있다 [3,4]. 따라서, 디지털 주파수 합성기는 배터리로 작동하는 의료 기기 센서, 무선 통신 장치에 많은 이점을 가지고 있다. 이러한 의료 기기용 RF 트랜시버에서 요구되는 디지털 주파수 합성기는 저전력을 소비하면서 성능이 우수해야 하지만, 낮은 스퓨리어스 잡음과 고분해능을 가지는 통합형 고성능 RF 트랜시버를 설계하는 것은 매우 어려운 과제이다.

본 논문에서는 델타 시그마를 이용하여 고분해능의 주파수 튜닝 범위를 가지는 저전력 디지털 주파수 합성 기를 제안한다.

본 논문은 다음과 같이 구성된다. 제 II장에서는 제안된 디지털 주파수 합성기 시스템에 대해 소개하고, 제 III 장에서는 고분해능을 가지는 델타 시그마 기반의 링 발진기를 설명한다. 제 IV장에서는 실험을 통해 성능을 분석한다. 마지막으로 제 V장에서는 본 논문의 결론을 맺는다.

#### Ⅱ. 디지털 주파수 합성기

#### 1. 제안된 시스템 구조

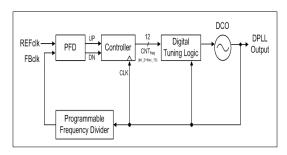

그림 1은 제안된 디지털 주파수 합성기의 구조를 나타내다. 본 구조는 PFD (Phase Frequency Detector), 컨트롤러, 디지털 제어 발진기 (Digitally Controlled Oscillator, DCO), 프로그래밍 주파수 분배기, 디지털 튜닝 로직으로 구성된다. 피드백 경로에는 주파수 분배비

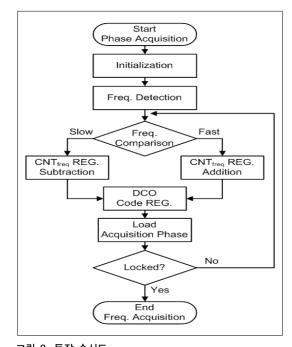

가 있어 기준 클록과 비교되는 피드백 출력 클록를 생성한다. PFD는 기준 클록과 피드백 클록의 위상차와 주파수 차이를 감지한다. 컨트롤러는 감지된 UP 및 DN 펄스를 측정하여 위상 및 주파수 차이를 카운트하고, 그에 따른 디지털 제어 비트를 생성한다. 생성된 제어 비트는 디지털 튜닝 로직을 거쳐, 디지털 제어 발진기의 주파수를 조절하여, 주파수를 변환하게 된다. 그림 2는 주파수 변환의 동작 순서로를 나타낸다. 컨트롤러에서 생성도니주파수 제어 비트 (CNTfreq)를 통해, 발진 주파수를 변화시켜 주파수 합성기의 동작을 하게 된다.

그림 1. 델타 시그마 기반의 디지털 주파수 합성기 구조 Fig. 1. Architecture of delta-sigma based digital frequency synthesizer

그림 2. 동작 순서도 Fig. 2. Operation flow chart

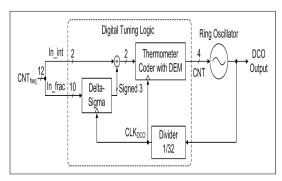

그림 3. 델타 시그마 기반의 디지털 제어 발진기 Fig. 3. Structure of delta-sigma based DCO

#### 2. 설계 고려 사항

표 1은 MICS 밴드 요구 사항을 반영한 설계 고려 사항을 나타낸다. 본 구조의 디지털 회로는 표준 셀 라이브 러리를 기반으로 구현된다. 낮은 전력 소비 및 디지털 회로의 안정적인 동작을 위해 0.7 V의 동작 전압을 사용하였다. 위상 잡음 및 주파수 분해능은 MICS 밴드 기준 허용치를 만족하는 범위에서 설정하였다.

표 1. 설계 고려 사항 Table 1. Design Considerations

| 130-nm CMOS process       |

|---------------------------|

| 0.7 V                     |

| < 1 mW                    |

| 402 ~ 405 MHz (MICS band) |

| > 3 MHz                   |

| < 30 kHz                  |

| < -100 dBc/Hz @ 200 kHz   |

| < 100 μs                  |

|                           |

### Ⅲ. 델타 시그마 기반 디지털 제어 발진기

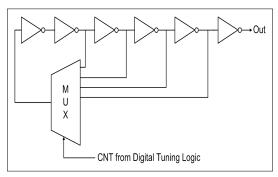

그림 3은 델타 시그마 기반의 디지털 주파수 튜닝 로 직을 이용한 디지털 제어 발진기의 구조를 나타낸다. 본 논문에서는 저전력의 설계가 용이한 인버터 기반의 링

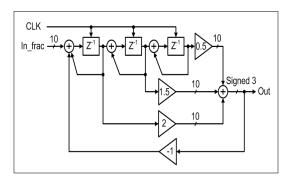

그림 4. 3차 델타 시그마 변조기 구조

Fig. 4. Structure of 3rd order delta-sigma modulator

그림 5. 링 오실레이터 구조 Fig. 5. Structure of ring oscillator

타입 발진기를 사용하였다. 제어 비트는 정수 3비트, 소 수 5비트의 총 8비트로 구성된다. 입력된 제어 비트는 동 적 요소 매칭 (Dynamic Element Matching, DEM)과 온 도계 코더 (Thermometer Coder)를 통해 8비트의 최종 제어 비트로 변환된다. 동적 요소 매칭은 구성 성분들 사 이에서 발생하는 미스 매치를 효과적으로 줄여 준다 [5]. 따라서, 소자 미스 매치로 인한 영향은 인버터 소자 선택 의 변화를 통해 제거 될 수 있다 [6]. 본 논문에서는 동적 요소 매칭으로 하드웨어 복잡도가 낮은 DWA (Data Weighted Averaging) 방법이 사용되었다. 디지털 튜닝 로직은 발진기의 출력을 32분주한 고주파 신호를 클록으 로 사용한다. 또한, 고분해능을 얻기 위해 그림 4와 같은 3차 피드 포워드 델타 시그마 변조 (Delta-Sigma Modulator, DSM)가 사용되었다 [7]. 피드포워드 구조는 작은 출력 범위를 갖기 때문에 오버플로우 문제를 해결 할 수 있다.

그림 6. 주파수 튜닝 범위 Fig. 6. Frequency tuning range

그림 5는 본 논문에서 사용된 인버터 기반의 링 발진기의 구조를 나타낸다. 인버터 기반 링 발진기는 제작이간단하고, 전력 소모가 적어 디지털 주파수 합성기에 자주 사용되는 발진기 형태이다. 발진 주파수는 인버터의 개수(n) 및 딜레이 (ta)에 의해 결정된다. (f=1/2nta) 딜레이 및 단수에 의해 결정된다. 본 설계에서는 MICS 주파수 밴드를 만족하기 위해 Ins의 딜레이를 가지는 인버터를 설계하였다. 정수 제어 비트를 통해 Coarse 주파수 튜닝을 실행하고, 그 후 델타 시그마 변조기를 통한 소수제어 비트를 통해 Fine 주파수 튜닝이 동작한다. 이를 통해, 분해능이 우수한 디지털 제어 발진기의 설계가 가능하다

#### Ⅳ. 실험 및 결과

이번 장에서는 델타 시그마 기반의 디지털 주파수 합성기의 성능을 모의실험을 통해 분석한다. 본 논문에서 제안된 시스템은 0.7 V 동작 전압에 130-nm CMOS 프로세스를 사용하여 설계되었고, 210 μW의 소비 전력을 나타낸다. 또한, 설계된 회로는 200 kHz 오프셋 주파수에서 -103 dBc/Hz의 위상 잡음을 가진다. 링 발진기는 LC 발진기에 비해 전력 소비가 월등히 낮은 대신, 위상 잡음이 높은 특성을 갖는다.

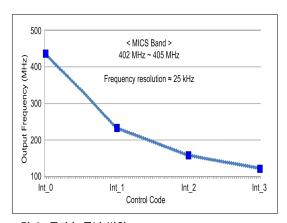

그림 6은 디지털 제어 발진기의 주파수 튜닝 범위를 나타낸다. 링 발진기는 넓은 주파수 튜닝 범위를 가진다. 컨트롤러에서 생성된 제어 코드를 통해 인버터의 수를 조절하여 주파수를 변화시키게 된다. 정수 제어 비트를

그림 7. 정착 시간 Fig. 7. Settling time

통해 넓은 주파수 대역을 커버하고, 미세 튜닝은 소수 비트를 통해 제어를 하게 된다. 설계된 디지털 제어 링 발진기는 MICS 밴드를 커버하고, 높은 주파수 분해능 특성을 보인다. 주파수 분해능은 약 25 kHz를 나타내며, MICS 밴드의 요구 사항을 만족한다.

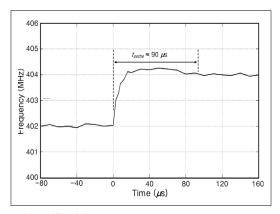

그림 7은 설계된 디지털 주파수 합성기의 정착 시간을 나타낸다. 정착 시간은 약 90 µs를 가지며, MICS 밴드 요구 사항을 만족한다. 델타 시그마 변조기를 이용하여 소수부 제어 비트를 사용함으로써 주파수의 미세 튜닝이가능하기 때문에, 빠른 주파수 정착 시간을 보이게 된다.

#### V. 결 론

본 논문에서는 델타 시그마 기반의 링 발진기를 사용하여 저전력의 분해능이 높은 디지털 주파수 합성기의 구조 및 설계에 대해 분석하였다. 반도체 공정의 미세화로 인한 디지털 회로 설계 기법의 발전으로, 이전의 아 날로그 회로 설계의 한계를 극복하고, 고성능의 집적화가 가능해 지고 있다. 전력 소모를 줄이기 위해, 디지털 회로 기반의 주파수 합성기를 제안했으며, 고분해능을 가지기 위해 링 발진기에 델타 시그마 변조기를 적용하여, 소수부 튜닝을 구현하였다. 모의실험을 통해 제안된 구조가 전력 소비가 적고 고분해능을 가짐과 동시에 MICS 밴드의 요구사항을 만족하는 것을 확인하였다.

#### References

[1] P. D. Bradley, "An ultra low power, high performance medical implant communication system (MICS) transceiver for implantable devices", in Proc. IEEE Biomed. Circuits and Syst. Conf., pp. 158 - 161, Dec. 2006.

DOI: 10.1109/BIOCAS.2006.4600332.

- [2] R. B. Staszewski and P. T. Balsara, "All-digital PLL with ultra fast settling", IEEE Trans. Circuits Syst. II, Vol. 54, No. 2, pp. 181 - 185, Feb. 2007. DOI: 10.1109/TCSII.2006.886896.

- [3] R. B. Staszewski, S. Vemulapalli, P. Vallur, J. Wallberg, and P. T. Balsara, "1.3 V 20 ps time-to-digital converter for frequency synthesis in 90-nm CMOS", IEEE Trans. Circuits Syst. II, Vol. 53, No. 3, pp. 220 224, Mar. 2006. DOI: 10.1109/TCSII.2005.858754.

- [4] J.-I. Lee and J.-S. Yoon, "A design of phase/frequency detector for PLL frequency synthesizer", The Journal of The Institute of Webcasting, Internet Television and Telecommunication, Vol. 7, No. 6, pp. 25–35, Dec. 2007.

http://www.iibc.kr/bbs/board.php?bo\_table=collect \_paper&wr\_id=1418&yy=2007.

[5] J. Wang, T. Matsuoka, and K. Taniguchi, "A switched-capacitor programmable gain amplifier using dynamic element matching", IEEJ Trans. Electrical and Electronic Engineering, Vol. 2, No. 6, pp. 600 - 607, Nov. 2007.

DOI: 10.1002/tee.20215.

[6] G. Tsuruyama, H. Ham, J. Wang, T. Matsuoka, and K. Taniguchi, "Analysis on influence of capacitor switching in digitally-controlled oscillator using behavior-level simulation", IEICE Trans. Fundamentals, Vol. J94-A, No. 2, pp. 145-148, Feb. 2011.

http://search.ieice.org/bin/summary.php?id=j94-a\_2\_145&category=A&year=2011&lang=E&abst=j.

[7] W. Rhee, B.-S. Song, and A. Ali, "A 1.1-GHz

CMOS fractional–N frequency synthesizer with a 3-b third-order  $\Sigma\Delta$  modulator", IEEE J. Solid-State Circuits, Vol. 35, No. 10, pp. 1453 - 1460, Oct. 2000.

DOI: 10.1109/4.871322.

#### 저자 소개

#### 배 정 남(정회원)

- 2009년 : 광운대학교 전파공학과 학사

- 2009년~2011년 : 광운대학교 전파공 학과 석사

- 2011년~2016년 : 오사카대학교 전자 공학과 공학박사

<주관심분야: 저전력 회로 설계, 디지 털 통신, 무선 통신>

#### 김 진 영(정회원)

- 1998년 : 서울대학교 전자공학과 공 학박사

- 2001년 : SK 텔레콤 네트웍 연구소 책임연구원

- 2009년 ~ 2010년 : 미국 M.I.T 공대 Visiting Scientist

- 2001년 ~ 현재 : 광운대학교 전자융합 공학과 교수

<주관심분야: 디지털 통신, 무선 통신, 채널부호화>