# Neutral-point Potential Balancing Method for Switched-Inductor Z-Source Three-level Inverter

### Xiaogang Wang† and Jie Zhang\*

**Abstract** – Switched-inductor (SL) Z-source three-level inverter is a novel high power topology. The SL based impedance network can boost the input dc voltage to a higher value than the single LC impedance network. However, as all the neutral-point-clamped (NPC) inverters, the SL Z-source three-level inverter has to balance the neutral-point (NP) potential too. The principle of the inverter is introduced and then the effects of NP potential unbalance are analyzed. A NP balancing method is proposed. Other than the methods for conventional NPC inverter without Z-source impedance network, the upper and lower shoot-through durations are corrected by the feedforward compensation factors. With the proposed method, the NP potential is balanced and the voltage boosting ability of the Z-source network is not affected obviously. Simulations are conducted to verify the proposed method.

**Keywords**: Switched-inductor, Z-source inverter, Voltage boosting, Neutral-point-clamped, Neutral-point potential balancing

#### 1. Introduction

Three-level neutral-point-clamped (NPC) inverters are widely used in high voltage and high power applications due to the low voltage stress of switching devices, the low output harmonics and the low operating frequency [1-3]. However, the NPC inverters can only perform voltage step down operation, so the input dc voltage must be higher than the amplitude of the output ac line voltage, which limits its application. Voltage step up can be realized by connecting dc-dc converters to the NPC converters, which increases the cost and reduces the reliability.

Z-source inverters have drawn much research interest in recent years. The difference between the Z-source inverters and the conventional inverters is the presence of an Xshaped LC impedance network, also known as Z-source impedance network, which gives voltage boosting abilities to Z-source inverters. This impedance network can also be introduced to the three-level NPC inverter, but the voltage boosting ability is limited because of the restriction between the boost factor and the modulation index [4-6]. Switched-inductor (SL) Z-source impedance network is derived by replacing the two inductors in the traditional network with two SL cells to obtain higher voltage boost factor. Several topologies based on SL Z-source impedance network are investigated in literatures [7-9]. However, the SL Z-source three-level NPC inverter has not attracted much attention from researchers. Like any other NPC inverter, the neutral-point (NP) potential of the SL Z-

Received: November 21, 2016; Accepted: February 27, 2017

source three-level inverter must be balanced. Various NP potential balancing methods were proposed for conventional NPC inverters [10-17], most of them alter redundant small vector durations so that the average neutral wire current becomes zero and thus the NP potential is balanced. In [18], a space vector modulated NP potential balancing method is proposed for Z-source three-level T-type inverter. However, it is not suitable for the SL Z-source three-level inverter.

In this paper, interest is focused on the NP potential balancing method for SL Z-source three-level inverter. Section 2 introduces the inverter topology, its voltage boosting ability and its pulse-width modulation method. Section 3 analyzes the effects of NP potential unbalance on dc-link voltage and output voltages. Section 4 describes a novel NP potential balancing method by correction of shoot-through durations. The performance of the method is evaluated through simulation, and the results are shown in Section 5.

### 2. Principle of Switched-inductor Z-Source Three-level Inverter

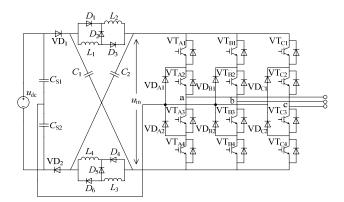

Fig. 1 shows the topology of a switched-inductor Z-source three-level NPC inverter with a Z-source impedance network connected between the two split capacitors ( $C_{\rm S1}$  and  $C_{\rm S2}$ ) and the dc-link for voltage boosting. The Z-source network consists of two capacitors ( $C_{\rm 1}$  and  $C_{\rm 2}$ ) and two SL cells, each of which is composed of two inductors and three diodes. Assuming circuit symmetry, the voltages of the four inductors are considered as being equal ( $u_{\rm L1}=u_{\rm L2}=u_{\rm L3}=u_{\rm L4}=u_{\rm L}$ ), as well as the voltages of the two capacitors ( $u_{\rm C1}=u_{\rm C2}=u_{\rm C}$ ).

<sup>†</sup> Corresponding Author: School of Mechanical and Electrical Engineering, Guangzhou University, China. (wxg@gzhu.edu.cn)

School of Mechanical and Electrical Engineering, Guangzhou University, China. (jzhang@gzhu.edu.cn)

**Fig. 1.** Topology of a switched-inductor Z-source three-level inverter

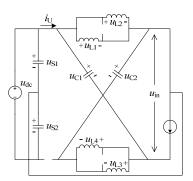

(a) Upper shoot-through state

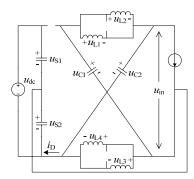

(b) Lower shoot-through state

Fig. 2. Equivalent circuits of the half shoot-through states

Voltage boosting within the Z-source three-level inverter is achieved by introducing half shoot-through states, which include upper shoot-through state and lower shoot-through state, to its modulation state sequence.

Fig. 2(a) shows the equivalent circuit in upper shoot-through state. Comparing with Fig. 1, we know that for phase a, switches  $VT_{A1}$ ,  $VT_{A2}$  and  $VT_{A3}$  conduct, as well as diode  $VD_{A2}$ . In the Z-source impedance network, diodes  $VD_1$ ,  $D_1$ ,  $D_3$ ,  $D_4$ ,  $D_6$  conduct, while  $D_2$  and  $D_5$  block. Current  $i_U$  flows to the Z-source network. Fig. 2(b) shows the equivalent circuit in lower shoot-through state. For phase a, switches  $VT_{A2}$ ,  $VT_{A3}$ ,  $VT_{A4}$  and diode  $VD_{A1}$  conduct. In the impedance network, diodes  $VD_2$ ,  $D_1$ ,  $D_3$ ,  $D_4$ ,  $D_6$  conduct, while  $D_2$  and  $D_5$  block. Current  $i_D$  flows from the

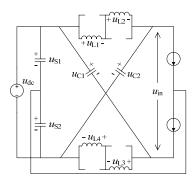

Fig. 3. Equivalent circuits of the non-shoot-through state

Z-source network. The voltage equations in both states are

$$\begin{cases}

u_{L} = u_{dc} / 2 \\

u_{inH} = u_{C} - u_{L}

\end{cases}$$

(1)

where  $u_{\rm inH}$  is the dc link high peak voltage, and  $u_{\rm dc}$  is the dc supply voltage. The upper shoot-through and the lower shoot-through have equal durations.

Fig. 3 shows the equivalent circuit in non-shoot-through state. In this case, diodes  $VD_1$ ,  $VD_2$ ,  $D_2$  and  $D_5$  conduct, while diodes  $D_1$ ,  $D_3$ ,  $D_4$  and  $D_6$  block. The voltage equations are

$$\begin{cases}

2u_{L} + u_{C} = u_{dc} \\

u_{inH} = u_{C} - 2u_{L}

\end{cases}$$

(2)

Because the inductor voltage-second balance in steady state, the capacitor voltage is derived from (1) and (2) as

$$u_{\rm C} = \frac{u_{\rm dc}}{1 - 2d_{\rm c}} \tag{3}$$

where  $d_s$  is the duty cycle of the upper shoot-through as well as the lower shoot-though.

From (2) and (3), the dc link high peak voltage is deduced as

$$u_{\text{inH}} = 2u_{\text{C}} - u_{\text{dc}} = \frac{1 + 2d_{\text{s}}}{1 - 2d_{\text{s}}} u_{\text{dc}} = Bu_{\text{dc}}$$

(4)

where *B* is known as boost factor.

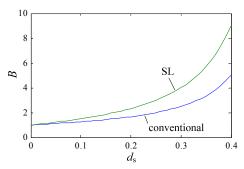

Fig. 4 plots relationships between the shoot-through duty cycle and the boost factor for the conventional Z-source three-level inverter and the SL Z-source three-level inverter. As shown in the figure, the boost factor of the SL type inverter is much higher than that of the conventional inverter.

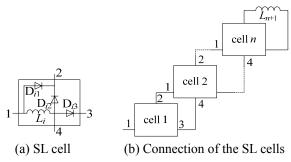

The SL cells can be cascaded to further increase the boost factor. Now a SL cell consists of one inductor  $L_i$  and three diodes  $D_{i1}$ ,  $D_{i2}$  and  $D_{i3}$  for the *i*th cell, as shown in Fig. 5(a). The SL cells are connected as in Fig. 5(b) for the upper bus. Note that inductor  $L_{n+1}$  is not included in the SL cells. For the lower bus, the SL cells are numbered from n+2 to 2n+2.

Fig. 4. Comparison of voltage boosting ability of the SL topology and the conventional topology

Fig. 5. Multicell SL

**Fig. 6.** Division of sector  $S_1$

Similarly, the dc-link high peak voltage is deduced as

$$u_{\rm inH} = \frac{1 + 2nd_{\rm s}}{1 - 2d_{\rm s}} u_{\rm dc} = Bu_{\rm dc}$$

(5)

The boost factor increases with total SL cells number 2n. However, n cannot be too large because the voltage stress of capacitors  $C_1$  and  $C_2$  will be too high.

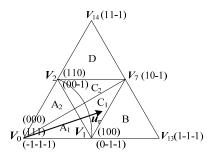

SL and multicell SL Z-source three-level inverters use same space vector pulse width modulation (SVPWM) method derived from the modulation method for traditional three-level NPC inverter. Fig. 6 illustrates the division of sector S<sub>1</sub>, which is divided into five triangles. The reference vector  $u_r$  is synthesized by its nearest three vectors. For example, if  $\mathbf{u_r}$  is located inside triangle  $C_1$  in a certain switching period, it can be synthesized by vectors  $V_1$ ,  $V_2$  and  $V_7$ .

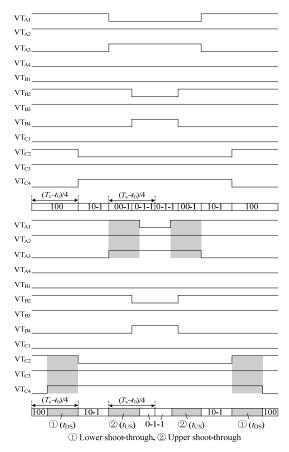

Fig. 7 shows the PWM state sequences in triangle  $C_1$  of a conventional three-level inverter and a Z-source three-

Fig. 7. Modulation of conventional and SL Z-source NPC inverters

level inverter, where two equal-interval shoot-through states (marked as ① and ② in the figure) are inserted at the two state transitions of  $\{100\} \rightarrow \{10-1\} \rightarrow \{0-1-1\}$  in the first half switching period, and the two half periods are symmetrical. The duration of  $\{10-1\}$  is  $t_0$ , so the time remaining in a switching period is  $T_s-t_0$ . The lower shootthrough state can be inserted during the {100} interval of conventional three-level inverter, while the upper shootthrough state can be inserted during the {00-1} interval and the  $\{0-1-1\}$  interval of the traditional three-level inverter to achieve as much duration time for shootthrough as possible. In half a switching period, the {100} interval is set equal to the sum of the {00-1} interval and the  $\{0-1-1\}$  interval, that is  $(T_s-t_0)/4$ . Thus, the durations available for insertion of the lower shoot-through vector and the upper shoot-through vector are identical.

### 3. Effects of Neutral-point Potential Unbalance

The voltages of the split capacitors are  $u_{S1}$  and  $u_{S2}$ respectively. In the case of unbalance, the two voltages are  $u_{\rm S1} = u_{\rm dc} / 2 + \Delta U$  and  $u_{\rm S2} = u_{\rm dc} / 2 - \Delta U$ , where  $\Delta U$  is the voltage deviation from  $u_{dc}/2$ . The KVL equations in unbalanced condition are rewritten as follows:

1) Upper shoot-through:

$$\begin{cases} u_{\rm L} = u_{\rm dc} / 2 + \Delta U \\ u_{\rm inL1} = u_{\rm C} - u_{\rm L} = u_{\rm C} - u_{\rm dc} / 2 - \Delta U \end{cases}$$

(6)

2) Lower shoot-through:

$$\begin{cases} u_{L} = u_{dc} / 2 - \Delta U \\ u_{inL2} = u_{C} - u_{L} = u_{C} - u_{dc} / 2 + \Delta U \end{cases}$$

(7)

3) Non-shoot-through:

$$\begin{cases} (n+1)u_{L} + u_{C} = u_{dc} \\ u_{inH} = u_{C} - (n+1)u_{L} \end{cases}$$

(8)

The average voltage of the inductors should be zero over one switching period, thus from  $(6)\sim(8)$ , the voltage of the Z-source network capacitor is deduced as

$$u_{\rm C} = \frac{1 + (n - 1)d_{\rm S}}{1 - 2d_{\rm S}} u_{\rm dc} \tag{9}$$

The output phase to neutral-point voltages of the inverter can be expressed as

$$\begin{cases} U_{\text{io+}} = u_{\text{dc}} / 2 + \Delta U - (n+1)u_{\text{L}} = u_{\text{inH}} / 2 + \Delta U \\ U_{\text{io-}} = u_{\text{dc}} / 2 - \Delta U - (n+1)u_{\text{L}} = u_{\text{inH}} / 2 - \Delta U \end{cases} i = a, b, c \quad (10)$$

which indicate that the NP potential unbalance causes the phase to neutral-point offset voltages to occur. The dc-link high peak voltage increases with the voltage boost factor, while the offset becomes less obvious.

## 4. Neutral-point Potential Balancing Method Based on Correction of Shoot-through Durations

### 4.1 NP potential balancing method for SL Z-source three-level inverter

The NP potential balancing method for conventional three-level NPC inverter is reviewed briefly at first. The method utilizes the redundancy of the small vectors. The positive and negative small vectors come in pairs in a switching period. As an example, the redundant vector of  $\{100\}$  is  $\{0-1-1\}$ , as shown in Fig. 6. The durations of the positive and negative small vectors in half a switching period are  $t_p$  and  $t_n$  respectively, which are equal without considering the NP potential balancing, i.e.,  $t_p$ = $t_n$ . A balancing control factor k is introduced to correct  $t_p$  and  $t_n$ . The durations after correction would be

$$\begin{cases} t_{p}^{'} = \frac{1+k}{2}t_{p} \\ t_{n}^{'} = \frac{1-k}{2}t_{p} \end{cases}$$

(11)

In order to balance the NP potential, the total injected charge to the neutral-point is set to zero. Thus the balancing control factor is deduced as

$$k = \frac{-C_{\rm S}(u_{\rm S1} - u_{\rm S2}) - i_{\rm o1}t_1 - i_{\rm o2}t_2}{i_{\rm on}t_{\rm p}}$$

(12)

where  $i_{o1}$  and  $i_{o2}$  are the neutral currents when the other two vectors are applied,  $t_1$  and  $t_2$  are the durations of the other two vectors in half a switching period,  $i_{op}$  is the neutral current when the positive small vector is applied. The split capacitor voltages can be balanced by using (11) and (12) to correct the durations of the positive and negative small vectors

Next, the effects of shoot-through on average neutral current for SL Z-source three-level inverter are analyzed. As an example, it is still assumed that  $u_r$  is located in triangle  $C_1$ . There are two cases: low boost factor and high boost factor. Using Fig. 7 for reference, in the first case, the upper shoot-through state is inserted only within  $\{00-1\}$ . The average neutral current is expressed as

$$\overline{i_{o}} = (d_{1P} - d_{S})(i_{b} + i_{c}) + d_{7}i_{b} + (d_{2N} - d_{S})(i_{a} + i_{b}) + d_{1N}i_{a}

+ [i_{a} + i_{b} - (n+1)(i_{L1} + i_{L2})]d_{S}

+ [(n+1)(i_{L1} + i_{L2}) + i_{b} + i_{c}]d_{S}

= d_{1P}(i_{b} + i_{c}) + d_{7}i_{b} + d_{2N}(i_{a} + i_{b}) + d_{1N}i_{a}$$

(13)

where  $d_{1P}$ ,  $d_{7}$ ,  $d_{2N}$  and  $d_{1N}$  are the duty cycles of vectors {100}, {10–1}, {00–1} and {0–1–1} respectively;  $i_{L1}$  and  $i_{L2}$  are the upper and lower inductor currents respectively;  $i_a$ ,  $i_b$  and  $i_c$  are the three phase inverter output currents.

In the second case, the upper shoot-through state is inserted within both  $\{00-1\}$  and  $\{0-1-1\}$ . The average neutral current is written as

$$\overline{i_{o}} = (d_{1P} - d_{S})(i_{b} + i_{c}) + d_{7}i_{b} + (d_{1N} + d_{2N} - d_{S})i_{a}

+ [i_{a} + i_{b} - (n+1)(i_{L1} + i_{L2})]d_{2N}

+ [(n+1)(i_{L1} + i_{L2}) + i_{b} + i_{c}]d_{S}

+ [i_{a} - (n+1)(i_{L1} + i_{L2})](d_{S} - d_{2N})

= d_{1P}(i_{b} + i_{c}) + d_{7}i_{b} + d_{2N}(i_{a} + i_{b}) + d_{1N}i_{a}$$

(14)

From (13) and (14), we know that the shoot-through states do not affect the average neutral current if the upper and lower shoot-through states have equal durations in a switching period. Same conclusions can be drawn when  $u_r$  is located in other triangles. Therefore, the NP potential can be balanced if the average neutral current is adjusted to zero during the non-shoot-through intervals. It seems that the principle of the NP potential balancing for a SL Z-source three-level inverter is similar to that of a conventional three-level NPC inverter. However, as previously mentioned, the time duration available for shoot-through vector insertion is  $(T_s-t_0)/4$ , which varies with the rotation of the reference voltage vector  $u_r$  and its

minimum value equals the shoot-through duration. When  $(T_s-t_0)/4$  reaches the minimum, the durations of the positive and negative small vectors equal zero and cannot be adjusted. Consequently, the NP potential balancing method for conventional three-level NPC inverter is not applicable to the SL Z-source three-level inverter.

This paper utilizes shoot-through vectors instead of redundant small vectors to stabilize the split capacitor voltages. The designing methodology is based on the charging and discharging processes of the split capacitors during the shoot-through states. From Fig. 2, it can be seen that in upper shoot-through state, the upper split capacitor discharges and  $u_{S1}$  decreases, the lower split capacitor charges and  $u_{\rm S2}$  increases, and  $u_{\rm S1} + u_{\rm S2}$  always equals to  $u_{dc}$ . As a result,  $\Delta U$  decreases. Similarly, the lower split capacitor discharges and the upper split capacitor charges in lower shoot-through state, so  $u_{\rm S2}$ decreases and  $u_{S1}$  increases, which makes  $\Delta U$  increases. As mentioned before, without considering NP potential balancing, the upper shoot-through duration  $t_{\rm US}$  equals the lower shoot-through duration  $t_{DS}$ . But in the proposed method, they can be corrected to balance the NP potential. If  $u_{S1}>u_{S2}$ , reduce  $t_{US}$  and do not correct  $t_{DS}$ . Instead, if  $u_{\rm S1} < u_{\rm S2}$ , reduce  $t_{\rm DS}$  and do not change  $t_{\rm US}$ . Based on this idea, define feedforward compensation factors as

$$\begin{cases} k_{\rm u} = 1 + \frac{\operatorname{sgn}(\Delta U) - 1}{2} k_{\rm p} \left| \Delta U \right| \\ k_{\rm d} = 1 - \frac{\operatorname{sgn}(\Delta U) + 1}{2} k_{\rm p} \left| \Delta U \right| \end{cases}$$

(15)

where sgn(x) is the sign function, sgn(x)=1 with x>0, sgn(x)=0 with x=0 and sgn(x)=-1 with x<0,  $k_p$  is a proportional coefficient greater than zero. Therefore, from (15), we know that  $k_u \le 1$  and  $k_d \le 1$ . The value of the two feedforward compensation factors cannot be too small to guarantee the voltage boosting ability of the inverter. So amplitude limiting is used to the two factors:

$$\begin{cases} k_{\rm u} = k_{\rm umin} & \text{if } k_{\rm u} < k_{\rm umin} \\ k_{\rm d} = k_{\rm dmin} & \text{if } k_{\rm d} < k_{\rm dmin} \end{cases}$$

(16)

where  $k_{\text{umin}}$  and  $k_{\text{dmin}}$  are the minimum values of  $k_{\text{u}}$  and  $k_{\text{d}}$ respectively.

After correction, the upper and lower shoot-through durations are

$$t'_{\rm US} = k_{\rm u} t_{\rm US}, \quad \dot{t}_{\rm DS} = k_{\rm d} t_{\rm DS}$$

(17)

If  $u_{S1}$ - $u_{S2}$ =2 $\Delta U$ >0, from (15) we know that  $k_u$ =1 and  $k_{\rm d}$ =1- $k_{\rm p}$ | $\Delta U$  |<1, so  $t_{\rm US}$  <  $t_{\rm DS}$  and  $\Delta U$  decreases. On the contrary, if  $u_{S1}$ - $u_{S2}$ = $2\Delta U$ <0, we have  $k_u$ = $1-k_p$ | $\Delta U$ |<1 and  $k_{\rm d}$ =1, thus  $t_{\rm US} > t_{\rm DS}$  and therefore  $\Delta U$  increases. With the adjustment of  $k_{\rm u}$  and  $k_{\rm d}$ , the difference between the split capacitor voltages will approach zero eventually. Thus the

NP potential is balanced.

### 4.2 The effect of NP potential balancing on inverter output voltage

Due to the operation of NP potential balancing control, the durations of the upper and lower shoot-through are not equal. Set  $k_u < 1$  and  $k_d = 1$  for simplification purpose, the volt-second balance equation of any of the inductors is written as

$$\frac{(u_{dc} - u_{C})}{n+1} [1 - (1+k_{u})d_{S}] + (u_{dc}/2 + \Delta U)k_{u}d_{S} + (u_{dc}/2 - \Delta U)d_{S} = 0$$

(18)

The Z-source network capacitor voltage is deduced as

$$u_{\rm C} = \frac{\left[1 + \frac{n - 3 + (n + 1)k_{\rm u}}{2} d_{\rm S}\right] u_{\rm dc} + (1 - k_{\rm u})(n + 1)d_{\rm S}\Delta U}{1 - (1 + k_{\rm u})d_{\rm S}}$$

(19)

The dc-link high peak voltage is further derived as

$$u_{\text{inH}} = \frac{1 + \left[ n - 2 + (n+2)k_{\text{u}} \right] d_{\text{S}}}{1 - (1 + k_{\text{u}})d_{\text{S}}} u_{\text{dc}} + \frac{2(1 - k_{\text{u}})(n+1)d_{\text{S}}\Delta U}{1 - (1 + k_{\text{u}})d_{\text{S}}}$$

(20)

The second item in (20) is much smaller than the first item, therefore it can be ignored. The voltage boost factor decreases compare with the ideal operation in which the split capacitor voltages are fixed and their values are equal. Generally, the inverter operates with the help of a closedloop controller to regulate its output voltages, which can compensate the slight drop of the dc-link high peak voltage. Therefore, the impact of the proposed NP potential balancing method on inverter output voltage can be neglected.

### 5. Simulation Studies

The proposed NP potential balancing method for SL Zsource three-level inverter is verified under MATLAB/ Simulink environment. The dc side voltage is  $u_{\rm dc}$ =200V. The capacitance of the split capacitors is 2200µF. The initial voltages  $u_{S1}$  and  $u_{S2}$  are 130V and 70V respectively, so  $\Delta U$ =30V. The capacitance of the Z-source network capacitors  $C_1$  and  $C_2$  is 800 $\mu$ F. The number of the switched-inductor cells is 2n=4. The inductance of the six inductors  $(L_1, L_2, L_3)$  for upper cells and  $L_4, L_5, L_6$  for lower cells) is 1.2mH. The switching frequency  $f_s$  of the inverter is 10kHz. The boost factor B is 11.4.

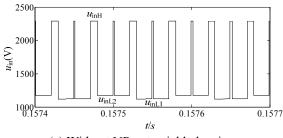

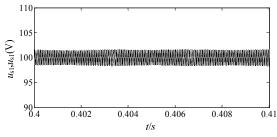

Fig. 8 shows the dc-link voltage waveforms in steady

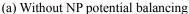

(b) With NP potential balancing

Fig. 8. Waveforms of the dc-link voltage in steady state

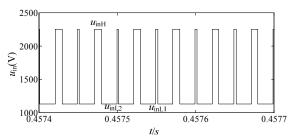

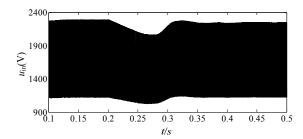

(a) Before and after the operation of NP potential balancing control

(b) Magnification after balancing

Fig. 9. Waveforms of the split capacitor voltages

and transient states. As seen from Fig. 8(a), without the operation of NP potential balancing, the dc-link high peak voltage  $u_{\rm inH}$  has the same value as in ideal case ( $u_{\rm inH}=Bu_{\rm dc}=11.4\times200=2280{\rm V}$ ), while the low peak voltage  $u_{\rm inL1}$  in upper shoot-through state is about 60V less than the low peak voltage  $u_{\rm inL2}$  in lower shoot-through state. The voltage difference equals to  $2\Delta U$ . The dc-link voltage with the operation of NP potential balancing is shown in Fig. 8(b), where the low peak voltages  $u_{\rm inL1}$  and  $u_{\rm inL2}$  are equal. The phase to neutral-point offset voltage decreases to zero.

The waveforms of split capacitor voltages are shown

Fig. 10. Waveform of the dc-link voltage in transient state

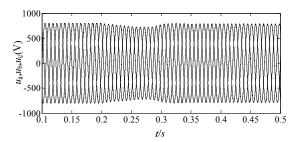

Fig. 11. Three-phase output voltages of the inverter

in Fig. 9. As seen in Fig. 9(a), the split capacitor voltages keep unbalance before 0.2s, while the proposed NP potential balancing method begins to operate at 0.2s,  $u_{\rm S1}$  deceases rapidly and  $u_{\rm S2}$  increases quickly, and they become equal from about 0.28s. The waveforms after magnification is shown in Fig. 9(b), where small ripples exist in the two voltages, but their amplitudes are less than 2V. The proposed method obtains good steady effect.

The transient state dc-link voltage is shown in Fig. 10. After 0.2s, both the high peak voltage and the low peak voltage fluctuate and recover to stable at about 0.34s. In addition, the dc-link high peak voltage is slightly smaller than it is before 0.2s due to the introduction of the feedforward compensation factors  $k_{\rm u}$  and  $k_{\rm d}$ .

The three-phase inverter output voltages are shown in Fig. 11. As the dc-link voltage, the output voltages also undergo transient processes. The voltage amplitudes become stable again at about 0.32s. Although open-loop control is adopted in the simulation, the steady state amplitudes almost keep unchanged with the proposed NP potential balancing method.

### 6. Conclusion

In this paper, a neutral-point potential balancing method for switched-inductor Z-source three-level inverter is proposed. This inverter outputs higher voltage than the Z-source three-level inverter and the three-level NPC inverter, but the conventional neutral-point potential balancing method for three-level NPC inverter is not apply to it. The upper and lower shoot-through durations are corrected by the feedforward compensation factors. With the proposed method, the NP potential is balanced

and the voltage boosting ability of the Z-source network is not affected obviously. Simulation results are provided to verify the effectiveness of the proposed method.

#### Acknowledgements

This work was supported by the "Guangdong Provincial Science and Technology Planning Project of China", no. 2015A010106015, the "Guangzhou Science and Technology Planning Project of China", no. 201607010262, and the "Innovative Academic Team Project of Guangzhou Education System", no. 1201610013.

#### References

- [1] V. Yaramasu, B. Wu, S. Alepuz and S. Kouro, "Predictive control for low-voltage ride-through enhancement of three-level-boost and NPC-converterbased PMSG wind turbine," IEEE Transactions on Industrial Electronics, vol. 61, no. 12, pp. 6832-6843, Dec. 2014.

- S. Wang, W. Song, J. Zhao and X. Feng, "Hybrid single-carrier-based pulse width modulation scheme for single-phase three-level neutral-point-clamped grid-side converters in electric railway traction," IET Power Electronics, vol. 9, no. 13, pp. 2500-2509, Sep.

- [3] M. Taoufik, H. Karima, S. Lassaad and G. Abdessattar, "Photovoltaic water pumping system with three-level NPC inverter," International Journal of Engineering Sciences, vol. 3, no. 10, pp. 99-108, Oct. 2014.

- [4] P. C. Loh, F. Gao, F. Blaabjerg and S. W. Lim, "Operational analysis and modulation control of three-level Z-source inverters with enhanced output waveform quality," IEEE Transactions on Power Electronics, vol. 24, no. 7, pp. 1767-1775, Jul. 2009.

- P. C. Loh, F. Gao, F. Blaabjerg, S. Y. C. Feng and K. N. J. Soon, "Pulsewidth-modulated Z-Source neutralpoint-clamped inverter," IEEE Transactions on Industry Application, vol. 43, no. 5, pp. 1295-1308, Sep. 2007.

- P. C. Loh, S. W. Lim, F. Gao and F. Blaabjerg, "Threelevel Z-source inverters using a single LC impedance network," IEEE Transactions on Power Electronics, vol. 22, no. 2, pp. 706-711, Mar. 2007.

- D. Li, P. C. Loh, M. Zhu, F. Gao and F. Blaabjerg, "Generalized multicell switched-inductor and switched-capacitor Z-source inverters," IEEE Transactions on Power Electronics, vol. 28, no. 2, pp. 837-848, Feb. 2013.

- M. K. Nguyen, T. V. Le, S. J. Park, Y. C. Lim and J. [8] Y. Yoo, "Class of high boost inverters based on switched-inductor structure," IET Power Electronics,

- vol. 8, no. 5, pp. 750-759, Apr. 2015.

- H. Fathi and H. Madadi, "Enhanced-boost Z-source inverters with switched Z-impedance," IEEE Transactions on Industrial Electronics, vol. 63, no. 2, pp. 691-703, Feb. 2016.

- [10] Z. Wang, F. Cui, G. Zhang, T. Shi and C. Xia, "Novel carrier-based PWM strategy with zero-sequence voltage injected for three-level NPC inverter," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 4, pp. 1442-1451, Dec. 2016.

- [11] Z. Ye, Y. Xu, X. Wu, G. Tan, X. Deng and Z. Wang, "A simplified PWM strategy for a neutral-pointclamped (NPC) three-level converter with unbalanced DC links," IEEE Transactions on Power Electronics, vol. 31, no. 4, pp. 3227-3238, Apr. 2015.

- [12] U. M. Choi and K. B. Lee, "Neutral-point voltage balancing method for three-level inverter systems with a time-offset estimation scheme," Journal of Power Electronics, vol. 13, no. 2, pp. 243-249, Mar. 2013.

- [13] C. J. Zhang, Y. Tang, D. Han, H. Zhang, X. Zhang and K. Wang, "A novel virtual space vector modulation strategy for the neutral-point potential comprehensive balance of neutral-point-clamped converters," Journal of Power Electronics, vol. 16, no. 3, pp. 946-949, May. 2016.

- [14] Z. Ye, Y. Xu, F. Li, X. Deng and Y. Zhang, "Simplified PWM strategy for neutral-point-clamped (NPC) three-level converter," Journal of Power Electronics, vol. 14, no. 3, pp. 519-530, May. 2014.

- [15] J. Lee, S. Yoo and K. Lee, "Novel discontinuous PWM method of a three-level inverter for neutralpoint voltage ripple reduction," IEEE Transactions on Industrial Electronics, vol. 63, no. 6, pp. 3344-3354, Jun. 2016.

- [16] Z. Zhang, O. Thomsen and M. Andersen, "Discontinuous PWM modulation strategy with circuitlevel decoupling concept of three-level neutral-pointclamped (NPC) inverter," IEEE Transactions on Industrial Electronics, vol. 60, no. 5, pp. 1897-1906, May. 2013.

- [17] J. Lyu, W. Hu, F. Wu, K. Yao and J. Wu, "Three-level saddle space vector pulse width modulation strategy based on two-level space vector pulse width modulation for neutral-point-clamped three-level inverters," IET Power Electronics, vol. 9, no. 5, pp. 874-882, Apr. 2016.

- [18] X. Xing, C. Zhang, A. Chen, J. He, W. Wang and C. Du, "Space-vector-modulated method for boosting and neutral voltage balancing in Z-source threelevel T-type inverter," IEEE Transactions on Industry Application, vol. 52, no. 2, pp. 1621-1631, Mar. 2016.

Xiaogang Wang He received his M.S. degree from the Institute of Electrical Engineering, the Academy of Sciences, Beijing, China, in 2003, and his Ph.D. degree from South China University of Technology, Guangzhou, China, in 2009. He was a visiting scholar at the University of South Carolina, USA,

from Feb. 2016 to Jan. 2017. He is currently an Associate Professor with the School of Mechanical and Electrical Engineering, Guangzhou University. His research interests include microgrid, renewable energy power generation systems, and high-power converters.

analysis.

Jie Zhang He received his M.S degree from South China University of Technology, Guangzhou, China, in 2006. He is currently an Experimenter with the School of Mechanical and Electrical Engineering, Guangzhou University. His research interests include power electronics and power system reliability