# Reactive Ion Etching Process Integration on Monocrystalline Silicon Solar Cell for Industrial Production

Chang Youn Yoo · Vichai Meemongkolkiat · Keunkee Hong · Jisun Kim · Eunjoo Lee · Dong Seop Kim\*

Technical Research Center, Shinsung E&G Co., Ltd., Seongnam 13543, Korea

Received October 11, 2017; Revised December 6, 2017; Accepted December 7, 2017

**ABSTRACT:** The reactive ion etching (RIE) technology which enables nano-texturatization of surface is applied on monocrystalline silicon solar cell. The additional RIE process on alkalized textured surface further improves the blue response and short circuit current. Such parameter is characterized by surface reflectance and quantum efficiency measurement. By varying the RIE process time and matching the subsequent processes, the absolute efficiency gain of 0.13% is achieved. However, the result indicates potential efficiency gain could be higher due to process integration. The critical etch process time is discussed which minimizes both front surface reflectance and etching damage, considering the challenges of required system throughput in industry.

Key words: Monocrystalline silicon, Passivation, Reactive ion etching, Reflectance, Surface texture

### 1. Introduction

Reactive ion etching (RIE) has been widely adopted in silicon PV industry for high efficiency "black silicon" product. The industry-scale RIE system has demonstrated absolute efficiency gain of more than 0.6% abs. for multicrystalline silicon solar cell<sup>1-3)</sup>. The RIE process relies on self-masking mechanism in which the plasma ions react with silicon to form polymer mask and also remove unmasked wafer surface as cyclic process. Its anisotropic etching process independent of crystal orientation is applicable to replace conventional wet texturing as well as removing grain boundaries. The role of nano-textured surface is known to improve the short circuit current by enhanced blue response of spectrum and thereby the conversion efficiency of solar cell<sup>3-5)</sup>. The same technique could apply for monocrystalline wafer with appropriate surface conditioning. However, high quality monocrystalline wafer is more sensitive to plasma etching damage than multicrystalline wafer. The relative efficiency gain against process cost needs to be measured for industrial application.

In this paper, the RIE process is applied on top of microtextured surface of monocrystalline wafer, which enables simple integration with formal mass production process. The RIE system parameters such RF power, pressure, gas ratio of

\*Corresponding author: dspv.kim@gmail.com

$SF_6/O_2/Cl_2$  were kept constant and only etch time was varied. In this way the total surface area can be monitored based on sheet resistance and deposited film thickness which are linearly correlated with etch time. We confirmed the reflectance gain becomes trivial beyond a certain etch process time. This corresponds to 150 s with etch depth limited to 500 nm for nano-texturing. Considering the throughput for industrial process, the maximum reflectance gain is found in 100 ~ 110 s. Beyond this etch time causes severe wafer edge discoloration after plasma enhanced chemical vapor deposition (PECVD) process due to chemical discontinuity at the edge.

# 2. Experiment

Industrial monocrystalline 6 inch p-type silicon with thickness of 180  $\mu$ m and resistivity of 1 ~ 3 ohm-cm is employed. The conventional aluminum back surface field (Al-BSF) manufacturing steps include alkaline texturing and phosphorous diffusion followed by PSG removal and junction isolation via inline wet process. High quality passivation is then obtained by growing thin thermal oxide layer and depositing SiN<sub>x</sub> layer with PECVD process. The front and rear contacts are screen printed with silver and aluminum paste and co-fired at peak temperature of 850°C. The additional RIE process is implemented prior to diffusion process, and subsequent surface cleaning is performed to remove the residual of RIE byproduct such as fluoride

© 2017 by Korea Photovoltaic Society

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License

<sup>(</sup>http://creativecommons.org/licenses/by-nc/3.0)

which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

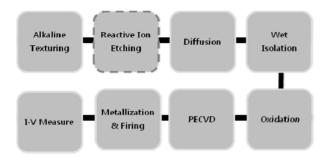

Fig. 1. RIE cell fabrication flow chart

powder. The simplified process flow diagram for Al-BSF cell fabrication with RIE is described in Fig. 1.

Emitter sheet resistance and implied  $V_{oc}$  are measured for both RIE cell and our baseline. The doping profile is also checked by ECV for applicability of the junction depth. In order to have proper passivation and minimum reflectance, either the PECVD process time or deposition rate needs to be increased. The samples are split into having SiN<sub>x</sub> thickness (1) equivalent to the baseline, (2) 10 ~ 15 nm thinner than the baseline. As for the production throughout, thinner SiN<sub>x</sub> layer is also recommended for starting point.

#### 3. Results and Discussion

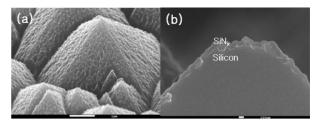

The surface morphology of our baseline and RIE processed for 100 s is characterized by SEM as shown in Fig. 2. The nanoscale RIE surface is visible on pyramid formed by alkaline texturing process while the tips are slightly rounded in (a). The SiN<sub>x</sub> film is uniformed deposited on RIE textured surface after PECVD process can be observed in (b). The valleys of pyramid have sharp transition surface and there are some chance of having voids which directly affect surface recombination. SiN<sub>x</sub> layer thickness of 80 nm or above provides better step coverage, but thinner film below 80 nm is more effective in utilizing nano-textured surface reflectivity at short wavelength. As an alternative, RF power and pressure of PECVD process can be adjusted to produce more dense films and prevent voids problems for film below 80 nm.

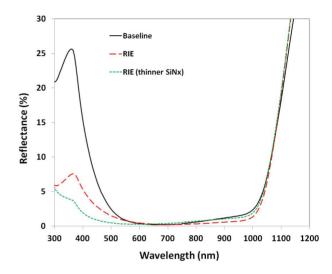

Fig. 3 shows the reflectance of all samples from 300 nm to 1200 nm after passivated with  $SiO_2/SiN_x$ , and their average weighted reflectance (AWR) measured at AM1.5 is calculated. The AWR of all RIE processed samples is below 4% as a result of improvement in both short and long wavelength, with the short wavelength improvement being the dominant one. The largest reflectance gain can be seen on the RIE sample with SiN<sub>x</sub>

Fig. 2. (a) RIE textured morphology and (b) cross-sectional view of deposited SiN<sub>x</sub> film on RIE surface

Fig. 3. Reflectance of front surface after  $SiN_x$  film deposition on both sides of wafer by PECVD

deposited  $10 \sim 15$  nm thinner than our baseline, which also appears to be more black. However, the difference in short wavelength below 550 nm gain is more dependent on the RIE process time matched with bare wafer condition and corresponding PECVD process time while the improvement in the long-wavelength above 700 nm is usually controlled by the SiN<sub>x</sub> thickness. The improvement in the long-wavelength response is expected to contribute more on passivated emitter rear contact (PERC) structure because such structure is much more efficient at long wavelength light compared to the conventional AL-BSF structure<sup>6</sup>.

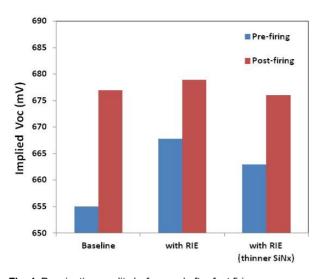

The implied  $V_{oc}$  is an important parameter for diagnosing passivation quality ahead of the metallization step. Because the surface has been enlarged, the trade-off between surface recombination and reflectance gain is addressed. The challenge is to minimize recombination by passivation processes. Fig. 4 shows the implied  $V_{oc}$  after PECVD process. To achieve symmetric passivation, the same thickness of SiN<sub>x</sub> on rear side is also deposited. For samples before fast firing, the implied  $V_{oc}$  is determined by how much SiN<sub>x</sub> film is deposited and amount of hydrogen contents in it. The actual thickness between the RIE

Fig. 4. Passivation quality before and after fast firing process as measured by QSSPC technique

|                          | Pm<br>[W] | Voc<br>[mV] | Jsc<br>[mA/<br>cm²] | Rsh<br>[ <i>Q</i> ] | Rs<br>[m <i>Q</i> ] | FF<br>[%] | Eff<br>[%] |

|--------------------------|-----------|-------------|---------------------|---------------------|---------------------|-----------|------------|

| Baseline<br>(80 nm SiNx) | 4.813     | 642.9       | 38.19               | 89                  | 4.41                | 80.2      | 19.70      |

| RIE<br>(80 nm SiNx)      | 4.845     | 641.7       | 38.46               | 23                  | 4.15                | 80.4      | 19.83      |

| RIE(<70 nm<br>SiNx)      | 4.830     | 640.3       | 38.34               | 46                  | 4.19                | 80.5      | 19.77      |

| RIE(>90 nm<br>SiNx)      | 4.772     | 643.1       | 38.01               | 62                  | 4.55                | 79.9      | 19.53      |

Table 1. I-V parameters of fabricated samples

sample and our baseline is similar, but the deposition process time of two differs by more than 50% in order to compensate for increased surface area. The longer deposition time is expected to improve the hydrogenation during the deposition which leads to higher implied  $V_{oc}$  values for RIE processed samples before firing. The firing process enables further hydrogenation from the SiN<sub>x</sub> film into emitter layer and improves surface passivation resulted in a vast improvement in implied  $V_{oc}$  after firing<sup>7</sup>). The implied  $V_{oc}$  after firing is influenced by the combination of RIE induced defect and hydrogenation of the surface.

The trend of SiN<sub>x</sub> thickness on RIE process is evident at cell level. Another set of wafers is processed with SiN<sub>x</sub> layer 10 ~ 15 nm thicker than the baseline to see if high V<sub>oc</sub> can be maintained. The cell with thicker SiN<sub>x</sub> layer indeed exhibits a higher V<sub>oc</sub> but less light can penetrate to the front surface and the generated current is reduced. Moreover, a much lower fill factor and a relatively high series resistance (Rs) suggest that the peak temperature of 850°C could not form good front contact with this thick SiN<sub>x</sub> layer (> 90 nm). In case of the thinner SiN<sub>x</sub>,

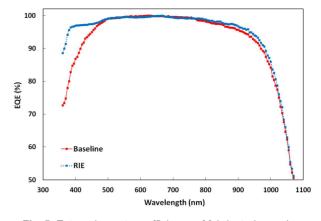

Fig. 5. External quantum efficiency of fabricated samples

surface recombination on larger surface area dominates and so the current gain becomes trivial. The implied  $V_{oc}$  indicates thick passivation could potentially help to reach efficiency higher than the one obtained with thinner passivation. However, the fast firing temperature needs to be increased to achieve punchthrough of thick SiN<sub>x</sub> layer. This would create thick Al-BSF layer and pose more challenges such as wafer bowing and nonuniform BSF quality with process integration<sup>8</sup>). The optimization strategy is to take advantage of high fill factor for thin passivation layer and deal with passivation quality on the RIE surface.

The electrical parameters of fabricated cells are listed in Table 1. The result shows average efficiency increases by 0.13%. for RIE cell passivated with SiO<sub>2</sub>/SiN<sub>x</sub> compared to our baseline cell. RIE processed cell benefits from not only increased current but also greater surface area which reduces contact resistance resulting higher fill factor. Although higher implied  $V_{oc}$  for RIE processed cells has been demonstrated with proper passivation, the actual  $V_{oc}$  after metallization is lower. This loss indicates that either the metal paste reaction or doping profile in the emitter region after fast firing process has influenced the result. The efficiency gain could be much higher if  $V_{oc}$  value is equal to the baseline cell. Similar parameter trade-off between  $V_{oc}$  and  $J_{sc}$  values is shown in a paper applying RIE to interdigitated back-contact (IBC) structure<sup>9</sup>.

Also, it was observed that all RIE processed samples tend to have lower shunt resistance (Rsh) compared to our baseline. The incomplete step coverage by SiNx film on the uneven surface previously observed by SEM may be responsible for the low shunt values.

The best efficiency sample of each process is selected and their external quantum efficiency (EQE) is measured as shown in Fig. 5. Similar to the reflectance measurement, the short wavelength region has improved significantly and increased response between 800 nm and 1000 nm wavelength also indicates excellent optical and electrical property of the fabricated solar cell despite lower  $V_{\rm oc}$  value.

# 4. Conclusion

The industry feasible RIE process for monocrystalline silicon solar cell is demonstrated with absolute efficiency gain of 0.13%. The etch time was controlled to achieve maximum gain from light trapping and the corresponding SiN<sub>x</sub> thickness was optimized with the PECVD process to account for the enlarged surface area. Various characterizations including SEM, reflectance, and implied V<sub>oc</sub> measurement were conducted to confirm the impact of RIE on each process. The non-uniform deposition of SiN<sub>x</sub> film is affected by enlarged nano-surface while the metallization contact is benefited from lower series resistance. The relatively lower V<sub>oc</sub> values for RIE processed cells can be attributed to increased surface recombination by larger surface area and changed doping profile condition. The thicker SiN<sub>x</sub> film works as supplementary to passivation quality, but thinner SiN<sub>x</sub> film results high fill factor.

### Acknowledgement

This work was supported by the Korea Institute of Energy Technology Evaluation and Planning (KETEP) and the Ministry of Trade, Industry & Energy (MOTIE) of the Republic of Korea (No. 20163010012450).

#### References

- 1. http://pv.energytrend.com/research/PERC\_and\_Black\_ Silicon\_Battle\_It\_Out\_for\_Dominance\_in\_High\_Efficiency\_ Market.html

- 2. http://pv.energytrend.com/news/GCLSI\_Achieves\_20\_6\_E fficiency\_on\_Multi\_si\_PERC\_Black\_Silicon\_Platform.html

- K.-S. Lee, M.-H. Ha, J. H. Kim, and J.-W. Jeong, "Damagefree reactive ion etch for high-efficiency large-area multi-crystalline silicon solar cells." Solar Energy Materials and Solar Cells 95.1 (2011): 66-68.

- Z. Zhao, B. Zhang, P. Li, W. Guo, and A. Liu, "Effective passivation of large area black silicon solar cells by: H Stacks." International Journal of Photoenergy 2014 (2014).

- Junghänel, M., et al. "Black multicrystalline solar modules using novel multilayer antireflection stacks." 25th European Photovoltaic Solar Energy Conference and Exhibition, 2010.

- Y. H. Chang, S. J. Su, P. S. Huang, and L. W. Cheng, "Investigation of electrical properties on industrial PERC mono-like Si solar cell," 2014 IEEE 40th Photovoltaic Specialist Conference (PVSC), Denver, CO, 2014, pp. 2960-2962. doi: 10.1109/PVSC. 2014.6925552

- 7. H. Brett, et al. "The role of hydrogenation and gettering in enhancing the efficiency of next-generation of Si solar cells: An industrial perspective." Physica status solidi (a) (2017).

- M. Vichai, et al. "Factors limiting the formation of uniform and thick aluminum-back-surface field and its potential." Journal of the Electrochemical Society 153.1 (2006): G53-G58.

- S. Hele, et al. "Black silicon solar cells with interdigitated backcontacts achieve 22.1% efficiency." Nature nanotechnology 10.7 (2015): 624-628.