# 접속 속도 향상 및 전력소모를 줄인 위성용 접속회로 연구

원주호<sup>\*</sup>. 고형호<sup>\*\*</sup>

# Research for the interface circuit to reduce static current and rising time

Joo-Ho Won\* and Hyoung-Ho Ko\*\*

요 약\_\_\_\_\_

인공위성은 다양한 제작사에서 공급하는 전장품들로 구성되는 시스템이다. 각 제작사에서는 각 제작사에서 사용하는 제작 이력 및 제작하는 위성 요구조건에 따라 다양한 내부전원을 사용하게 된다. 따라서 전장품마다 사용하는 내부전원이 다르기 때문에 전장품 사이의 접속요건에 대한 분석이 필수적이다. 접속요건에 대한 검증을 완화시키기 위해서 사용되는 회로가 Open Collector회로로, Open collector는 내부전원 차이에서 발생하는 문제를 완화시킬 수 있지만, 정전류에 의한 전력소모 증가 및 상승시간의 증가와 offset 전압 문제를 발생시킬 수 있다. 따라서 본 논문에서는 전력소모를 감소시키면서 빠른 반응시간을 얻기 위한 접속회로를 제안하고, 감소되는 전력 및 상승시간 감소를 분석한다.

Key Words: Interface circuit, Open collector, Static current, Power dissipation, High speed

ABSTRACT\_\_\_\_\_

In this paper, we present the advanced open collector circuit, interface circuit between aerospace electronics. Satellite is composed of a number of electronics, which were provided from various manufacturers. Each company manufactured its own electronics for satellite using its heritage and requirements for their electronics. Therefore each electronics may use different internal supplies. It make a problem between electronics because the supply is different from other electronics, such as the increasing of power dissipation because of the static current and the mismatch of interface voltage, the offset. Proposed circuit can reduce the static current and rising time, and also decrease the useless power dissipation caused by the static current for open collector circuit

# I. 서 론

인공위성은 구조, 추진, 열제어 등으로 구성되는 기계 부분체와 원격측정명령계, 통신계, 전력계 등 전기전자 부분체 및 자세제어 부분체로 구성되어 있다 [1]. 또한 전기전자, 자세제어 부분체의 전장품들은 다양한 제작사를 통해서 제작, 공급되어 조립 및 시험을 통해서 발사되게 된다. 각 제작사는 제작사의 제작 경험 및 제작사가 속해있는 Space Agency에서 정의한 요구조건에 적합한 설계를 하게 된다. 예를 들어 유럽의 인공위성은 50V 전압을 전력계를 위해서 사용하지만 [2], 미국의 인공위성은 28V 또는 100V의 전압을 사용한다. 1차전원뿐만 아니라 2차전원도 각 제작사마다 다르게 사용되게 된다. 유럽의 Eurostar 3000 정지궤도위성에 사용

되는 탑재컴퓨터에서는 아날로그 부품을 위한 전원을 위해서 +12.5V, -12.5V를 사용하지만 [3], 자세제어를 위한 추력기구동을 위한 접속장치에서는 아날로그 부품을 위한 전원을 +15V와 -15V를 사용한다 [4]. 이렇듯 동일한 제작사에서 제작한 전장품도 다른 전원을 사용하게 되는데, 다른 제작사에서 제작되는 전장품사이에 전원을 동일하게 하는 것은 불가능하다.

# II. Open Collector/Drain Circuit

#### 1. 전원불일치에 따른 정전류에 의한 전력소비

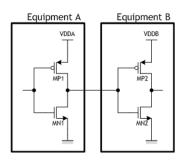

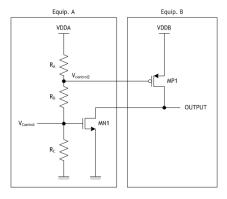

그림 1은 다른 전압을 사용하는 전장품 사이의 접속회로

접수일자 : 2016년 9월 20일, 최종게재확정일자 : 2016년 9월 30일

<sup>\*</sup> 한국항공우주연구원 위성전자팀 (jooho@kari.re.kr),

<sup>\*\*</sup>충남대학교 전자공학과 (hhko@cnu.ac.kr)

를 보여주고 있다. P-type의 MOS-FET은 source 전압과 gate 전압의 차이가 Vth 보다 큰경우에는 turn-on되고, source 전압과 gate 전압의 차이가 Vth보다 작은 경우에는 turn-off되는 특성을 갖는 3개의 입력갖는 소자이다 [5]. 따라서 그림 1의 전장품 B에 사용되는 P-type FET 소자인 MP2의 source에 해당하는 VDDB의 전원이 전장품 A의 출력을 통해서 전달되는 gate 전압에 걸리는 VDDA의 차이에 의해서 수신단 동작 특성이 결정되게 된다.

그림 1. 전장품 접속부 회로

따라서 VDDA와 VDDB가 같은 경우에는 Gate의 전압과 Source 전압이 동일하기 때문에 P-type FET가 완전하게 OFF 상태를 유지할 수 있다. 따라서 MP2과 MN2를 통해 Power Source에서 GND로 직접 흐르는 정전류가 발생하지 않는다 [6]. VDDA가 VDDB보다 큰 경우에는 문제가 발생 하지 않지만, VDDB가 VDDA보다 Vth이상 큰 경우에는 전 장품 A에서 high를 출력하게 되는 경우에도 전장품 B의 입 력은 VDDA이기 때문에 MP2가 완전하게 turn-off되지 않 고, turn-on 상태를 유지하기 때문에, 식 1과 같은 정전류가 발생해서 필요없는 전력소비가 발생한다 [5]. CMOS가 사용 되는 이유는 BIT에 비해서 동일한 transconductance인 경 우, 속도는 느리지만 BJT소자에서 발생할 수 있는 정전류를 방지해서 전력낭비를 줄일 수 있는 장점이 있기 때문인데 [7], 전원차이에 의해서 발생하는 위와 같은 정전류는 CMOS 의 느린 속도에 전력소비를 증가하는 문제를 동시에 발생시 킨다.

$$I_{static} = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2$$

(1)

일반적으로 전압이 다른 전장품 사이에서는 전압차이에 의해서 발생하는 정전류문제를 해결하기 위한 다양한 방식의 level-shifter 회로를 사용할 수 있지만, level-shifter 역시 접속 전압의 영향을 받기 때문에, 전압에 따라 다른 설계가 적용되어야 한다. 인공위성의 전장품은 어떠한 회로가 변경될 때마다, 최악설계해석 (WCA) 및 부품응력해석 (PSA) 등을 통해서 전장품 회로의 설계 안정성을 확인하고 열, 진공시험 등 다양한 시험을 통과해야만 실제 비행모델에 적용이가능하다, 하지만 전장품의 전원이 변경될 때 마다 해당 전

장품의 전원에 따라서 level shifter를 설계하고, 분석 및 시험을 매번 수행하는 것은 불가능하다 [8].

### 2. Open Collector/Drain Circuit

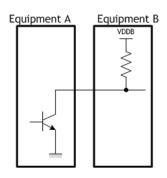

그림 2는 전원차이에 의한 문제를 방지하기 위해서 사용되는 기존의 Open collector 회로의 구조를 보여주고 있다. Open Collector 회로는 접속부의 구동회로에서 BJT나 MOS-FET를 통해서 pull-down path만을 제공하고, pull-up path는 접속부의 수신회로에서 제공하는 방식으로, 구동부에서는 수신부의 전압특성을 고려하지 않더라도 설계가 가능하기 때문에, 유연하고 간단한 설계가 가능하고 전장품의 변경에 따라서 회로의 변경도 수반하지 않는다. 그림 3은 위성에서 주로 사용되는 Open collector가 적용된 LM139 비교기의 회로를 보여주고 있다. 하지만, Open collector/drain 회로는 수신부에 사용되는 pull-up 저항값에 따라 출력이 low인 경우의 전압에 offset이 발생할 수가 있고, low인 경우에 정전류가 발생해서 전력낭비가 발생할 수가 있다.

그림 2. Open Collector 회로

식 2는 N-type FET의 on-resistance의 식을 보여주고, 식 3은 open collector 회로가 logic low인 경우에 pull-up 저항과 FET의 on-resistance에 의해 발생 가능한 offset 전압을 보여주고, 식 4는 logic low인 경우에 발생할 수 있는 최대 정전류를 보여준다. 또한 식 5는 pull-up 저항에 따른 rising time constant를 보여주고 있다. 일반적으로 Open collector/drain회로가 전압에 영향을 받지 않는 유연한 설계가 가능하지만, 식 3에 따른 offset이 커지는 경우에는 TTL 방식의 buffer를 통해서 동작하는 FPGA의 경우에는 정상적으로 high, low를 구분하는 것이 불가능해지는 문제가 발생할 수가 있다. [9].

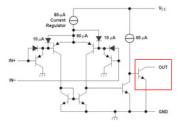

그림 3. LM139비교기 Open collector 회로

$$R_{on} \approx \frac{1}{i_D \lambda} = \frac{1}{\frac{\mu C_{ox} W}{L} (v_{gs} - V_T)}$$

(2)

$$V_{low}(Offset) = V_{cc} \times \frac{R_{on}}{R_{pull-up} + R_{on}}$$

(3)

$$I_{static} = \frac{V_{cc}}{R_{pull-up} + R_{on}} \tag{4}$$

$$t_{r(10\%-90\%)} \approx 2.2\tau \approx \frac{0.35}{f_c} = 2.2RC$$

(5)

표 1은 인공위성에서 주로 사용되는 FPGA 입출력에 적용되는 TTL 방식의 전압특성을 보여주고 있다. 따라서 일반적으로 사용되는 5V Vcc회로에서 Pull-up 저항이 4.7K를 사용하며, open collector에 사용된 BJT의 on-resistance가최대 1Kohm인 경우에 offset의 최대값은 0.88V가 된다. 0.88V는 FPGA나 RS-422 표준에서 사용되는 TTL의  $V_{\text{L-High}}$ 인 0.8V 보다 크기 때문에 정상적으로 logic low로 구분하는 것이 불가능하다. 또한  $V_{\text{CC}}$  전압이 증가하는 경우에는 TTL 전압조건을 만족시키는 것이 더 어렵기 때문에 직접적으로 TTL 로직에 접속하도록 사용할 수가 없다.

표 1. TTL 로직 전압특성

| Logic         | Voltage   |  |

|---------------|-----------|--|

| $ m V_{Low}$  | 0 ~ 0.8V  |  |

| $ m V_{High}$ | 2.5V ~ 5V |  |

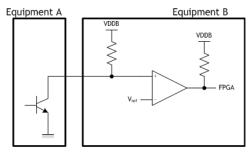

따라서 Open collector는 구동회로에서 수신단 전압특성을 고려하지 않고 설계가 가능하지만, 수신단에서는 offset에 의해서 FPGA등에 적용하기 위해서는 FPGA와 open c collector 접속회로 중간에 그림 4와 같은 비교기를 통해서 offset에 영향을 받지 않도록 하는 회로를 추가해야만 사용이 가능하다. 하지만 그림 3과 같은 비교기는 Open Collector를 내장하기 때문에 Open collector가 중복적으로 사용되는 문제가 있다.

그림 4. 비교기를 적용한 FPGA 접속용 Open collector회로

또한 Open collector의 출력이 Low인 경우에 식 4와 같은 정전류가 발생하는데, 4.7K저항과 5V Vcc를 사용하는 경우에는 최대 1.06mA가 발생할 수가 있다. 휠의 경우에는 15V

의 Vcc 및 5K 저항이 사용되므로, Open collector 1개당 3mA의 정전류가 발생한다. 정지궤도위성에 사용되는 휠의경우에는 속도정보와 방향정보를 획득하기 위해서 각 채널당 2개의 open collector회로가 사용되고, 5 채널의 휠이 사용되므로, 휠에서만 30mA의 정전류가 발생하고, 1개의 전장품당 평균적으로 10개의 비교기가 이진정보 획득 및 접속회로를 위해서 사용되게 되므로, 전장품당 10.6mA의 정전류가발생해서 전력낭비에 사용되게 된다. 식4에 따르면 pull-up저항으로 큰 저항을 사용하면 정전류에 의한 전력소비를줄일수 있지만, 식 5에 따르는 상승시간이 증가해서 접속 지연시간을 증가시키는 문제를 발생시킨다. 따라서 상승시간을줄이기 위해서 저항값을 줄이면 정전류에 의한 전력낭비가증가시키기 때문에 저항값을 무한정으로 줄이는 것은 불가능하다.

# II. Proposed Open Collector/ Drain Circuit

일반적인 Open collector 회로는 low인 경우에 지속적으로 정전류가 흐르는 문제가 있다. 그림 5는 정전류를 줄이면서 상승시간을 단축시키면서 offset voltage 문제가 발생하지 않는 Open drain 회로를 보여주고 있다.

그림 5. Proposed Open drain circuit

Open drain 회로는 pull-up 저항대신에 P-type의 MOS-FET로 변경되었고, N-type의 FET를 제어하기 위한 신호를 위한 voltage divider가 사용되었다. 입력전압이 Low인 경우에 MN1의 gate 전압은 식 6에 따르고, MP1의 gate 전압은 식 7에 의해서 결정된다. 따라서 식 6과 같이 MN1의 gate는 FPGA에 의해서 0V가 가해지고, 이것은 문턱전압보다 낮으므로 OFF를 유지하고, MP1은 VDDB보다 낮기 때문에 ON이 되므로 FET를 통해 빠른 상승시간을 갖는 구동이 가능하다.

$$V_{G.MN1} = 0 V < 0.7 V \tag{6}$$

$$V_{G,MP1} = V_{DDA} \cdot \frac{R_B}{R_A + R_B} > 0.7 V$$

(7)

하지만, 입력전압이 High인 경우에는 MN1의 gate는 FPGA에 의해서  $V_{HIGH}$ 가 가해지게 되고, 식 8과 같이 정해져서 MP1은 OFF가 되고, MN1은 ON이 되어서 출력이 Low가 될 수 있다. 따라서 offset이 없기 때문에 0V를 유지할 수가 있다.

$$V_{G,MP1} = V_{DDA} \bullet \frac{R_A}{R_A + R_B} - V_{HIGH} \bullet \frac{R_A}{R_A + R_B} < 0.7 \, V \quad (8)$$

따라서 pull-up 저항에 의해서 발생하는 정전류를 P-Type FET를 이용해서 OFF시켜서 정전류를 방지할 수가 있다. 하지만  $R_A$ ,  $R_B$ ,  $R_C$ 를 통해서 발생하는 정전류는 식 9와 같이 결정되고 문제가 될 수가 있지만, 정전류는  $R_A$ ,  $R_B$ ,  $R_C$ 의 절대적인 값에 의해서 정의되는 것이 아니라, 저항의 비율에 의해서 결정이 되기 때문에, 저항값을 큰 값을 사용하는 경우에 정전류를 줄일 수가 있다. 따라서 정전류를 없애기 위해서 MP1이 OFF될 수가 있는 전압이 될 수 있도록, 식 6, 7, 8을 이용해서 저항값을 선택한 후에, 같은 비율로 높은 저항값을 갖도록 사용할 수가 있다.

$$I_{static} = \frac{V_{DDA}}{R_A + R_B + R_C} \tag{9}$$

# Ⅳ. 시뮬레이션

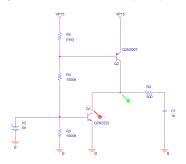

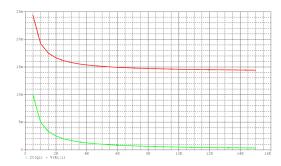

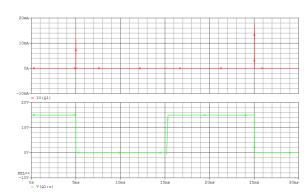

그림 6은 시뮬레이션에 사용된 Open collector회로를 보여주고 있다. Open collector회로는 저항에 의한 voltage divider에 의한 정전류 소모를 줄이기 위해서 1Mohm 저항이 사용되었다. 그림 7은 pull-up 저항을 사용하는 기존의 open drain 회로에서 pull-up 저항에 따른 offset 전압 및 정전류를 보여주고 있다. 따라서 pull-up 저항이 감소되면 붉은색 결과처럼 offset이 증가해서 TTL에 적합하지 않기 때문에 별도의 접속회로를 사용해야하고, 또한 녹색선과 같이 정전류가 증가해서 전력 소비가 증가하는 것을 확인할 수가 있다. 표 2는 기존 및 제안된 Open collector circuit에서 발생하는 정전류에 대한 시뮬레이션 결과를 보여주고 있다. 제안된 open collector 회로는 Pull-up 저항대신에 트랜지스터가 사용되므로 저항값이 존재하지 않고, 출력이 Low인 경우에 발생 가능한 정전류는 72.55nA으로 거의 없다고 볼 수가 있다.

그림 6. Proposed Open Collector circuit 회로

그림 7. 기존 Open drain circuit offset 및 정전류 시뮬레이션 결과

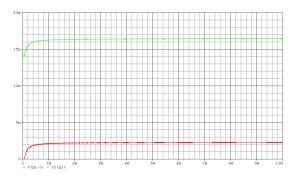

그림 8은 pull-up 저항대신 트랜지스터를 사용하는 open collector 회로의 voltage divider를 구성하는 저항값에 따른 정전류에 대한 시뮬레이션 결과를 보여주고 있다. 그림 8을 보면, 그림 6의 회로도에서 RA가 50Kohm이하인 경우에는 MP1을 통한 정전류가 0.1uA이하로 거의 없지만, 50Kohm이상이 되는 경우에는 MP1이 ON되어서 정전류가 기존의 Open collector와 유사하게 2.0mA가량이 흐르는 것을 확인할 수 가 있다. 정전류는 비슷하지만 녹색의 offset 전압을 확인하는 경우에는 어떤 저항을 사용하는 경우에도 최대 17mV로 안정적으로 low를 유지하는 것을 확인할 수가 있다. 표 3은 상승시간 및 하강시간에 대한 시뮬레이션 결과를 비교해서 보여주고 있다. 하강시간은 기존의 회로와 제안된 회로가 동일한 FET를 사용하기 때문에 거의 동일하고, 상승시간에 대해서는 Pull-up 저항에 비해서 6usec가 감소한 것을확인할 수가 있다.

표 2. 정전류에 의한 전력소비 비교

| Logic  | Pull-up 저항 | 정전류     |

|--------|------------|---------|

| 기존 회로  | 1Kohm      | 3.75mA  |

| 제안된 회로 | 없음         | 72.55nA |

표 3. 상승시간, 하강시간 비교

| Logic  | Pull-up 저항 | 상승시간      | 하강시간     |

|--------|------------|-----------|----------|

| 기존 회로  | 1Kohm      | 21.43usec | 1.53usec |

| 기존 회로  | 2Kohm      | 22.45usec | 1.55usec |

| 기존 회로  | 4Kohm      | 25.58usec | 1.76usec |

| 제안된 회로 | 없음         | 18.36usec | 1.36usec |

그림 8. MOS-FET을 이용한 제안된 Open drain 회로의 정전 류 및 offset 전압 시뮬레이션 결과

시뮬레이션에서는 15V Vcc를 사용해서 5V를 사용하는 일반적인 open collector 회로의 시뮬레이션 결과보다 정전류가 크게 나타난다. 하지만 BJT를 통한 정전류는 0.1uA이고 voltage divider에 의한 정전류는 7.3uA이다. 따라서 정전류는 worst case 7.4uA로 기존의 5V를 사용하는 open collector 1.06mA의 0.7%이고, 15V를 사용하는 회로의 정전류인 3mA의 0.24%으로 정전류에 의한 전력소비를 감소시킬 수 있다. 그림 9는 제안된 Open collector회로의 transient 시뮬레이션 결과를 보여주고 있다. High인 경우에는 VCC와동일한 15V를 유지하고, Low인 경우에도 offset이 거의 발생하지 않아서 0V에 가까운 값을 유지하는 것을 확인할 수가 있다. 또한 출력이 변하는 구간에서만 static current가 흐르고, 출력이 변하지 않는 구간에서는 static current가 흐르지 않는 CMOS 동작과 유사하게 동작해서 전력소모가 없는 것을 확인할 수가 있다.

그림 9. MOS-FET을 이용한 제안된 Open drain 회로의 정전 류 및 offset 전압 시뮬레이션 결과

# V. 결 론

Open collector회로는 다양한 제조사에 의해서 제작된 전 장품을 통해서 구성되는 인공위성에서 사용가능한 접속회로로 구동부와 수신부 각각 반대편 회로에 대해서 고려하지 않고 회로를 설계할 수 있는 유연한 설계를 제공한다. 하지만 회로의 특성에 따른 offset 전압 및 정전류에 의한 전력소모가 문제가 된다. 따라서 open collector에서 pull-up 통로를 제공하기 위해서 사용되는 수동소자인 pull-up 저항을 대신 능동소자인 PNP BJT 또는 P-type MOS-FET를 사용하고, 해당 능동소자의 switching 특성을 이용하기 위한 resistor string을 이용한 voltage divider를 통해서 정전류를 제거하고, offset없이 0V를 출력할 수 있는 회로를 제안하였다. 제안된 회로는 정전류에 의한 전력소비가 기존 회로에 비해서 1%이하로 감소하였고, 상승시간도 6usec 감소한 것을 확인할 수가 있었다. 마지막으로 offset 전압이 없기 때문에 별도의 접속회로 없이 FPGA를 구동할 수가 있다.

# 참 고 문 헌

- [1] 이동호, "인공위성시스템", 경문사, 1997

- [2] AIRBUS, Design, Interface, Environment and Test Requirement specification for Equipments, EUR3.SP.5060.MMT, 2001

- [3] AIRBUS, Eurostar 3000 Spacecraft Computer Unit (SCU) Hardware Specification, EUR3.SP.01987.MMS, 2006

- [4] AIRBUS, Eurostar 3000 Actuator Drive Electronics Specification, EUR3.SPG.00033.DP.T.ASTR, 2006

- [5] J. Rabaey, A. Chadrakasan, and B. Nikolic "Digital Integrated Circuit-A design perspective 2nd edition", Prentice Hall, 2003

- [6] J. Rabaey, M. Pedram, "Low Power Design Methodologies", Kluwer Academic Publishers, 1996

- [7] P. Gray, P. Hurst, S. Lewis, R. Meyer, "Analysis and Design of Analog Integrated Circuits", Wiley, 2009

- [8] ECSS-Q-ST-30-11C Rev 1, Space product assurance Derating for EEE components, ECSS, Oct. 2011.

- [9] H. Eren, "Electronics Portable Instruments: Design and Applications", CRC Press, 2003

#### 저자

# 원 주 호(Joo Ho Won)

# 정회원

- · 2003년 2월 : 연세대학교 전기전자공 학과 학사졸업

- · 2005년 2월 : 연세대학교 전기전자공 학과 석사졸업

- · 2007년 12월 ~ 현재: 한국항공우주 연구원

<관심분야>: 위성용회로, 위성시스템, 위성컴퓨터

#### 고 형 호(Hyoungho Ko)

- · 2003년 2월 : 서울대학교 전기공학부 학사졸업

- · 2008년 2월 : 서울대학교 전기공학부 박사졸업

- · 20010년 3월 ~ 현재 : 충남대학교 전 자공학과

<관심분야> : 아날로그 집적 회로, 센서인터페이스, MEMS