## 65 nm CMOS 공정을 이용한 W-대역 전력증폭기 설계

# Design of a W-Band Power Amplifier Using 65 nm CMOS Technology

김준성 · 권오윤 · 송 림 · 김병성

Jun-Seong Kim · Oh-yun Kwon · Reem Song · Byung-Sung Kim

요 약

본 논문에서는 차량 충돌 방지 장거리 레이더(Long Range Radar: LRR)을 위한 77 GHz 전력증폭기를 65 nm CMOS 공정을 이용하여 설계하였다. 제안한 회로는 3단 차동 전력증폭기로 공통 소스 구조와 트랜스포머를 사용했다. 측정결과로 77 GHz에서 18.7 dB의 전압 이득과 13 GHz의 3 dB 대역폭을 얻었다. 측정된 최대 출력 전력은 10.2 dBm, 입력  $P_{ldB}$ 는 -12 dBm, 출력  $P_{ldB}$ 는 5.7 dBm이며, 측정된 최대 전력 효율은 7.2 %이다. 본 전력증폭기는 1.2 V의 공급전원으로부터 140.4 mW의 DC 전력을 소모한다.

#### **Abstract**

In this paper, we propose 77 GHz power amplifier for long range automotive collision avoidance radar using 65 nm CMOS process. The proposed circuit has a 3-stage single power amplifier which includes common source structure and transformer. The measurement results show 18.7 dB maximum voltage gain at 13 GHz 3 dB bandwidth. The measured maximum output power is 10.2 dBm, input  $P_{1dB}$  is -12 dBm, output  $P_{1dB}$  is 5.7 dBm, and maximum power add efficiency is 7.2 %. The power amplifier consumes 140.4 mW DC power from 1.2 V supply voltage.

Key words: Power Amplifier, CMOS, W-Band

## T. 서 론

최근 각종 차량 사고로 인하여 발생되는 인적, 물적, 사회적 비용을 획기적으로 경감시키기 위한 지능형 차량충돌방지 안전기술에 대한 연구 및 상용화가 다양하게 진행되고 있다. 차량용 레이더 센서는 차량의 다양한 위치에 장착되어 운전자의 주행 안전성을 높이고, 각종 차량사고를 예방할 수 있다. 차량용 충돌방지 레이더를 위한 주파수 대역은 크게 24 GHz 대역과 77 GHz 대역이 주로 사용되고 있으며, 특히 77 GHz 대역은 레이더 기반의 ACC(Adaptive Cruise Control)을 위한 용도로 전 세계적으

로 사용되고 있다. 레이더 시스템 중 전력증폭기는 중요한 부분으로 우수한 성능을 얻고자 고가의 화합물 공정기술을 이용하거나, 하이브리드 형태로 제작되어 왔는데, 최근 CMOS 공정기술의 발전으로 차단 주파수와 최대 전력 이득 주파수가 100 GHz가 넘는 능동 소자들이 개발되어, 초고주파 분야에서 CMOS 공정을 이용한 레이더 시스템 설계가 활발히 이루어지고 있다<sup>[1]</sup>. 하지만 70 GHz 이상의 주파수 대역에서는 능동 소자와 수동 소자의 모델이 부정확하고, 낮은 절연 파괴 전압과 실리콘 기판의 손실로 인하여 설계에 어려움이 있다.

전력증폭기 설계는 수동소자를 사용하여 임피던스 정

<sup>「</sup>이 논문은 2015년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 연구임(No. NRF-2015R1A2A1A15056196).」 성균관대학교 정보통신대학(College of Information & Communication Engineering, Sungkvunkwan University)

<sup>·</sup> Manuscript received January 12, 2016; Revised February 22, 2016; Accepted February 26, 2016. (ID No. 20160112-003)

<sup>·</sup> Corresponding Author: Byung-Sung Kim (e-mail: bskimice@skku.edu)

합, 전력 결합, 단일 대 차동 변환을 수행하는데, 본 연구에서는 여러 가지 수동소자 중 차동회로 구조에서 DC 바이어스를 인가하기 쉽고, 전력 결합이 용이한 트랜스포머구조를 사용하였다. 본 논문에서는 65 nm 공정을 이용하여 트랜스포머를 이용한 W-Band 전력증폭기를 설계 제작하고, 측정 결과를 보여준다.

## Ⅱ. 회로 설계

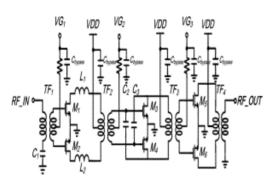

그림 1은 본 연구에서 설계한 전력증폭기의 회로도이다. 본 전력증폭기는 3단 구조로써 공통소스 구조의 차동 증폭기 단으로 구성했고, 트랜스포머를 이용하여 임피던스 정합을 했다. 임피던스 정합은 3차원 전기장 해석 툴인 HFSS를 이용하여 트랜스포머를 설계하고, 좀 더 정확한 값을 얻기 위해 연결부분까지 포함하여 시뮬레이션을 진행하였다.

차동구조 입력을 얻기 위해 입력 단에 단일 대 차동 변환(single-to differential conversion) 회로가 필요하다. 하지만 70 GHz 이상의 주파수대에서 발룬을 이용한 회로는 신호의 불균형이 일어나, 차동구조의 회로를 구현하기 어렵다. 이를 해결하고자  $C_1$  캐패시터를 추가함으로써 입력단에서 보이는 캐패시턴스의 값의 균형을 맞춰주었다<sup>[2]</sup>.

그림 1의  $M_1$ 과  $M_2$ 는 공통소스 구조이고,  $M_3$ 와  $M_4$ 는 교차 결합(cross-coupled)으로 높은 이득과 전압 이득을 얻을 수 있는 구조를 사용했다.  $M_5$ 와  $M_6$ 는 1.2 V의 낮은 공급 전압에서 캐스코드 구조보다 효율성과 선형성이 좋은 공통소스 구조를 사용하였다.

전력 증폭기를 설계함에 있어 출력 파워, 이득, 효율, 안전성 등 많은 부분을 동시에 만족해야 한다. 높은 출력

그림 1. W-band 전력증폭기 회로도

Fig. 1. Schematic of the W-band power amplifier.

을 얻기 위해서는 디바이스의 단위 폭을 키우거나, 게이트의 가지(finger)의 수를 증가시켜야 하는데, 단위 폭을 키우면 게이트 저항 성분이 증가하고, 최대 전력 이득 주파수와 이득이 낮아진다. 또한, 게이트 가지 수를 증가시키면 레이아웃이 길어져 기생성분이 증가하게 되어, 적절한 디바이스 사이즈를 결정하는 것이 중요하다<sup>[3]</sup>. 본 논문에서는 이 점들을 고려하여 시뮬레이션을 진행을 하였고, 최종단의 FET는 단일 폭  $2~\mu$ m에 총 게이트 폭  $104~\mu$ m인 소자를 사용하였다.

밀리미터파 대역에서 공통소스 구조는 드레인-게이트의 커페시턴스에 의해 피드백이 형성된다. 이는 이득 저하와 증폭기의 안정성이 낮아지는데, 이를 해결하고자 차동 증폭기 구조에서 쉽게 사용할 수 있는 중화(neutralization) 방법을 사용했다. 두 번째 단에서  $C_2$ 과  $C_3$ 를 추가함으로써 같은 위상 노드사이에 피드백을 형성한다. 이 기법은 드레인-게이트 사이의 피드백 캐페시턴스를 중화시켜 이득과 안정성을 개선한다<sup>[4]</sup>.

임피던스 정합과 전력결합용 트랜스포머는 결합상수 k 인자를 높이기 위해 두께 3  $\mu$ m인 최상위 금속층과 0.57  $\mu$ m인 차상위층을 사용한 수직 결합 구조를 사용하였다. FET에 연결되는 트랜스포머의 1차측이 더 큰 전류가 흐르기 때문에 저항 손실을 최소화하기 위해 최상위층을 1 차측으로 사용하였다. 출력단에 사용된 트랜스포머는 패드 캐패시턴스를 고려한  $50~\Omega$  부하가 최적 부하 임피던 스로 변환되도록 설계했다.

### Ⅲ. 측정 결과

그림 2는 65 nm CMOS 공정을 이용하여 제작된 칩 사

그림 2. 제작된 CMOS 전력증폭기 칩 사진 Fig. 2. Die photo of the fabricated CMOS power amplifier.

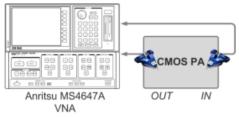

- (a) 소신호 측정 환경

- (a) Small-signal measurement setup

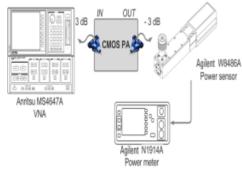

- (b) 대신호 측정 환경

- (b) Large-signal measurement setup

그림 3. 측정 환경

Fig. 3. Measurement setup.

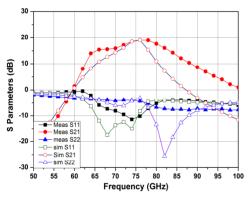

그림 4. 소신호 특성의 시뮬레이션 및 측정 결과 Fig. 4. Measured and simulated S-parameter.

진을 보여준다. 1.2~V 공급 전원으로부터 117~mA의 전류를 소모하고, 칩 면적은 패드를 포함하여  $520~\mu m \times 560~\mu m$ 이다.

본 전력증폭기의 소신호 특성은 그림 3(a)와 같이 110 GHz까지 측정 가능한 Anritsu 사의 MS4647A 벡터 네트워크 분석기를 이용하여 온칩 프로빙 방법으로 측정하였

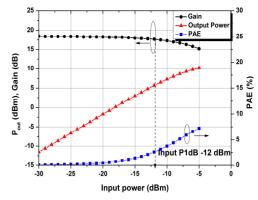

그림 5. 대신호 특성의 측정 결과

Fig. 5. Measured results of the large-signal performance.

고, 그림 4는 S-파라메터 측정 및 시뮬레이션 결과를 보여준다. 측정 결과, 77 GHz에서 18.7 dB의 전압이득과 69 GHz에서 82 GHz까지 13 GHz의 3 dB 대역폭을 얻었다.  $S_{21}$  측정결과, -40 dB 이하이고 시뮬레이션 결과와 측정결과가 약간 차이가 있지만 유사한 경향성을 보이는 것으로 볼 수 있다.

대신호 측정 환경은 그림 3(b)와 같다. 연결에 필요한 케이블, 커넥터 및 프로브에 의한 손실은 별도로 측정하여 보상했다. 그림 5는 대신호 측정 결과를 보여준다. 신호발생기의 제약으로 전력증폭기 입력 전력을 최대 -5 dBm까지 인가했고, 출력 전력은 10.2 dBm을 얻었다. 입력  $P_{IdB}$ 는 -12 dBm, 출력  $P_{IdB}$ 는 5.7dBm이며, 측정된 최대 전력 효율은 7.2 %이다.

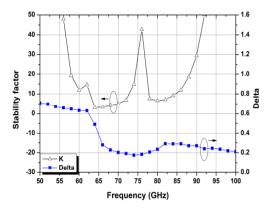

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |D|^2}{2|S_{12}S_{21}|} \tag{1}$$

$$D = S_{11}S_{22} - S_{12}S_{21} \tag{2}$$

식 (1)과 (2)를 이용하여 안정성을 계산하고, 그림 6는 안정성 측정 결과를 보여준다<sup>[10]</sup>. 측정 결과, 전 대역에서 절대 안정성(unconditional stability)을 만족하였다. 표 1에 기존의 전력증폭기의 성능과 본 논문의 전력증폭기의 성능을 비교하였다. 표에서 보는 바와 같이, 기존의 전력증폭기에 뒤지지 않는 성능을 갖는 것을 알 수 있다.

### Ⅳ. 결 론

본 논문에서는 65 nm CMOS 공정을 이용하여 77 GHz

| 丑 | 1. | 전력증폭기 | 성능 | 비교 |

|---|----|-------|----|----|

|   |    |       |    |    |

| Table 1. Performance | comparison | with | prior | arts. |

|----------------------|------------|------|-------|-------|

|----------------------|------------|------|-------|-------|

| Ref.      | Process             | Freq<br>[GHz] | Supply [V] | P <sub>dc</sub> [mW] | Power gain [dB] | P <sub>1dB</sub> [dBm] | P <sub>sat</sub><br>[dBm] | Peak<br>PAE[%] | Size [mm <sup>2</sup> ] |

|-----------|---------------------|---------------|------------|----------------------|-----------------|------------------------|---------------------------|----------------|-------------------------|

| [5]       | SiGe BiCMOS 0.12 µm | 77            | 1.8        | 297                  | 17              | 14.5                   | 17.5                      | 12.8           | 0.61                    |

| [6]       | SiGe BiCMOS 0.13 µm | 77            | 2.5        | 250                  | 25              | 9                      | 14.5                      | 9              | 0.242                   |

| [7]       | 90 nm CMOS          | 72            | 1.2        | 109                  | 11.3            | 10.3                   | 11.4                      | 11.0           | 0.28                    |

| [8]       | 90 nm CMOS          | 80            | 3          | 180                  | 18              | 10.8                   | 13.3                      | 11.8           | 0.35                    |

| [9]       | 65 nm CMOS          | 77            | 2          | 246                  | 20.9            | 13                     | 15.8                      | 15.2           | 0.375                   |

| This work | 65 nm CMOS          | 77            | 1.2        | 140.4                | 18.7            | 5.7                    | 10.2                      | 7.2            | 0.29                    |

그림 6. 안정성 측정 결과 Fig. 6. Measured stability.

전력증폭기를 설계 및 제작하였다. 측정결과, 77 GHz에서 18.7 dB의 전압 이득과 13 GHz의 3 dB 대역폭을 얻었다. 측정된 최대출력 전력은 10.2 dBm이고, 1.2 V의 공급전원으로부터 140.4 mW의 DC 전력을 소모한다.

#### References

- [1] 민경원, 손행선, "차량용 레이더 센서의 현황 및 연구 개발 동향", 전자공학회지, 40(6), pp. 28-38, 2013년 6 월.

- [2] Sofiane Aloui et al., "RF-pad, transmission lines and balun optimization for 60 GHz 65 nm CMOS power amplifier", IEEE Radio Frequency Integrated Circuits Symposium, pp. 211-214, May 2010.

- [3] Debopriyo Chowdhury et al., "Design considerations for 60 GHz transformer-coupled CMOs power amplifiers", IEEE J. Solid-State Circuits, vol. 44, no. 10, pp. 2733-

2744, Oct. 2009.

- [4] W. L. Chan, J. R. Long, M. Spirito, and J. J. Pekarik, "A 60 GHz-band 1 V 11.5 dBm power amplifier with 11% PAE in 65nm CMOS", *IEEE Solid-State Circuits Conf. Tech. Dig*, pp. 380-381, 381a, Feb. 2009.

- [5] A. Komijani and A. Hajimiri, "Wideband 77-GHz, 17.5-dBm fully integrated power amplifier in silicon", *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1749-1756, Aug. 2006.

- [6] V. Giammello, E. Ragonese, and G. Palmisano, "Transformer-coupling current-reuse SiGe HBT power amplifier for 77-GHz automotive radar", *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 6, pp. 1676-1683, Jun. 2012.

- [7] J. Lin, K. To, D. Hammock, B. Knappenberger, M. Majerus, and W. Huang, "Power amplifier for 77-GHz automotive radar in 90-nm LP CMOS technology", *IEEE Microw. Wireless Compon. Lett.*, vol. 20, no. 5, pp. 292-294, May 2010.

- [8] D. A. Chan, M. Feng, "Compact W-band CMOS power amplifier with gain boosting and short-circuited stub matching for high power and high efficiency operation", *IEEE Microw. Wireless Compon. Lett.*, vol. 21, no. 2, pp. 98-00, Feb. 2011.

- [9] Juntaek Oh, Songcheol Hong, "A 77-GHz CMOS power amplifier with a parallel power combiner based on transmission-line transformer", *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 7, pp. 2662-2669, Jul. 2013.

- [10] G. Gonzalez, Microwave Transistor Amplifiers Analysis and Design, Prentice Hall, 1997.