http://dx.doi.org/10.6113/TKPE.2016.21.6.538

# 3상 계통 연계 인버터의 SVPWM을 위한 LCL-필터 설계

서승규<sup>1</sup>. 조용수<sup>2</sup>. 이교범<sup>†</sup>

# Design of an LCL-Filter for Space Vector PWM in a Grid-Connected System

Seung Gyu Seo<sup>1</sup>, Yongsoo Cho<sup>2</sup>, Kyo-Beum Lee<sup>†</sup>

#### Abstract

This paper proposes an LCL-filter design for space vector pulse width modulation (SVM) in grid-connected three-phase inverter systems. Although there are a several studies in progress, the existing methods are erroneous because they do not focus on the other switching methods. This paper presents the design methodology for an LCL-filter that is optimized for SVM switching operations. The design procedure for the LCL-filter is presented step-by-step. The inverter-side inductor was determined by an analysis of the ripple components, mathematically. Based on the reactive power absorption ratio, the filter capacitor was determined. The grid-side inductor was determined by the ripple attenuation factor of the output current. Experimental results verify the validity of the design method for the LCL-filter.

Key words: LCL filter design, 2-level inverter, Space vector pulse width modulation (SVM)

#### 1. 서 론

최근 자원 고갈과 환경오염에 대한 관심의 증대로, 화석 연료를 대체하고 이산화탄소의 배출을 감소시키기위해 신재생 에너지 시스템의 발전이 활발히 이루어지고 있다. 이러한 신재생 에너지 시스템은 일반적으로 그림 1과 같은 계통 연계 인버터를 사용한다. 하지만 인버터를 사용하는 시스템은 필연적으로 기본과 성분과 더불어 스위칭 주파수의 정수배에 해당하는 고조파 성분을 포함한다<sup>[1]</sup>. 계통 전류의 고조파 성분은 시스템 성능을 저하시킬 뿐만 아니라 장비의 손상을 야기할 수 있다. 이러한 계통의 손상 방지를 위해 계통 전류의 고조파 성분은 통상 IEEE-519, IEEE-1547 과 같은 규정을 준수하여야 한다<sup>[2]</sup>. 이러한 규정을 만족하기 위한 다양한 방법들이 존재하지만 필터 설계에 의한 고조파 억제

Fig. 1 Grid-connected three-phase inverter system

를 일반적으로 고려한다. L-필터는 설계 방법이 간단하여 계통 연계 시스템에서 쉽게 사용할 수 있다는 장점이 있다. 하지만 시스템 용량이 증가할수록 규정을 만족시키고 성능을 유지하기 위한 필터의 용량도 커지게 되며, 결과적으로 필터의 부피와 가격의 상승을 야기한다. 또한 필터 인덕턴스의 증가로 시스템의 응답 특성이 저하되며 전압 강하 현상이 나타나게 된다. 필터의 크기가증가하는 L-필터의 단점을 보완하기 위한 방법으로 LCL-필터가 있다. 3차 저역 통과 필터와 같은 특성을 갖는 LCL-필터는 고조파 감쇄 효과가 L-필터 보다 우수하기 때문에 더 작은 용량으로도 동일한 감쇄 효과를 얻을 수 있다. 따라서 필터의 제작 비용과 부피를 줄일수 있다. 하지만 이러한 장점에도 불구하고 LCL-필터는 설계 과정이 복잡하다는 문제를 가지고 있다<sup>[3]</sup>. 이러한

Paper number: TKPE-2016-49

Print ISSN: 1229-2214 Online ISSN: 2288-6281

<sup>†</sup> Corresponding author: kyl@ajou.ac.kr, Dept. of Electrical & Computer Eng., Ajou Univ.

Tel: +82-31-219-2376 Fax: +82-31-212-9531

<sup>&</sup>lt;sup>1</sup> Dept. of Electrical & Computer Eng., Ajou Univ.

<sup>&</sup>lt;sup>2</sup> LG Electronics Gasan R&D Campus, Korea

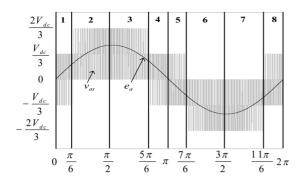

Fig. 2 Three-phase inverter output phase voltage

문제 해결을 위한 다양한 방법들이 연구되고 있지만 대부분 추가적인 LC-필터의 영향을 고려한 설계에 초점이 맞춰져 있다 $^{[A]-[5]}$ . 필터 설계 과정에 있어 추가적인 LC-필터는 LCL-필터 설계에 있어 중요한 부분이다. 하지만 LC-필터는 인버터 측 인덕턴스 $(L_1)$ 를 기준으로 설계되기 때문에 정확한 인버터 측 인덕턴스 설계가 우선된다. 또한 전류 리플 분석을 통해 인버터 측 인덕턴스 설계를 하므로 전류 리플에 영향을 주는 인버터의 스위칭 방식은 중요하게 고려되어야 한다.

본 논문에서는 공간벡터변조방식(SVM)에 최적화된 LCL-필터 설계 방법을 제안한다. 전압변조지수가 작은 구간에서는 스위칭 방법에 따른 필터 설계값에 큰 차이 가 없지만 전압변조지수가 클 경우 스위칭 방법에 따라 필터 설계값에 차이가 생기기 때문에 최적화된 설계 방 법이 필요하다. 공간벡터변조방식(SVM)은 옵셋 주입 방 식을 통해 구현한다. 인버터 측 인덕턴스( $L_1$ )는 L-필터 만 사용했을 때의 계통 전류 리플을 분석하여 설계한다. 또한 계통 측 인덕턴스( $L_2$ )는 전류 리플 감쇄율을 이용 하여 값을 얻을 수 있다. 전류 리플 감쇄율은 인버터 측 인덕턴스 $(L_1)$ 의 출력 전류 전고조파 왜율(THD)과 계통 측 인덕턴스 $(L_2)$ 의 출력 전류 전고조파 왜율(THD)의 비로 나타낼 수 있다. 필터 커패시터( $C_t$ )는 무효전력 흡 수율을 고려하여 적절하게 설계할 수 있다. 제안하는 설 계 기법은 실험을 통해 설계한 필터의 계통 측 인덕턴 스의 출력 전류 전고조파 왜율(THD)을 확인하는 것으 로 그 타당성을 검증한다.

## 2. LCL-필터 설계

#### 2.1 인버터 측 인덕턴스 $(L_1)$ 설계

인버터 측 인덕턴스 $(L_1)$ 의 설계 방법은 전류 리플률 (RF)을 통해 결정할 수 있다. 전류 리플률은 정격 전류  $(I_{rate})$ 와 리플 전류 $(I_{ripple})$ 의 비로 정의하며 설계 시 목표 THD 선정에 따라 식 (1)과 같이 표현 할 수 있다.

$$RF = \frac{I_{ripple}}{I_{rate}} \tag{1}$$

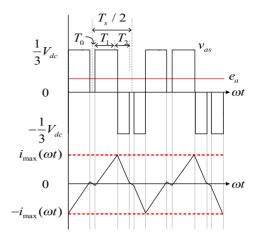

Fig. 3 Current ripple in sector 1 and 4

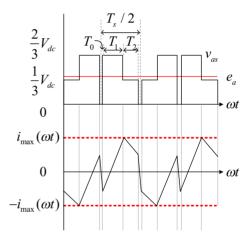

Fig. 4 Current ripple in sector 2 and 3

전류 리플은 인버터 측 인덕터에 인가되는 유효 인가 시간과 전압을 통해 그 크기를 계산할 수 있다.

극전압 지령값과 삼각 반송파의 비교를 통해 스위치 동작이 결정되기 때문에 식 (2)와 같이 정의 된다.

$$\begin{split} T_{a} &= \frac{T_{s}}{2} \left( \frac{V_{an}^{*}}{V_{dc}} + 0.5 \right) \\ T_{b} &= \frac{T_{s}}{2} \left( \frac{V_{bn}^{*}}{V_{dc}} + 0.5 \right) \\ T_{c} &= \frac{T_{s}}{2} \left( \frac{V_{cn}^{*}}{V_{c}} + 0.5 \right) \end{split} \tag{2}$$

여기서  $T_s$ 는 제어 주기,  $T_a$ ,  $T_b$ ,  $T_c$ 는 각 상 스위치의 유효 인가 시간,  $V_{an}^*$ ,  $V_{bn}^*$ ,  $V_{cn}^*$ 은 옵셋 전압이 더해진 공간 벡터변조방식(SVM)의 지령 극전압을 의미한다. 또한 이를 통해 만들어진 지령 극전압은 중앙 정렬 되었어 유효 전압 벡터가 변조 주기내 정중앙에 위치하게 된다.

인버터 측 인덕터 양단에 인가되는 전압은 인버터의 출력 상전압과 계통 상전압의 차이로 나타낼 수 있다. 이 때 인버터의 출력 상전압은 시간에 따라 변화하기

TABLE I EFFECTIVE TIME OF PHASE OUTPUT VOLTAGE

| Region | Output voltage      | Effective time |                                |

|--------|---------------------|----------------|--------------------------------|

| 1      | 0                   | $T_0$          | $T_b$                          |

|        | $1/3$ $V_{dc}$      | $T_1$          | $T_a$ – $T_b$                  |

| 2      | 2/3 V <sub>dc</sub> | $T_1$          | T <sub>a</sub> -T <sub>c</sub> |

|        | 1/3 V <sub>dc</sub> | $T_2$          | T <sub>c</sub> -T <sub>b</sub> |

때문에 인덕터 양단에 인가되는 전압도 시간에 따라 변화한다. 인가되는 전압과 유효 인가 시간의 관계는 표 1과 같이 결정된다.

출력 상전압은 그림 2와 같이 8개의 영역으로 나눌 수 있으나 대칭성을 가지기 때문에 절반인 4개의 영역 에 대한 리플 분석만으로 전체 영역에서의 전류 리플 값을 구할 수 있다. 그림 3과 4는 각 영역에서의 상전압 에 따른 전류 리플 모양을 나타낸다. 영역 1과 영역 4에 서는 그림 3에 나타난 것처럼 0이  $T_0$ 동안,  $V_{dd}/3$ 가  $T_1$ 동안.  $-V_{dc}/3$ 이  $T_2$ 동안 인가됨으로써 전류 리플값이 결 정된다. 이 영역에서는 인버터 출력 상전압의 전압 레벨 이  $V_{dc}/3$ 일 때와 0일 때 전류 리플의 최대값이 결정되 는 것을 그림 3을 통해 확인 할 수 있다. 영역 2와 영역 3 에서는 그림 4에 나타난 것처럼 0이  $T_0$ 동안,  $2V_{dd}/3$ 가  $T_1$ 동안.  $V_{dr}/3$ 이  $T_2$ 동안 인가됨으로써 전류 리플값 이 결정된다. 이 영역에서는 출력 상전압의 전압 레벨이  $2V_{dc}/3$ 일 때와  $V_{dc}/3$  일 때 전류 리플의 최대값이 결정 되는 것을 그림 4를 통해 확인할 수 있다. 전류 리플이 최대가 되는 각 영역에서의 전류 리플 최대값은 식 (3) 과 같이 나타낼 수 있으며  $\Delta i_{\max}(\omega t)$ 는 영역 1과 4,  $\Delta i_{\text{max}2}(\omega t)$ 은 영역 2와 3의 최대 전류 리플을 나타낸다.

$$\begin{split} \Delta i_{\text{max1}}(\omega t) &= \frac{1}{L} \left( \frac{V_{dc}}{3} - e_a(\omega t) \right) (T_a - T_b) - \frac{1}{L} e_a(\omega t) T_b \\ \Delta i_{\text{max2}}(\omega t) &= \frac{1}{L} \left( \frac{2 V_{dc}}{3} - e_a(\omega t) \right) (T_a - T_c) - \frac{1}{L} e_a(\omega t) T_b \end{aligned} \tag{3}$$

$$\frac{1}{2L} \left( \sqrt{(\frac{V_{dc}}{3} - e_a(\omega t))^2} + (\frac{V_{dc}}{3} - e_a(\omega t)) \right) (T_c - T_b)$$

여기서  $e_a(wt) = M_i \frac{V_{dc}}{\sqrt{3}} \sin(wt), 0 < wt < \pi$  이며 계통 상전압을 나타낸다.

전류 리플의 파형은 고주파의 삼각파 모양이기 때문에 전류 리플 RMS 값을 삼각파의 RMS 구하는 식과 동일하게 계산하면 전류 리플 RMS 값은 식 (4)와 같이나타난다.

$$I_{ripple} = \sqrt{\frac{2}{3\pi} \left[ \int_0^{\pi/6} \! \Delta i_{\rm max1}^2(\theta) d\theta + \int_{\pi/6}^{\pi/2} \! \Delta i_{\rm max2}^2(\theta) d\theta \, \right]} \eqno(4)$$

식 (4)에 정의된 전류 리플의 RMS 값을 정리하면 식 (5)와 같다.

$$I_{ripple} = \frac{1.719 \, V_{dc} \, T_s}{10^4 \, L_1} \, \sqrt{\frac{L(M_i)}{\pi^3}} \tag{5}$$

여기서  $L(M_i)$ 는 식 (6)와 같이 나타나며 식 (6)에 나타난 A와 B는 각각  $A=\sqrt{V_{dc}^2(4-6.9282M_i+3M_i^2)}$  ,  $B=\sqrt{V_{dc}^2(2-6.9282M_i+6M_i^2)}$  를 나타낸다.

$$L(M_i) = 8.15 V_{dc} M_i^4 - 23.13 V_{dc} M_i^3 + 17.56 V_{dc} M_i^2 + (0.2877 M_i^3 - 0.784 M_i^2 + 0.1995 M_i + 0.372) A - (2.214 M_i^3 - 4.136 M_i^2 + 0.738 M_i + 0.526) B$$

(6)

여기서  $M_i$ 는 전압 변조 지수를 나타내며 식 (7)과 같이 정의한다.

$$M_i = \frac{\sqrt{2} E_n}{V_{da}} \tag{7}$$

시스템의 정격 전류는 식 (8)로 정의 할 수 있다.

$$I_{rate} = \frac{M_i V_{dc}}{\sqrt{3} \sqrt{2} Z_h} = \frac{M_i V_{dc}}{2\sqrt{6} f_n L_h}$$

(8)

여기서  $f_n$ 은 계통 주파수를 의미한다. 또한  $L_b$ 는 베이스 인덕턴스를 의미하며 식 (9)와 같이 나타낼 수 있다. 이 때  $E_n$ 은 계통 선간 전압,  $P_n$ 은 정격 전력을 의미한다.

$$L_b = \frac{E_n^2}{2\pi f_n P_n} \tag{9}$$

최종적으로 식 (5)와 식 (8)을 식 (1)에 대입하여 인버터 측 인덕턴스 $(L_1)$ 을 구할 수 있으며 식 (10)과 같이 표현할 수 있다.

$$L_1 = \frac{3.43788 \sqrt{6} \ T_s f_n L_b}{RF M \cdot 10^4} \ \sqrt{\frac{L(M_i)}{\pi}}$$

(10)

#### 2.2 필터 커패시터 $(C_f)$ 설계

필터 커패시턴스( $C_f$ )는 시스템의 베이스 커패시턴스 ( $C_b$ )에 무효 전력 흡수율(x)의 곱으로 정의한다. 정격 조건에서의 베이스 커패시턴스는 식 (11)과 같고, 필터 커패시턴스는 식 (12)와 같다<sup>[6]</sup>.

$$C_b = \frac{1}{2\pi f_1 Z_b} \tag{11}$$

$$C_f = x C_b \tag{12}$$

#### 2.3 계통 측 인덕턴스 $(L_2)$ 설계

계통 측 인덕턴스 $(L_2)$ 는 인버터 측 인덕턴스 $(L_1)$ 에 전류 리플 감쇄율(r)의 곱으로 정의되며 식 (13)과 같이 표현된다 $^{[6]}$ .

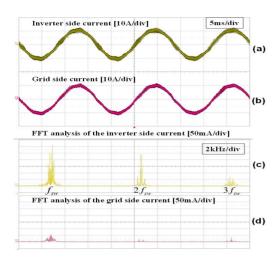

Fig. 5 Current waveform of the LCL-filter in the experiment (a) inverter-side current, (b) grid-side current, (c) FFT analysis of the inverter-side current, and (d) FFT analysis of the grid-side current

$$L_2=rL_1 \eqno(13)$$

전류 리플 감쇄율은 인버터 측 필터 인덕턴스와 계통 측 필터 인덕턴스의 비율을 나타내며 필터 전후의 전류 THD 비로도 나타낼 수 있다.

#### 3. 실 험

제안하는 설계 기법 검증을 위해 3 kW급 실험세트를 통하여 실험을 수행하였다. 실험을 위한 파라미터는 표 2에 나타나있다. 인버터 측 전류의 목표 THD를 12%로 정하였고 이에 따라 전류 리플률(RF)은 0.12로 정하고 식 (10)을 통해 1.4 mH로 설계하였다. 필터 커패시터 ( $C_f$ )는 무효 전력 흡수율을 2.67% 정도로 고려하고 식 (12)를 통해 4.4  $\mu$ F로 설계하였다. 마지막으로 계통 측 전류 THD의 목표를 2.6%로 설정하였고 식 (13)을 이용하여 계통 측 인덕턴스( $L_2$ )는 709  $\mu$ H로 설계하였다. 그림 5는 실험 결과 파형을 나타낸다. 인버터 측 전류와 계통 측 전류 비교 시 고조파 성분이 고조파 차수별 THD를 만족하고 있으며(20) 전류 THD 분석 결과 계통 측 전류 THD가 2.63%로 측정됨으로써 목표한 2.6%에 0.03% 정도의 작은 오차를 갖는 것을 확인하였다.

#### 4. 결 론

본 논문은 공간벡터변조방식(SVM)을 이용하여 계통 연계형 3상 인버터를 위한 LCL-필터 설계를 제안하였 다. 인버터 측 인덕턴스( $L_1$ )의 설계 방법은 출력 전류의 리플 분석을 통해 수식적으로 계산하였으며 계통 측 인 덕턴스( $L_2$ )는 전류 리플 감쇄율을 통해 설계하였다. 제

TABLE II SYSTEM PARAMETERS

| Parameter                       | Value              |  |

|---------------------------------|--------------------|--|

| Rated output power              | 3 kW               |  |

| Grid line-to-line voltage       | $220 V_{rms}$      |  |

| DC-link voltage                 | 400 V              |  |

| Grid frequency                  | 60 Hz              |  |

| Switching frequency             | 7.8 kHz            |  |

| Target current THD <sub>i</sub> | 12 %               |  |

| Target current THDg             | 2.6 %              |  |

| $L_{I}$                         | 1.4 mH (0.0327 pu) |  |

| $C_f$                           | 4.4 μF             |  |

| $L_2$                           | 709 μH (0.0165 pu) |  |

안하는 LCL-필터 설계 방법은 실제 전류 THD와 목표한 전류 THD의 차이를 비교하여 성능을 검증하였으며 계통 전류의 고조파 관련 기준에 부합하는 것을 확인하였다. 최종적으로 실험을 통하여 얻은 결과를 바탕으로 제안한 필터 설계 방법의 타당성을 검증하였다.

이 논문은 2016년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업임 (No. 2016R1A2B4010636)

### References

- [1] W. Wu, Y. He, T. Tang, and F. Blaabjerg, "A new design method for the passive damped LCL and LLCL filter-based single-phase grid-tied inverter," *IEEE Transactions on Industrial Electronics*, Vol. 60, No. 10, pp. 4339 4350, Oct. 2013.

- [2] 1547.1 IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources With Electric Power Systems, IEEE Std 1547.1-2005, 2005.

- [3] D. K. Choi, and K. B. Lee, "Stability improvement of distributed power generation systems with an LCL-filter using gain scheduling based on grid impedance estimations," *Journal of Power Electronics*, Vol. 11, No. 4, pp. 599–605, Jul. 2011.

- [4] K. Jalili, and S. Bernet, "Design of filters of active-front-end two-level voltage-source converters," *IEEE Transactions on Industrial Electronics*, Vol. 56, No. 5, pp. 1674-1689, May 2009.

- [5] X. Guo, X. You, X. Li, R. Hao, and D. Wang, "Design method for the LCL filters of three-phase voltage source PWM rectifiers," *Journal of Power Electronics*, Vol. 12, No. 4, pp. 559–566, Jul. 2012.

- [6] M. Liserre, F. Blaabjerg, and S. Hansen, "Design and control of an LCL-filter-based three-phase active rectifier," *IEEE Transactions on Industry Applications*, Vol. 41, No. 5, pp. 1284–1285, Sep./Oct. 2005.