# 아날로그 소자기술

# I. 서론

현대를 디지털 시대라고 부른다. 그런데 우리가 주위에서 얻는 신호 는 대부분 아날로그이기 때문에 아날로그 신호를 정확하게 처리하는 것 이 중요하게 된다. 신호 처리 관점에서는 아날로그 신호로 처리하는 것 이 곤란하기 때문에 처리의 디지털화가 되고 있다. 아날로그 신호를 손

실 없이 디지털 신호로 변 환한다든가. 아날로그 신 호로 변환하는 목적에서 아날로그 회로가 사용된

아날로그 신호를 정확하게 처리하기 위 호를 정확하게 디지털 신 해서는 회로 설계 기술 뿐만 아니라 회로 를 구성하는 소자 기술도 중요하다.

다. 그래서 정확한 아날로그 신호 처리를 위한 회로를 구현하기 위해 설계 기술도 중요하지만 회로를 구성하는 소자 기술도 중요한 역할을 하게 된다.

본 연구에서는 먼저 robust 한 아날로그 회로 설계를 위해 필요한 소 자들의 종류와 특성에 대해 알아보고자 한다. 그리고 이러한 특성을 얻 기 위해 필요한 여러 가지 공정 기술에 대해 알아 보고 이를 통해 얻은 소자 특성에 대해서도 몇 가지 예를 들어 소개하고자 한다.

# Ⅱ. 본론

실리콘 프로세스에서 사용되는 반도체 소자는 MOS 트랜지스터, 저 항기, 캐패시터, 바이폴라 트랜지스터 등이 있다. 이들 소자들이 아날 로그 회로에 사용될 때 요구되는 여러 가지 특성들에 대해 알아 보도록 하겠다. 중요한 소자 특성으로 이득(Gain), 노이즈, 선형성, 매칭 특성 등을 들 수 있는데[1] 이러한 특성들이 양호한 특성을 갖고 있어야 설계

이희승 매그나칩반도체

이정환 매그나칩반도체

에서 요구하는 사양을 만족하면서 안정된 동작을 하는 회 로를 구현할 수 있게 된다.

#### 1. 노이즈 특성

반도체 소자의 노이즈는 크게 2가지로 나눌 수 있다. 하나는 화이트 노이즈로 주파수에 상관없이 일정한 수준을 가진다. 다른 하나는 주파수에 따라 노이즈 값이 바뀌는 노이즈로 Flicker 노이즈나 Burst 노이즈가 있다<sup>[2]</sup>. 이 중에서 Flicker 노이즈와 Burst 노이즈에 대해 좀 더자세히 알아보도록 하자. Flicker 노이즈는 값이 주파수에 반비례하므로 1/f 노이즈라고도 하며 실리콘과 게이트 산화막 계면의 트랩들에 의한 전하의 trapping/de-

trapping에 의해 일어나며<sup>③</sup> 소자에서 저항 fluctuation으로 나타나게된다. 즉, 1/f 노이즈는 전압이나 전류의 fluctuation을 일으키게된다. 그리고 Burst 노이즈는 팝콘 노이즈

아날로그 반도체 소자는 크게 1/f noise와 RTS noise 두 가지의 노이즈를 갖고 있다.

또는 RTS 노이즈라고도 불리며, 스피커로 들으면 팝콘이 튀는 소리가 나는 것과 같은 잡음이 난다는 것에서 붙여진 이름이다. 이것은 주파수의 제곱에 반비례하는 양상을 보이며 1/f 노이즈와 마찬가지로 실리콘과 게이트 산화막

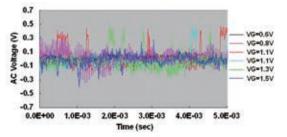

(a) Thermally nitrided gate oxide를 사용한 트랜지스터의 RTS noise 측정 결과

(b) Plasma nitrided gate oxide를 사용한 트랜지스터의 RTS noise 측정 결과 〈그림 1〉게이트 산화막 종류에 따른 RTS 노이즈 특성

계면의 트랩들에 의한 전하의 trapping/de-trapping에 의해 일어난다.

〈그림 1〉은 두 가지 게이트 산화막 공정에 대해 RTS 노이즈를 측정한 그래프를 나타낸 것인데, 시간에 따른 전압 수준 변화를 보여 준다. Thermally nitrided gate oxide를 사용하여 RTS 노이즈가 큰 (a)의 경우, 전압 fluctuation이 크게 존재하고 이것이 결국 신호 처리의 중간에 신호가 튀는 노이즈로 나타나게 된다. Plasma nitrided gate oxide를 사용한 (b)의 경우에 RTS 노이즈가 크게 감소하는 것을 볼 수 있다. 이것은 Plasma nitrided gate oxide를 사용한 경우에 interface trapped charge가 크게 감소하기 때문에 나타나는 결과이다.

반도체 트랜지스터에서 Flicker 노이즈나 팝콘 노이즈를 감소시키 기 위해 실리콘과 게이트 산화막 사 이의 계면 특성을 제어하여 트랩 밀 도를 줄이는 것이 필요하다. 실리

콘과 게이트 산화막 계면의 트랩 밀도를 줄여서 낮은 1/f 노이즈 특성을 얻기 위해 필요한 반도체 공정에 대해 알아 보고자 한다. 첫 번째로 게이트 산화막 제조 공정에서 순수한 실리콘 산화막을 형성하는 방법이다. Boron penetration을 줄이기 위해 산화막 형성 후 실리콘과 게이트 산화막 사이의 계면에 열적으로 질소를 들어가게 하는 공정은 interface tapped charge를 많이 생성시키기때문에 Flicker 노이즈 특성을 좋지 않게 만든다. 두 번째로 게이트 산화막 형성 전에 세정을 식각 속도가 느린 용액으로 사용하여 실리콘 표면 거칠기를 줄이는 방법이 있

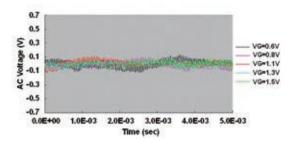

〈그림 2〉 Noise 개선 전후의 MOS 트랜지스터의 노이즈 특성 비교

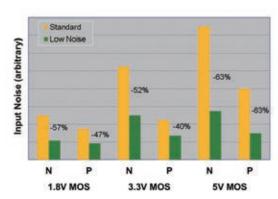

〈그림 3〉 P+ 폴리실리콘 저항기의 선폭에 따른 면저항 변화 (Length = 100um)

다. 세 번째로 실리콘과 큰 결합력을 갖는 원소를 게이트 영역에 이온 주입하여 실리콘과 이 원소의 결합을 통해 계면에서 dangling bond를 감소시키는 것이다. 이러한 방법을 통해 Flicker 노이즈가 낮은 트랜지스터를 제작하 였으며 〈그림 2〉에 노이즈를 개선하기 전과 후의 노이즈 수준을 비교하였다. 이렇게 구현된 트랜지스터는 세계에 서 가장 낮은 수준의 노이즈 값을 가진다.

#### 2. 저항기 특성

반도체 소자 중 아날로그 회로에 많이 사용되는 저항기 의 크기, 온도 및 전압에 따른 특성에 대해 알아 보자, 먼 저 많이 사용되는 저항 중의 하나인 non-silicide P+ 폴 리실리콘 저항기의 크기에 따른 면저항 값을 보면 〈그림 3〉과 같이 나타난다. 〈그림 3〉에서 볼 수 있는 것과 같이

저항의 폭이 감소함에 따라 면저항 이 증가하는 것을 알 수 있다. 이러 한 특성을 잘 고려하여 설계를 하여 야 하며, SPICE 모델에 저항기 크

기에 따른 저항 특성이 잘 반영되어 있으므로 이를 이용 하면 된다. 이와 같이 소자의 크기에 따른 특성 변화는 저 항기 뿐만 아니라 트랜지스터. 캐패시터 등 모든 소자에 서 나타나므로 이 특성을 고려한 모델 반영 및 설계가 이 루어져야 한다.

반도체 칩에서 사용된 소자들은 일정한 온도에서 작동 하는 것이 아니고 칩의 동작이나 외부 환경에 따라 칩의 내부 온도가 변하므로 어떤 온도 범위에서 작동하게 된 다. 그래서 소자들의 온도에 따른 소자 특성 변화를 측정

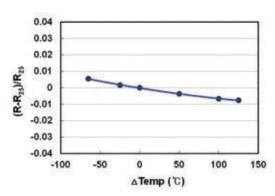

〈그림 4〉 TaN resistor의 온도 변화에 따른 저항 변화

하여 SPICE 모델에 반영하게 된다. 전압에 따른 특성 변 화도 마찬가지로 모델에 반영되어 있으며, 이런 온도나 전압에 따른 특성 변화까지 고려하여 회로 설계를 하여야 한다. 온도에 대한 특성 변화를 나타내기 위해 온도 계수 를 사용하게 되며, 저항에서의 온도 계수는 다음과 같이 정의된다[4]

$$R = R_{ref} [1 + \alpha (T - T_{ref})]$$

여기서. R = 온도 "T"에서 도체의 저항. R<sub>ref</sub> = 기준 온 도에서 도체의 저항  $(T_{ref}$ 는 보통  $25^{\circ}$ C),  $\alpha$  = 저항 온도 계 수, T = 섭씨 온도로 표시한 도체의 온도, Tref = 도체의 기준 온도

그런데 어떤 회로는 온도에 따른 저항 변화가 아주 작 은 것을 요구하므로 이에 맞는 저항을 개발하여야 한다.

> 반도체 공정에서 사용 가능하면 서 온도 계수가 낮은 물질은 TiN. TaN 등이 있으며. TaN 막을 얇은 두께로 증착하여 온도 계수가 아주

낮은 저항기를 제작하였다. 이렇게 제작된 저항기의 온 도 변화에 따른 저항 변화 특성을 〈그림 4〉에 나타내었 다. 이 저항의 온도 계수는 -80ppm/℃로 아주 낮은 값 을 보인다. 이는 보통 아날로그에 사용하는 폴리실리콘 저항기의 온도 계수의 1/3~1/10 수준이다.

### 3. 캐패시터 특성

저항기와 캐패시터는 온도 계수. 전압 계수와 매칭 계수가 중요한 파라미터이다.

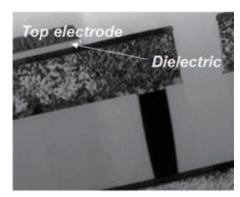

> 아날로그에 사용하는 캐패시터는 초기에는 PIP (Poly-Si Insulator Poly-Si) 캐패시터를 사용하였지만 최근에

〈그림 5〉 MIM 캐패시터의 투과전자현미경 단면 사진

는 MIM (Metal Insulator Metal) 캐패시터를 많이 사용 하고 있다. 〈그림 5〉는 MIM 캐패시터의 투과전자현미 경 단면 사진을 보여 준다. 캐패시터는 여러 가지 기본적 인 특성 뿐만 아니라 단위 면적당 캐패시턴스도 중요하 다. 왜냐하면 기술이 scaling-down됨에 따라 능동소자 뿐만 아니라 수동소자의 크기도 줄일 필요가 있다. MIM 캐패시터에서 단위 면적당 캐패시턴스 값이 4fF/um<sup>2</sup> 이 상이 되려면 기존의 실리콘 질화막을 절연막으로 사용하 는 것은 한계가 있다. 단위 면적당 캐패시턴스 값을 증가 시키기 위해 두께를 줄여야 하는데 이렇게 되면 절연막의

누설전류와 신뢰성을 만족하지 못 하게 된다. 그래서 Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, HfO,와 같은 높은 절연 상수 값을 갖는 물질을 절연막으로 사용할 필 요가 있다.

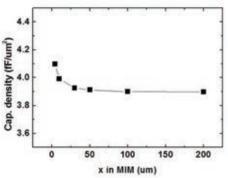

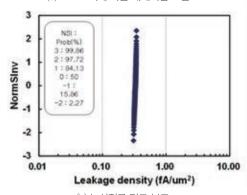

Al<sub>2</sub>O<sub>3</sub>와 HfO<sub>2</sub>를 적층 구조로 사

용하여 4. 6. 8. 10fF/um<sup>2</sup>의 캐패시터를 개발하였다. 〈그림 5〉에 4fF/um² MIM (Metal Insulator Metal) 캐 패시터의 특성을 나타내었다. 〈그림 6 (a)〉에서 캐패시터 크기에 따른 캐패시턴스 밀도 변화를 나타내며. 〈그림 6 (b)〉는 누설전류 밀도의 분포를 나타내는데 양호한 값을 갖는 것을 볼 수 있다. 이러한 기본적인 특성 외에 온도나 전압에 따른 특성을 SPICE 모델에 반영하였고 소자의 신 뢰성 테스트를 통과하여 제품에 적용하고 있다.

#### 4. 매칭 특성

아날로그에 사용하는 소자는 특성 파라미터의 절대값

(a) MIM 크기에 따른 캐패시턴스 밀도

(b) 누설전류 밀도 분포 (그림 6) 4fF/um<sup>2</sup> MIM 캐패시터의 특성

을 이용하는 경우도 있지만 파라미터 값의 상대적인 비

아날로그 반도체 소자는 특성 파라미터

의 절대값 보다는 상대적인 비율을 이용하는 경우가 많으며 이에 따라 매칭

특성이 매우 중요하다.

를 이용하는 경우가 더 많다. 즉. 많은 아날로그 회로에서 트랜지스 터, 저항기, 캐패시터 등의 파라미 터 값의 비를 이용하여 회로를 구 현하게 되며 이 비가 아주 중요한 요소가 된다. 예를 들면, 캐패시턴

스의 상대적인 크기가 1인 것과 9인 캐패시터를 설계에 사용할 때 1:9의 비가 잘 맞아야 회로 설계 및 동작에 유 리하다. 이 두 개의 캐패시터는 가까이 있지만 다른 위치 에 존재하기 때문에 기본적으로 특성 차이가 존재할 수 있다. 이러한 위치나 소자의 주위 환경에 따른 차이를 최 소화할 수 있도록 공정 변동이 적도록 조절해야 하며 소 자의 패턴 모양도 고려해야 한다.

같은 기하학적 구조와 환경을 가지면서 근접한 거리에 위치한 소자들 사이에도 공정변동 때문에 전기적 특성 차 이가 생기며 이를 local variation이라 부른다. 이러한 전 기적 특성 차이의 분포를 통계적으로 특성화한 것을 매칭

특성이라 한다. 예를 들면, 트랜지스터의 문턱 전압 (Vt) 에 대한 매칭 특성은 〈그림 7〉과 같이 측정하여 구해진 다. 여기서 A<sub>v+</sub>는 Vt의 매칭 계수(matching coefficient) 라 명명하며, 매칭 계수가 작을 수록 매칭 특성이 좋다고 하다

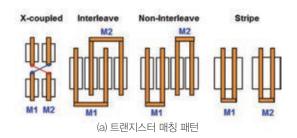

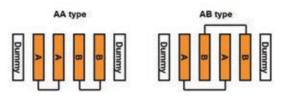

매칭 평가 패턴의 형태도 여러 가지가 있는데 〈그림 8〉 에 트랜지스터와 저항기의 대표적인 매칭 패턴을 나타내 었다. 이런 여러 가지 형태의 패턴을 평가하여 매칭 특성 을 얻게 되면 특성이 좋은 형태의 패턴을 설계에서 선택 하여 사용할 수 있다.

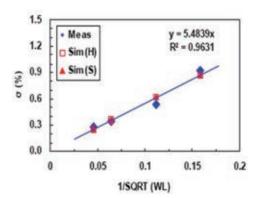

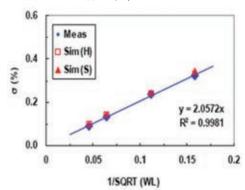

실제 웨이퍼에서 측정한 Non-silicide 폴리실리콘 저 항기의 매칭 특성을 〈그림 9〉에 나타내었다. 두 저항의 매칭 계수를 비교해 보면 P+ poly resistor가 2.06%um로 N+ poly resistor의 5.48%-um 에 비해 더 작다 는 것을 알 수 있다. 온도 계수 및 전압 계수 특성도 P+ poly resistor가 N+ poly resistor에 비해 더 양호하므로 아날로그 회로에 P+ poly resistor가 일반적으로 더 많이 사용된다.

매칭 특성이 있으면 이를 반영하여 아날로그 회로를 더 정확하게 설계할 수 있을 뿐 아니라 회로에서 필요로 하 는 정확도에 따라 필요한 소자 크기를 정할 수 있어 회로 의 면적도 줄일 수 있다. 또한 매칭 특성 그래프에서 알 수 있듯이 소자 크기가 증가하면 소자들의 mismatching 은 감소한다는 것을 알 수 있다. 트랜지스터의 경우 소자

〈그림 7〉 매칭 특성을 구하는 방법

크기가 증가하면 면적은 증가하고 스피드는 감소하게 된 다. 즉, 소자 매칭에 의한 아날로그 회로의 정확도와 스 피드는 기본적으로 trade-off 관계에 있다는 것을 알 수 있다.

(b) 저항기 매칭 패턴 〈그림 8〉 매칭 패턴의 종류

(a) N+ poly resistor

(b) P+ poly resistor 〈그림 9〉 Non-silicide poly resistor의 매칭 특성

## Ⅲ. 결론

아날로그 회로 설계를 위해 사용되는 아날로그 소자들의 종류, 특성 및 소자 기술에 대해 알아 보았다. 이러한소자 특성들이 정확하게 평가되어 모델에 반영되어 있어야 아날로그 설계에서 이를 이용한 정교한 설계가 이루어질 수 있다. 어떤 특정 회로에서는 아날로그 소자들의 노이즈나 선형성 등에 있어서 고성능 특성을 요구하는데 이것을 만족하는 아날로그 소자 개발이 필요하다.

# 참고 문헌

- Behzad Razavi, "Design of Analog CMOS Integrated Circuits," McGRAW-HILL International Edition, 2001,

- [2] W. Marshall Leach, JR., "Fundamentals of Low-Noise Analog Circuit Design," Proc. IEEE, vol. 82, Oct. 1994.

- [3] Hei Wong, Cheng, Y.C., "Modeling of low-frequency noise in metal-oxide-semiconductor field-effect transistor with electron trapping-detrapping at oxide-silicon interface," IEEE Trans. Electron Devices, vol. ED-38, Aug. 1991.

- [4] N. C. C. Lu, L., Grzberg, C. Y. Lu, and J. D. Mwindl, Hei Wong, Cheng, "Modeling and optimization of Monolithic polycrystalline silicon resistors," IEEE Trans. Electron Devices, vol. ED–28, Jul. 1981.

이희승

- 1989년 고려대학교 공학사 (재료공학)

- 1991년 한국과학기술원 공학석사 (재료공학)

- 2002년 한국과학기술원 공학박사 (재료공학)

- 1991년~1997년 현대전자

- 2002년~2004년 하이닉스 반도체

- 2005년~현재 매그나칩 반도체

#### 〈관심분야〉

Analog & mixed signal 소자 개발, Logic process integration, Sensor 기술 개발

이 정 환

- 1983년 한양대학교 공학사

- 1985년 한국과학기술원 공학석사

- 1996년 미국 Drexel University 공학박사

- 1985년~1988년 삼성전자 연구원

- 1989년~2004년 하이닉스 반도체 수석 연구원

- 2005년~현재 매그나칩 반도체 전무

#### 〈관심분야〉

Analog 소자 개발, Sensor 기술 개발, BCD Tech 개발, NVM Tech 개발, RF 소자 개발, ESD 소자 개발