# **Characterization of Dielectric Relaxation and Reliability of High-k MIM Capacitor Under Constant Voltage Stress**

Ho-Young Kwak<sup>1</sup>, Sung-Kyu Kwon<sup>1</sup>, Hyuk-Min Kwon<sup>1</sup>, Seung-Yong Sung<sup>1</sup>, Su Lim<sup>2</sup>, Choul-Young Kim<sup>1</sup>, Ga-Won Lee<sup>1</sup>, and Hi-Deok Lee<sup>1,\*</sup>

Abstract—In this paper, the dielectric relaxation and reliability of high capacitance density metal-insulatormetal (MIM) capacitors using  $Al_2O_3$ -HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub>-HfO<sub>2</sub>-SiO<sub>2</sub> sandwiched structure under constant voltage stress (CVS) are characterized. These results indicate that although the multilayer MIM capacitor provides high capacitance density and low dissipation factor at room temperature, it induces greater dielectric relaxation level (in ppm). It is also shown that dielectric relaxation increases and leakage current decreases as functions of stress time under CVS, because of the charge trapping effect in the high-k dielectric.

*Index Terms*—MIM (Metal-Insulator-Metal), AHA (Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub>), SHS (SiO<sub>2</sub>-HfO<sub>2</sub>-SiO<sub>2</sub>), charge trapping effect, dielectric relaxation

#### I. INTRODUCTION

Metal-Insulator-Metal (MIM) capacitors are widely used for in integrated circuit applications, such as analogto-digital (A/D) converters, digital-to-analog (D/A) converters, and resonators, due to their low parasitic capacitance, and low series resistance [1, 2]. Recently, the MIM capacitors have generated great attention in silicon integrated circuit (IC) applications as passive components, because the total area of passive devices, capacitors in particular, usually consumes a large portion of the whole chip size. Therefore, MIM capacitors with a high capacitance density have been required in order to increase the circuit density and reduce the system cost [3]. Silicon dioxide (SiO<sub>2</sub>,  $\sim$ 3.9) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>,  $\sim$ 7) are commonly used as insulator materials in conventional MIM capacitors. Although these conventional dielectric materials have good voltage linearity and low temperature coefficients, their capacitance density has been limited, owing to their low dielectric constant. Achieving high capacitance density by reducing the thickness of conventional dielectric materials, silicon dioxide (SiO<sub>2</sub>) and silicon nitride  $(Si_3N_4)$ , has led to high leakage current and reliability issues [4]. Therefore, the use of high-k dielectric materials, such as  $HfO_2$  (~25),  $Al_2O_3$  (~9),  $ZrO_2$  (~20),  $Ta_2O_5(\sim 25)$ , and  $TiO_2(\sim 80)$ , is necessary to increase the capacitance density and reduce the leakage current. Due to outstanding properties, such as high capacitance density, good thermal stability, and high band gap, hafnium-oxide based MIM capacitors are widely used for next generation capacitors [5]. However, MIM capacitor with single high-k dielectric shows high leakage current. In the last few years, laminate or sandwiched structures of MIM capacitor by adding Al<sub>2</sub>O<sub>3</sub> or SiO<sub>2</sub> layers have been studied to reduce the leakage current. However, it is known that MIM capacitors with high-k dielectric have many defects in the metal-insulator interface, which implies that the injected charges in the interface of high-k dielectric induce greater change of capacitor characteristics than those in the interface of conventional

Manuscript received May. 8, 2014; accepted Sep. 1, 2014 A part of this work was presented in Korean Conference on

Semiconductors, Seoul in Korea, Feb. 2014.

<sup>&</sup>lt;sup>1</sup> Dept. of Electronics Engineering, Chungnam National University, Daejeon 305-764, Korea

<sup>&</sup>lt;sup>2</sup> Dongbu HiTek Semiconductor Inc., Bucheon, Gyeonggi 420-712, Korea

E-mail : hdlee@cnu.ac.kr, Tel : +82-42-821-6868

dielectric materials do [6]. These cause a large dependence of capacitance performance on applied voltage and temperature. Also, it is shown that performance of MIM capacitors degrades by electrical stress [7]. Dielectric relaxation (DR) is one of the related phenomena, due to the trapping and de-trapping mechanism in the high-k dielectric [8]. DR can degrade the performance, like analogue and digital converters (ADC) and voltage controlled oscillators (VCO) linearity [9]. However, there has been little study of electric stress associated with DR.

In this paper, reliability and dielectric relaxation of MIM capacitors, in particular, of advanced capacitors with  $Al_2O_3$ -  $HfO_2$ -  $Al2O_3$  (AHA) and  $SiO_2$ - $HfO_2$ - $SiO_2$  (SHS) sandwiched structure are analyzed under constant voltage stress (CVS).

#### **II. EXPERIMENT**

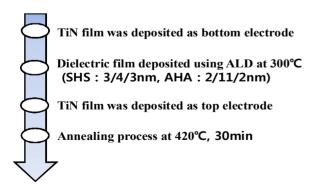

Fig. 1 shows the process flow by which the MIM capacitors used in this experiment were fabricated, with sandwiched dielectric structure of  $Al_2O_3/HfO_2/Al_2O_3$  and  $SiO_2/HfO_2/SiO_2$ . MIM capacitors were fabricated on 8-inch p-type silicon substrates. TiN layer was used as the bottom electrode. After that, the stacked dielectric layers with  $Al_2O_3$  (2 nm),  $HfO_2$  (11 nm), and  $Al_2O_3$  (2 nm) and  $SiO_2$  (3 nm),  $HfO_2$  (4 nm), and  $SiO_2$  (3 nm) were sequentially deposited using the atomic layer deposition (ALD) method at 300 °C. Finally, TiN layer was deposited and patterned, to form the top electrode.

A conventional MIM capacitor with  $Si_3N_4$  was also fabricated using PE-CVD method for comparison. An Al-Cu layer was used as the bottom electrode and a TiN layer was used as the top electrode.

Fig. 1. Process flow for fabrication of MIM capacitor with sandwiched structure.

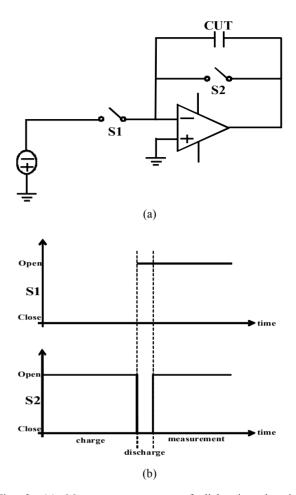

Fig. 2. (a) Measurement system of dielectric relaxation characteristic for MIM capacitor, (b) timing diagram of the switches.

CVS is applied using an Agilent 4156C semiconductor parameter analyzer. The DR characteristic was evaluated using the measurement system shown in Fig. 2(a). Fig. 2(b) shows the clock signals applied to switches for measurement of dielectric relazation. In the charge period, switch 1 is closed and switch 2 is opened. During the discharge period, switch 1 is opened and switch 2 is closed, vice versa. Finally, in the measurement period, switch 1 and switch 2 are opened.

## **III. RESULT AND DISCUSSION**

DR is a carrier absorption/relaxation phenomenon between the electrodes and the interface of dielectric. There are two methods to measure DR characteristic in the time domain. One is the "recovery voltage" technique [10] and the other is the "discharge current" method [11]. For the accurate evaluation of DR characteristic, we used

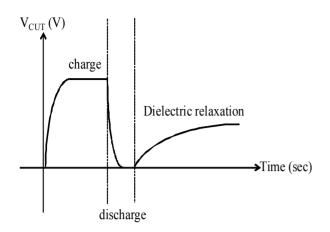

Fig. 3. Normalized voltage across the MIM capacitor during measurement of dielectric relaxation.

the first method. Fig. 3 shows the change of capacitor voltage with measurement time. The positive recovery voltage is measured from negative voltage potential because the charging voltage is applied to the bottom electrode. The top plate may be grounded or left floating, and the bottom plate may be grounded or being charged. Capacitor is charged for a long time then momentarily shorted the capacitor for a short time. Finally, the capacitor remained floating state and the voltage at the terminals is measured over time.

At a given applied charging voltage, traps in the interface of the dielectric become gradually filled over time. Due to the detrapped charged from these trap sites in the dielectric, the voltage of the capacitor rises slowly after the floating period.

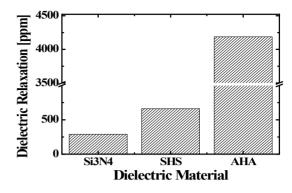

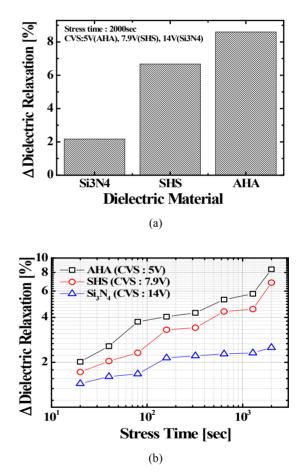

Fig. 4 shows the dielectric relaxation level (in ppm), with various dielectric materials of the MIM capacitor. It shows that MIM capacitor with high-k dielectric has a higher DR level than that with a conventional dielectric material, because the high-k dielectrics have more traps in the dielectric than conventional dielectric materials, such as  $SiO_2$ , and  $Si_3N_4$ .

Fig. 5 shows the increase of DR value after CVS for 2000 sec. We applied the same effective electric field  $(E_{\text{eff}})$  to the MIM capacitors for an accurate comparison of the dielectric relaxation characteristics. We normalized the thickness of the dielectric layer in terms of HfO<sub>2</sub> equivalent as defined below. Therefore, the normalized thicknesses (t<sub>eff</sub>) are defined as (1) and (2).

$$t_{eff.AHA} = t_{HfO_2} + \frac{\varepsilon_{HfO_2}}{\varepsilon_{Al_2O_3}} t_{Al_2O_3}$$

(1)

**Fig. 4.** Dielectric relaxation characteristic of the MIM capacitor with dielectric material.

**Fig. 5.** Time evolution of dielectric relaxation under CVS according to the dielectric material (a) during 2000 sec, (b) like NBTI stressing for 2000 sec.

$$t_{eff.SHS} = t_{HfO_2} + \frac{\varepsilon_{HfO_2}}{\varepsilon_{SiO_2}} t_{SiO_2}$$

(2)

Then, the effective electric field is defined as (3).

$$E_{eff} = \frac{V_{AHA}}{t_{eff,AHA}} = \frac{V_{SHS}}{t_{eff,SHS}} = \frac{V_{Si_3N_4}}{t_{eff,Si_3N_4}}$$

(3)

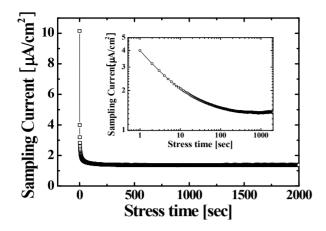

Fig. 6. Characteristic of leakage current with stress time under CVS.

The applied voltage for CVS of AHA, SHS, and  $Si_3N_4$ dielectrics were 5V, 7.9V, and 14V, respectively. Fig. 5 indicates that the high-k dielectrics show a great increase of DR than conventional dielectric material. The largest variation of DR occurs in the AHA structure. This is because HfO<sub>2</sub> has the largest prefactor among the various high-k dielectric materials, related to the charge losses in DRAMs and V<sub>T</sub>-shift in MOSFETs [12]. Figs. 5(a) and (b) show a similar increase in DR value.

Fig. 6 shows that the leakage current decreases during CVS for SHS structure. It is caused by the generation of traps and electron trapping in the dielectric. At the initial state under CVS, the reduction of leakage is great, because the generation of traps occurs mainly near the interface of dielectric and the electrode. Figs. 5 and 6 indicate that the charge trapping effect with CVS causes the variation of dielectric relaxation value.

## **IV. CONCLUSIONS**

In this paper, we analyzed the dielectric relaxation characteristics and reliability of MIM capacitors with  $Al_2O_3/HfO_2/Al_2O_3$  and SiO2/HfO\_2/SiO\_2 sandwiched structures under constant voltage stress. It is shown that a MIM capacitor with high-k dielectric has a higher dielectric relaxation (DR) level, and greater increase of DR value uncer constant voltage stree (CVS) than does conventional dielectric material. The leakage current decreases with stress-time under CVS. The charge trapping effect in the dielectric contributes to the variation of the variation of the capacitor parameters.

### **ACKNOWLEDGMENTS**

This work (research) is financially supported in part by the Ministry of Knowledge Economy (MKE) and Korea Institute for Advancement of Technology (KIAT) through the Workforce Development Program in Strategic Technology. This work was also partially supported by the IT R&D program of MKE/KEIT. [10041855, Development of e-NVM (embedded Non-Volatile Memory) Analog mixed signal-based Convergence process technology & IP].

### REFERENCES

- C. C Huang, C. H. Cheng, A. Chin, and C. P. Chou, "Leakage Current Improvement of Ni/TiNiO/TaN Metal-Insulator-Metal Capacitors using Optimized N<sup>+</sup> Plasma Treatment and Oxygen Annealing," *Electrochemical and Solid-State Letters*, Vol.10, No.10, pp.H287-H290, Jul. 2007.

- [2] V. Mikhelashvili, G. Eisenstein, and A. Lahav, "High capacitance density metal-insulator-metal structure based on Al<sub>2</sub>O<sub>3</sub>-HfTiO nanalaminate stacks," *Appl. Phys. Lett.*, Vol.90, No.1, pp.013 506 (1-3), Jan. 2007.

- [3] H. Hu, C. Zhu, Y. F. Lu, Y. H. Wu, T. Liew, M. F. Li, B. J. Cho, W. K. Choi, and N. Yakovlev, "Physical and elecrical characterization of HfO<sub>2</sub> metal-insulator-metal capacitors for Si analog circuit applications," *J. Appl. Phys*, Vol.94, No.1, pp.551-557, Jul. 2003.

- [4] T. Remmel, R. Ramprasad, and J. Walls, "Leakage Behavior and Reliability Assessment of Tantalum Oxide Dielectric MIM Capacitors," *Proc. Int. Reliability Physics Symp.*, pp.277-281, Mar. 2003.

- [5] X. Yu, C. Zhu, H. Hu, A. Chin, M. F. Li, B. J. Cho, D. L. Kwong, P. D. Foo, and M. B. Yu, "A highdensity MIM capacitor (13fF/µm<sup>2</sup>) using ALD HfO<sub>2</sub> dielectrics," *IEEE Electron Device Lett.*, Vol.24, No.2, pp.63-65, Feb, 2003.

- [6] J. Babcock, S. Balster, A. Pinto, C. Dirnecker, P. Steinmann, R. Jumpertz, and B. El-Kareh, "Analog characteristics of metal-insulator-metal capacitors using PECVD nitride dielectrics," *IEEE Electron Device Lett.*, Vol.22, No.5, pp.230-232, May, 2001.

- [7] H. Y. Kwak, H. M. Kwon, Y. J. Jung, S. K. Kwon,

J. H. Jang, W. I Choi, M. L. Ha, J, I, Lee, S. J. Lee and H. D. Lee, "Characterization of Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> sandwiched MIM capacitor under DC and AC stresses", SSE, Vol.79, pp.218-222, Jan, 2013.

- [8] Z. Ning, H. Casier, R. Gillon, H.X. Delecourt, D. Tack, E. D. Vylder, P. V. Torre and D. Hegsted, "Analog characterization of dielectric relaxation of MIM capacitor using an improved recovery voltage technique," *IEEE Intenational Conference on Microelectronic Test Structures (ICMTS)*, pp.109-114, Mar. 2007.

- [9] A. Zanchi, F. Tsay, and I. Papantonopoulos, "Impact of Capacitor Dielectric Relaation on a 14bit 70-MS/s pipeline ADC in 3-V BiCMOS," *IEEE Journal of Solid-State Circuits*, Vol.38, No.12, pp.2077-2086, Dec, 2003.

- [10] J. C. Kuenen and G. M. Meijer, "Measurement of dielectric absorption of capacitors and analysis of its effects on VCOs," *IEEE Tras. on Instrumentation nad Measurement*, Vol.45, No.1, pp.89-97, Feb. 1996.

- [11] Z. Xu, L. Pantisano, A. Kerber, R. Degraeve, E. Cartier, S. De Gendt, M. Heyns and G. Groeseneken, "A study of relaxation current in high-k dielectric stacks," *IEEE Trans Electron Devices*, Vol. 51, No.3, pp.402-408, Mar. 2004.

- [12] H. Reisinger, G. Steinlesberger, S. Jakschik, M. Gutsche, T. Hecht, M. Leonhard, U. Schroder, H. Seidl, and D. Schumann, "A comparative study of dielectric relaxation losses in alternative dielectrics," *in IEDM tech. Dig.*, pp.12.2.1-12.2.4, Dec. 2001.

**Sung-Kyu Kwon** received the B.S. degree and M.S. degree in electronics engineering from the Chungnam National University, Daejeon, Korea in 2011 and 2013. Since 2013, he has been a Ph.D. student in electronics engineering from the Chungnam

National University, Daejeon, Korea. His main research interests include reliability and low frequency noise characteristics of nano-CMOS devices for analog mixed signal application.

Hyuk-Min Kwon Hyuk-Min Kwon received the B.S., M.S., and Ph.D. degrees from Chungnam National University, Daejeon, Korea, in 2007, 2009, and 2014, respectively, all in electronics engineering. He has been with SEMATECH, Austin, TX, USA,

as a Visiting Research Scholar, since 2013. He is currently involved in nanoscale CMOS technology, reliability physics, test pattern for matching, RF CMOS modeling, and low-frequency noise for nano-CMOS, Ge/III–V quantum well MOSFETs and Fin-FETs.

**Seung-Yong Sung** received B.S. and M.S. degrees in electronics engineering fron Chungnam National University, Daejeon. Korea. in 2012 and 2014, respectively. His main research interests include characterization and reliability of nano-scale CMOS device

and EDMOS for analog mixed-signal applications.

**Su Lim** received the B.S. and M.S. degrees in electronics engineering from Chungnam National University, Daejeon, Korea, in 2002 and 2004, respectively. Since 2004, he joined Dongbu HiTek Semiconductor Inc., Bucheon, Korea, where he has been

involved in developing mixed signal products of 0.18µm CMOS technology. Since 2010, he has been developing devices characterization and measurement methodology of CMOS/BCD technologies.

**Ho-Young Kwak** was born in Daejeon. Korea in 1985. He received B.S. and M.S. degrees in electronics engineering fron Chung-nam National University, Daejeon. Korea. in 2011 and 2013, respectively. His major research interests include characteri-

zation and reliability of high-k dielectrics of CMOS devices for analog mixed-signal applications.

**Choul-Young Kim** (S'04) received the B.S. degree in electrical engineering from Chungnam National University (CNU), Daejeon, Korea, in 2002 and M.S. and Ph.D degrees in electrical engineering from Korea Advanced Institute of Science and

Technology (KAIST), Daejeon, Korea, in 2004 and 2008, respectively. From March 2009 to February 2011, he was a Postdoctoral Research Fellow at the department of electrical and computer engineering at the University of California, San Diego (UCSD). He is assistant professor of electronics engineering at Chungnam National University, Daejeon, Korea. His research interests include mm-wave integrated circuits and systems for short range radar and phased-array antenna applications.

**Ga-Won Lee** received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, Korea, in 1994, 1996, and 1999, respectively. In 1999, she joined Hynix Semiconductor Ltd.

as senior research engineer, where she was involved in the development of 0.115- $\mu$ m, 0.09- $\mu$ m DDRII DRAM technologies. Since 2005, she has been in Chungnam National University, Daejeon, Korea, as a Professor with the Department of Electronics Engineering. Her main research fields are flash memory, flexible display technology including fabrication, electrical analysis and modeling.

**Hi-Deok Lee** received a B.S., M.S., and Ph.D. degrees in Electrical Engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1990, 1992, and 1996, respectively. In 1993, he joined the

LG Semicon Company, Ltd. (currently SK Hynix Semiconductor Ltd.), Chongju, Choongbuk, Korea, where he has been involved in the development of 0.35µm, 0.25-µm, and 0.18-µm CMOS technologies, respectively. He was also responsible for the development of 0.15-µm and 0.13-µm CMOS technologies. Since 2001, he has been with Chungnam National University, Daejeon, Korea, with the Department of Electronics Engineering. From 2006 to 2008, he was with the University of Texas, Austin, and SEMATECH, Austin, as a Visiting Scholar. His research interests are in nanoscale CMOS technology and its reliability physics, silicide technology, and Test Element Group design. His research interests also include development of high performance analog and high voltage MOSFETs, and high efficient silicon solar cells. Dr. Lee is a member of the Institute of Electronics Engineers of Korea.