# **On-State Resistance Instability of Programmed Antifuse Cells during Read Operation**

Jae Hwan Han, Hyunjin Lee, Wansoo Kim, Gyuhan Yoon, and Woo Young Choi

Abstract—The on-state resistance  $(R_{ON})$  instability of standard complementary metal-oxide-semiconductor (CMOS) antifuse cells has been observed for the first time by using acceleration factors: stress current and ambient temperature. If the program current is limited, the  $R_{\rm ON}$  increases as time passes during read operation.

Index Terms—Antifuse, reliability, on-state resistance instability

### I. INTRODUCTION

Among various kinds of one-time programmable (OTP) memory technologies, the standard complementary metaloxide-semiconductor (CMOS) antifuse cell based on conventional polysilicon-gate with silicon dioxide gate insulator has been regarded as one of the most promising technologies. It is usually used for the redundancy memory of dynamic random access memory (DRAM) or static RAM (SRAM) [1-4]. This antifuse cell is costeffective because its fabrication process is compatible with CMOS baseline process.

In terms of the reliability of an antifuse cell, the onstate resistance  $(R_{ON})$  instability of the programmed cell during read operation is an important issue. The  $R_{ON}$ instability means the time-dependent resistance increase of the conductive filament (CF) in the programmed

antifuse cell during read operation. It can induce the read disturb: the  $R_{ON}$  increase of programmed antifuse cells to an off-state resistance ( $R_{OFF}$ ) level during read operation. In the case of metal-insulator-metal (MIM) antifuse cells, read disturb problems have already been reported [5, 6]. On the other hand, in the case of standard CMOS antifuse cells, few research results on read disturb problems have been reported yet. It is because the thermal hard breakdown (HBD) of a silicon dioxide film with Joule heating effects does not recover.

If the stress current is limited during the breakdown process of an ultra-thin silicon dioxide film, the post-HBD leakage conductance is similar to that of a quantum point contact. It means that a CF is regarded as an atomsized constriction, which is explained by the quantum point contact HBD (QPC-HBD) model [7]. The antibreakdown has been reported which means that the reversibility of the QPC-HBD path in an ultra-thin silicon dioxide film [8, 9]. The anti-breakdown is induced by the rearrangement of defects which form CFs. The rearrangement process is driven by electron wind force [8, 9]. Because the program current of an on-chip antifuse cell is limited, the CFs of programmed antifuse cells can be formed by the QPC-HBD. Thus, the  $R_{ON}$  of programmed antifuse cells may vary during read operation:  $R_{ON}$  instability.

In this paper, It has been observed that the  $R_{\rm ON}$ instability of programmed standard CMOS antifuse cells by using stress current and ambient temperature as acceleration factors for the first time. Also, the data retention of programmed standard CMOS antifuse cells has been discussed.

Manuscript received Apr. 2, 2014; accepted Aug. 23, 2014 A part of this work was presented in Korean Conference on Semiconductors, Seoul in Korea, Feb. 2014.

Department of Electronic Engineering, Sogang University, 35 Baekbeom-ro (Sinsu-dong), Mapo-gu, Seoul 121-742, Korea E-mail : wchoi@sogang.ac.kr

## **II. MEASUREMENT CONDITION**

The  $R_{\rm ON}$  instability during read operation is generally negligible as long as stress current is low. Thus, in order to observe the  $R_{ON}$  instability within short measurement time, acceleration factors should be introduced. In order to accelerate the  $R_{ON}$  instability, the electron wind force needs to be strengthened. It is well-known that the intensity of the electron wind force is related to the current and temperature [10]. Thus, it is predicted that the  $R_{\rm ON}$  instability will be accelerated when the antifuse cells are exposed to high stress current and temperature.

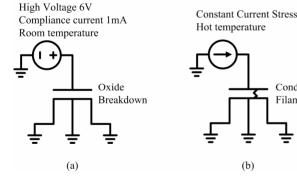

For experiments, we have used typical single antifuse test patterns based on n-channel MOSFET in sub 30 nm technology node for DRAM. As shown in Fig. 1(a) antifuse cells are programmed at room temperature by 6-V gate voltage with program current fixed at 1 mA. This program condition has been selected in order to form QPC-HBD paths. Subsequently, in order to observe the  $R_{\rm ON}$  instability, the programmed cells are exposed to constant current stress as shown in Fig. 1(b). The stress current should be lower than the program compliance current in order to prevent the phase change of CFs by Joule heating at high temperature. The accelerated stress conditions are summarized in Table 1.

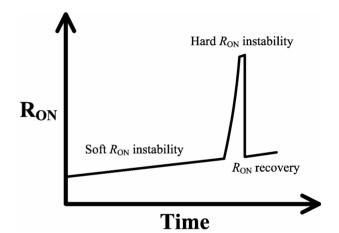

The  $R_{ON}$  instability consists of three regions as shown in Fig. 2. The first region is defined as "soft  $R_{ON}$ instability region" where  $R_{ON}$  increases slightly. The second region is defined as "hard  $R_{ON}$  instability region" where  $R_{ON}$  increases abruptly. The last region is defined as " $R_{ON}$  recovery region" where the  $R_{ON}$  increased in the hard  $R_{\rm ON}$  instability region is recovered to its initial value.

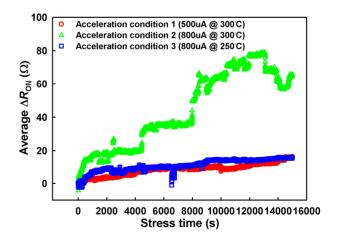

Fig. 3 shows the average  $R_{\rm ON}$  variation ( $\Delta R_{\rm ON}(t) \equiv$  $R_{\rm ON}(t)$  -  $R_{\rm ON}(0)$  in the soft  $R_{\rm ON}$  instability region of several samples measured under the three acceleration conditions as shown in Table 1. Fig. 3 clearly shows the two acceleration factors of  $R_{ON}$  instability: stress current and ambient temperature. In the first place, comparing the acceleration condition 1 with 2,  $R_{on}$  instability is accelerated as stress current increases. The  $R_{\rm ON}$  in the

Fig. 1. (a) Program condition, (b) read disturb measurement.

Table 1. Acceleration conditions for read disturb measurement

Condutive

Filament

|                             | Stress current | Ambient temperature |

|-----------------------------|----------------|---------------------|

| Acceleration condition 1    | 500 μΑ         | 300°C               |

| Acceleration condition 2    | 800 μΑ         | 300°C               |

| Acceleration<br>condition 3 | 800 μΑ         | 250°C               |

Fig. 2. Three regions of the  $R_{ON}$  instability: soft  $R_{ON}$  instability, hard  $R_{\rm ON}$  instability and  $R_{\rm ON}$  recovery region.

Fig. 3.  $\Delta R_{ON}(t)$  in soft  $R_{ON}$  instability region under each acceleration condition.

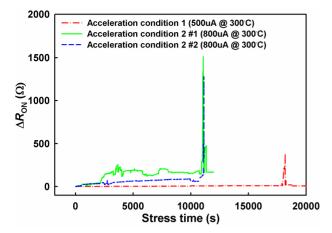

**Fig. 4.**  $\Delta R_{ON}(t)$  of programmed antifuse cells showing a hard  $R_{ON}$  instability event.

acceleration condition 2 increases more rapidly than that in the acceleration condition 1.  $R_{\rm ON}$  increases ~4.4 mΩ/s under the acceleration condition 2, whereas  $R_{\rm ON}$ increases ~1.1 mΩ/s under the acceleration condition 1. In the same manner, the comparison between the acceleration condition 2 with 3 shows that high temperature accelerates  $R_{\rm ON}$  instability. The  $R_{\rm ON}$  in the acceleration condition 2 increases more rapidly than that in the acceleration condition 3.  $R_{\rm ON}$  increases ~4.4 mΩ/s under the acceleration condition 2, whereas  $R_{\rm ON}$ increases ~1.0 mΩ/s under the acceleration condition 3.

Some of the measured antifuse cells exhibit hard  $R_{ON}$  instability which is similar to anti-breakdown as shown in Fig. 4. It is because the rearrangement of defects by electro-migration effects eventually makes CFs narrower or disconnected. These unusual cells also exhibit the same trend as in Fig. 3 ahead of the hard  $R_{ON}$  instability region. It means that the occurrence of the hard  $R_{ON}$  instability is determined randomly depending on the atomic topology of CFs. Hard  $R_{ON}$  instability events occur earlier, more frequently and more rapidly in the acceleration condition 2 than in acceleration condition 1. Also, no hard  $R_{ON}$  instability event has been observed in the acceleration condition 3. Thus, it is expected that hard  $R_{ON}$  instability will show the same trend as soft  $R_{ON}$  instability.

However, in our experiment,  $R_{ON}$  does not increase to the  $R_{OFF}$  level which is larger than several M $\Omega$ , as shown in Fig. 4, even in the case of hard  $R_{ON}$  instability. If multiple hard  $R_{ON}$  instability events occur repeatedly, read disturb may occur. However,  $R_{ON}$  is recovered to its initial value before another hard  $R_{ON}$  instability event occurs because the high electric field applied across the unoccupied CF spots generates new defects. This  $R_{ON}$ recovery occurs hundreds of seconds after hard  $R_{ON}$ instability event. However, it takes more than 10,000 s to induce the hard  $R_{ON}$  instability. Thus, it is not probable that  $R_{ON}$  instability occurs repeatedly without  $R_{ON}$ recovery. Therefore, in spite of the hard  $R_{ON}$  instability, it is predicted that read disturb will not occur, even at 300 °C. Obviously, CFs in the programmed antifuse cell have been guaranteed for ten years at room temperature.

# **III. SUMMARY**

The  $R_{ON}$  instability of the programmed CMOS antifuse cells has been investigated by using the two acceleration factors: stress current and ambient temperature. Based on experimental results, it has been found that the  $R_{ON}$ instability depends on the stress current and ambient temperature for the first time. Then, it has been confirmed that read disturb will not occur in the case of CMOS antifuse cells.

#### ACKNOWLEDGMENTS

This work was supported in part by the NRF of Korea funded by the MSIP under Grant NRF-2012R1A2A2A01006159 (Mid-Career Researcher Program), in part by the NIPA funded by the MSIP under NIPA-2014-H0301-14-1007 Grant (Information Technology Research Center). part the in by MOTIE/KSRC under Grant 10044842 (Future Technology Semiconductor Device Development Program) and in part by the Sogang University Research Grant of 2014 (201410038).

### REFERENCES

- P. Candelier, N. Villani, J.-P. Schoellkopf, and P. Mortini, "One time programmable drift antifuse cell reliability," *Proc. IEEE Int. Reliabil. Phys. Symp.*, pp. 169-173, Apr., 2000.

- [2] J. Kim and K. Lee, "Three-transistor one-time programmable (OTP) ROM cell array using standard CMOS gate oxide antifuse," *IEEE Electron Device lett.*, vol. 24, no. 9, pp. 589-591,

Sept. 2003

- [3] H. Ito and T. Namekawa, "Pure CMOS one-time programmable memory using gate-ox anti-fuse," *Proc. IEEE Custom Integr. Circuits Conf.*, pp.469-471, Oct. 2004.

- [4] H.-K. Cha, I. Yun, J. Kim, B.-C So, K. Chun, I. Nam, and K. Lee, "A 32-KB Standard CMOS antifuse one-time programmable ROM embedded in a 16-bit microcontroller," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 9, pp. 2115-2124, Sep., 2006.

- [5] R. J. Wong, K. E. Gordon, and A. K. Chan, "Time dependent reliability of the programmed metal electrode antifuse," *Proc. IEEE Int. Reliabil. Phys. Symp.*, pp. 22-26, May 1996..

- [6] N. Vasudevan, R. B. Fair, H. Z. Massoud, T. Zhao, K. Look, Y. Karpovich, and M. J. Hart, "ON-state reliability of amorphous-silicon antifuses," *Journal* of *Appl. Phys.*, vol. 84, no. 11, pp. 6440-6447, Dec., 1998.

- [7] J. Sune, E. Miranda, M. Nafria, and X. Aymerich, "Point contact conduction at the oxid breakdown of MOS devices," in *IEEE International Electron Devices Meeting*, pp. 191-194, Dec., 1998.

- [8] E. Miranda, J. Sune, R. Rodriguez, M. Nafria, and X. Aymerich, "Conduction properties of breakdown paths in ultrathin gate oxides," *Microelectron Reliab.* vol. 40, pp. 687-690, Apr. 2000.

- [9] E. Miranda, J. Sune, R. Rodriguez, M. Nafria, and X. Aymerich, "Breakdown and anti-breakdown events in high-field stressed ultrathin gate oxides," *Solid-State Electron.*, vol. 45, pp. 1327-1332, Aug., 2001.

- [10] J. R. Black, "Electromigration a brief survey and some recent results," *IEEE Transaction on Electron Devices*, vol. ED-16, no. 4, pp. 338-347, 1969.

Jae Hwan Han was born in Seoul, Korea, in 1989. He received the B.S., and M.S. degrees in electronic engineering from Sogang University, Seoul, Korea, in 2012, and 2014, respectively His current research interests include CMOS compatible

nanoelectro- mechanical memory cells and antifuse cells.

Hyunjin Lee received the B.S., M.S., and Ph.D. degrees in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2001, 2003, and 2007, respectively. She joined Research and Development

Division of SK Hynix Semiconductor, Korea, in 2007, where she has been involved in the process integration of DRAM. Her current work focuses on L4X, L2X DRAM Technology and advanced DRAM technology.Dr. Lee received the Best Student Paper Award of the 2006 Symposium on VLSI Technology.

Wan Soo Kim was born in Chunju, Korea, in 1967. He received the B.S., and M.S. degrees in the Electrical Engineering from Kwangwoon University, Seoul, Korea in , 1991 and 1994, respectively. From 1994 to 2014, He is working a senior DRAM

Process Integrated Engineer for SKHINIX. He is currently with the Logic Device Development Group. His current research interest include sigma eSiGe and RMG for current boosting and gate leakage reduction

**Gyu Han Yoon** received the B.S., and M.S. degrees in the School of Electrical Engineering from Sogang University, Seoul, Korea in 1981 and 1984, respectively. In 1984, He joined the memory development group, LG Semiconductor, where he

worked on product engineering for EPROM, SRAM and DRAM, From 2000 to 2009, he was an executive manager of R&D division, Hynix Semiconductor, where he was responsible for DRAM and CIS development. He is currently a director of semiconductor group, Sogang Institute of advanced technology, Sogang University. He has authored or coauthored over 10 papers. He is the holder of 20 Korean patents and 4 international patents. His current research interests include the reliability of semiconductor memory.

**Woo Young Choi** was born in Incheon, Korea, in 1978. He received the B.S., M.S. and Ph. D. degrees in the School of Electrical Engineering from Seoul National University, Seoul, Korea in 2000, 2002 and 2006, respectively. From

2006 to 2008, he was with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, USA as a post-doctor. Since 2008, he has been a member of the faculty of Sogang University (Seoul, Korea), where he is currently an Associate Professor with the Department of Electronic Engineering. He has authored or coauthored over 170 papers in international journals and conference proceedings and holds 30 Korean patents. His current research interests include fabrication, modeling, characterization and measurement of CMOS/CMOScompatible semiconductor devices and nanoelectromechanical (NEM) devices.