# SiGe 에피 공정기술을 이용하여 제작된 초 접합 금속-산화막 반도체 전계 효과 트랜지스터의 시뮬레이션 연구

이훈기 · 박양규 · 심규환 · 최철종†

†전북대학교 반도체화학공학부 반도체 물성 연구소

# Simulation Studies on the Super-junction MOSFET fabricated using SiGe epitaxial process

#### Hoon-Ki Lee, Yang-Kyu Park, Kyu-Hwan Shim and Chel-Jong Choi<sup>†</sup>

<sup>†</sup>School of Semiconductor and Chemical Engineering, Semiconductor Physic Research Center, (SPRC), Chonbuk National University, Jeonju 561-756, Korea

#### **ABSTRACT**

In this paper, we propose a super-junction MOSFET (SJ MOSFET) fabricated through a simple pillar forming process by varying the Si epilayer thickness and doping concentration of pillars using SILVACO TCAD simulation. The design of the SJ MOSFET structure is presented, and the doping concentration of pillar, breakdown voltage ( $V_{BR}$ ) and drain current are analyzed. The device performance of conventional Si planar metal-oxide semiconductor field-effect transistor(MOSFET), Si SJ MOSFET, and SiGe SJ MOSFET was investigated. The p- and n-pillars in Si SJ MOSFET suppressed the punch-through effect caused by drain bias. This lead to the higher  $V_{BR}$  and reduced on resistance of Si SJ MOSFET. An increase in the thickness of Si epilayer and decrease in the former is most effective than the latter. The implementation of SiGe epilayer to SJ MOSFET resulted in the improvement of  $V_{BR}$  as well as drain current in saturation region, when compared to Si SJ MOSFET. Such a superior device performance of SiGe SJ MOSFET could be associated with smaller bandgap of SiGe which facilitated the drift of carriers through lower built-in potential barrier.

Key Words: Super-junction MOSFET, SiGe, P-pillar, N-pillar, breakdown voltage, drain current

#### 1. 서 론

전력 소자의 한 종류인 초 접합 금속-산화막 반도체 전계 효과 트랜지스터는 실리콘 기반의 일반적인 전계 효과 트랜지스터의 항복 전압 대비 온-저항의 트레이드 오프 특성을 보완하기 위하여 개발되었다[1]. 지금까지 초 접합 금속-산화막 반도체 전계 효과 트랜지스터의 성능을 향상시키기 위하여 다양한 공정 기술이 개 발되어 왔다. 예를 들어, P 영역과 N영역의 도핑 농도를 최적화하여 전하 균형을 유지함으로써 항복 전압은 높지만 상대적으로 온-저항의 증가 비율을 최소화 할수 있다[2]. 또한, 다층 에피 공정을 이용한 기술[3-4]과

더불어 트랜치 필링 기술을 통하여 약 600 V 이상의 높은 항복 전압을 가지는 초 접합 금속-산화막 반도체 전계 효과 트랜지스터 소자를 구현할 수 있다[5-6]. 그러나, 이와 같은 방법들은 초 접합 금속-산화막 반도체 전계 효과 트랜지스터 소자를 구현하는데 공정 자체가 복잡할 뿐만 아니라 많은 시간과 비용이 소모된다는 문제점을 가지고 있다. 더욱이, 실리콘 물성 한계로 인하여 단순히 소자의 구조를 변경하여 소자 동작 특성을 향상시키는데 한계가 있다.

최근 화합물 반도체 재료를 이용하여 기존의 실리콘 반도체 소자의 성능을 획기적으로 개선하려는 많은 연 구가 진행되고 있다[7-9]. 다양한 화합물 반도체 재료 중 실리콘-게르마늄은 공정이 용이하고 저 비용, 대면 적으로 생산할 수 있는 장점을 가지고 있으며, 실리콘

†E-mail: cjchoi@jbnu.ac.kr

보다 월등히 빠른 전자의 이동도와 낮은 밴드갭을 가지는 우수한 특성으로 인하여 고주파, 저전력, 비메모리 소자 등에 적용되고 있다. 이러한 우수한 실리콘-게르마늄의 물성에도 불구하고 아직 이을 이용하여 초접합 금속-산화막 반도체 전계 효과 트랜지스터를 구현하기 위한 연구는 극히 제한적으로 진행되고 있다.

본 연구에서는 SILVACO TCAD 시뮬레이션을 이용하여 주요 공정 변수 별 초 접합 금속-산화막 반도체전계 효과 트랜지스터의 특성변화에 대해 연구하였다. 특히, 실리콘-게르마늄 에피 공정이 적용된 초 접합 금속-산화막 반도체 전계 효과 트랜지스터가 향 후 전력소자 응용에 매우 효율적으로 적용될 수 있다는 것을보이려고 한다.

## 2. 초 접합 금속-산화막 반도체 전계 효과 트랜지스터 시뮬레이션

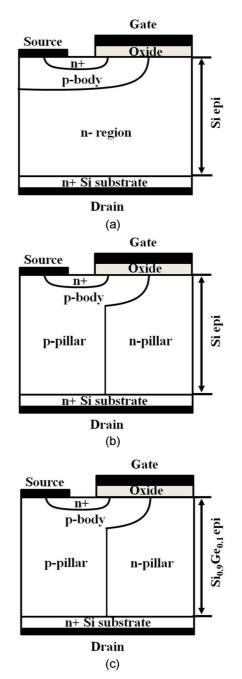

Fig. 1과 같은 구조의 실리콘 초 접합과 평면 금속-산화막 반도체 전계 효과 트랜지스터, 실리콘-게르마늄 초 접합 금속-산화막 반도체 전계 효과 트랜지스터를 SILVACO TCAD를 이용하여 시뮬레이션 하였다. 시뮬레이션을 하는데 있어 모든 소자 제작 공정은 인이  $1 \times 10^{18}$  /cm<sup>3</sup>도핑된 N+ (100) 실리콘 기판을 사용하였으며, 추가로 인이 $1 \times 10^{19}$ /cm<sup>3</sup> 만큼 도핑된N+ 폴리실리콘을 게이트 전극으로, 알루미늄을 소스 및 드레인 영역 접합용 금속 전극으로 사용하였다.

#### 2.1. 실리콘 초 접합 금속-산화막 반도체 전계 효과 트 랜지스터 시뮬레이션

인의 도핑농도가  $1\times10^{15}$  /cm³인 실리콘 층을 N+ (100) 실리콘 기판위에 32.5  $\mu$ m 두께로 에피 성장하였다. 다음으로, 전하 균형 효과를 극대화하기 위하여 p- 필라와 n-필라 영역의 도핑농도를  $1\times10^{15}$  /cm³로 동일하게 하였고, 필라 폭 크기를 각각  $4\mu$ m씩 유지하였다. P-바디 영역은 붕소로  $5\times10^{13}$  /cm³로 도핑을 하였고, 인의 농도가  $1\times10^{19}$  /cm³ 될 수 있도록 이온 주입 공정을 진행하여 N+ 소스 형성하였다.

### 2.2. 실리콘 평면 금속·산화물 반도체 전계 효과 트랜 지스터 시뮬레이션

실리콘 평면 금속-산화막 반도체 전계 효과 트랜지스터는 실리콘 초 접합 금속-산화막 반도체 전계 효과 트랜지스터와 유사한 구조를 가지지만, 필라의 구분이 없는 소자이기 때문에 인이  $1 \times 10^{15}$  /cm³ 도핑된 실리콘 에피층(두께 :  $32.5 \mu m$ )에 붕소를 이온 주입하여 p-

**Fig. 1.** Schematics of (a) Si Planar MOSFET, (b) Si SJ MOSFET and (c) SiGe SJ MOSFET employed in TCAD simulation

바디(도핑농도 :  $5\times10^{13}$  /cm³)를 형성하였다. 마지막으로 인의 이온 주입 공정을 이용하여  $1\times10^{19}$  /cm³의 도핑 농도를 갖는 N+ 소스를 형성하였다.

#### 2.3. 실리콘-게르마늄 초 접합 금속-산화막 반도체 전 계 효과 트랜지스터 시뮬레이션

실리콘 게르마늄 초 접합 금속-산화막 반도체전계 효과 트랜지스터의 시뮬레이션을 위해서 실리콘 초 접 합 금속-산화막 반도체 전계 효과 트랜지스터와 같은 구조로 공정을 진행하였다. P-바디, p-필라 및 n-필라 의 도핑 농도는 실리콘 초 접합 금속-산화막 반도체 전 계 효과 트랜지스터와 동일하지만, 실리콘 에피 대신에 게르마늄의 농도가 10 % 인 실리콘-게르마늄 화합물 을 32.5 μm 두께로 N+ (100) 실리콘 기판 위에 에피 성장하였다.

#### 3. 시뮬레이션 분석 결과

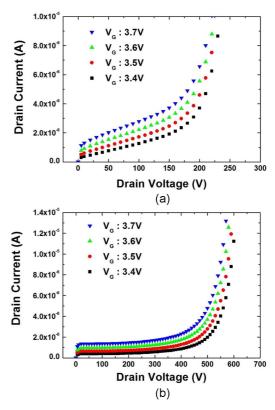

Fig. 2는 실리콘 평면 금속-산화막 반도체 전계 효과 트랜지스터와 실리콘 초 접합 금속-산화막 반도체 전 계 효과 트랜지스터의 드레인 전류 - 드레인 전압 특성 곡선에 대한 시뮬레이션 결과이다. 두 소자 모두 게이 트 전압이 증가함에 따라 항복 전압이 감소하였다. 그 러나, 실리콘 평면 금속-산화막 반도체 전계 효과 트랜 지스터의 항복 전압이 실리콘 초 접합 금속-산화막 반 도체 전계 효과 트랜지스터와 비교하여 약 2배 이상 낮은 것을 관찰 할 수 있었다. 더욱이, 평면 금속-산화 막 반도체 전계 효과 트랜지스터는 초 접합 금속-산화 막 반도체 전계 효과 트랜지스터와 달리 포화 상태 영 역에서 드레인 전류가 평형을 이루지 못하고 드레인 전압이 증가할수록 그 값이 급격히 증가하는 펀치스루 효과가 지배적 이었다. 즉, 펀치 스루 현상에 의해 낮 은 드레인 전압에도 누설 전류의 양이 증가하여 항복 전압이 감소함을 알 수 있다[10]. 초 접합 금속-산화막 반도체 전계 효과 트랜지스터가 평면 금속-산화막 반 도체 전계 효과 트랜지스터보다 우수한 항복 전압 특 성을 갖는 것은 필라 영역이 존재하기 때문이다. 즉, p-필라에 의해 드레인 전압에 의한 p-바디 채널의 공핍 층 확장이 제한되어 채널 길이가 일정하게 유지됨으로 써 높은 드레인 전압을 인가하여도 넓은 드레인 전류 포화 상태를 나타낼 수 있다. 또한, p-필라와 n-필라 접 합은 다수 캐리어와 소수 캐리어가 재결합되는 현상을 효과적으로 방지하여 평면 금속-산화막 반도체 전계 효과 트랜지스터에서 나타나는 전력 손실을 최소화 할 수 있다[11]. 더욱이 우수한 특성의 초 접합 금속-산화 막 반도체 전계 효과 트랜지스터를 구현하기 위해서는 p-필라와 n-필라 의 도핑농도가 동일한 전하 균형 상태 를 유지해 주어야 한다[12-13].

초 접합 금속-산화막 반도체 전계 효과 트랜지스터

Fig. 2. Simulated I<sub>DS</sub>-V<sub>DS</sub> characteristics of (a) Si Planar MOSFET and (b) Si SJ MOSFET. The thickness of Si epi layer and the doping concentration of pillars were 32.5  $\mu$ m and  $1 \times 10^{15}$ /cm<sup>3</sup>, respectively.

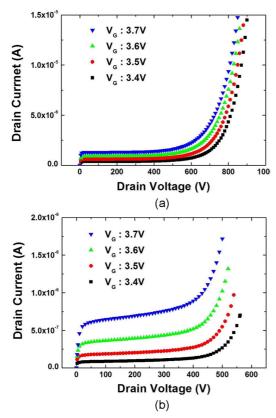

의 항복 전압 특성을 더욱 향상 시키기 위하여 실리콘 에피층의 두께와 필라의 도핑 농도를 변경하여 시뮬레 이션을 수행하였다. Fig. 3(a)는 48.5 μm로 두께의 실 리콘 에피층을 이용하여 제작된 초 접합 금속-산화막 반도체 전계 효과 트랜지스터의 드레인 전류 – 드레인 전압 특성 곡선에 대한 시뮬레이션 결과이다. 실리콘 에피층의 두께가 32.5 μm인 초 접합 금속-산화막 반도 체 전계 효과 트랜지스터 (Fig. 2(b))와 비교하여 항복 전압 특성이 향상되어 600 V 급 이상의 성능을 보이는 것을 알 수 있다. 더욱이 포화 상태의 드레인 전류도 게이트 전압이 3.5 V일 때 0.5 × 10<sup>-6</sup> A로 실리콘 에피 층 두께 증가에 따른 저항의 증가가 소자의 동작 특성 에 크게 영향을 미치지 않는 것으로 판단된다. 실리콘 에피층의 두께 증가로 인하여 항복 전압 특성이 향상 되는 원인은 소스로부터 드레인까지 캐리어가 이동하 는 거리가 길어지기 때문이다. 그러나, 실리콘 에피층

Fig. 3. Simulated  $I_{DS}$ - $V_{DS}$  characteristics of Si SJ MO-SFET with (a) the Si epi thickness of 48.5  $\mu$ m and (b) p-/n-pillar concentration of  $1\times10^{14}$ /cm<sup>3</sup>.

두께를 증가시킨 구조는 공정 시간이 증가되고, 이온 주입 공정이 추가되기 때문에 열처리 공정 중 p-필라 와 n-필라영역에 존재하는 도판들의 상호 확산으로 인 하여 최적화 된 전하 균형을 구현하기가 매우 어렵다 는 단점이 있다. 실리콘 에피층 두께 증가로 인해 수반 될 수 있는 문제점을 해결하기 위해서 p-필라와 n-필라 의 농도를 1×10<sup>14</sup>/cm<sup>3</sup> 로 감소시킨 후 시뮬레이션 하 였다. Fig. 3(b)은 이에 대한 드레인 전류 - 드레인 전 압 특성 곡선 시뮬레이션 결과로 p-필라와 n-필라의 농 도가 1 × 10<sup>15</sup> /cm<sup>3</sup>인 Fig. 2(b)보다 증가된 항복 전압 (402~480 V)이 나타남을 알 수 있지만 실리콘 에피층 의 두께를 증가시킨 구조보다는 낮은 항복 전압을 나 타내었다. 즉, 항복 전압 특성 향상 측면에서 필라의 도핑 농도를 감소시키는 것 보다는 에피 두께를 증가 시키는 것이 훨씬 효과적이다. 또한, 게이트 전압이 3.5 V일 때 포화 상태의 드레인 전류는 1.8×10<sup>-7</sup> A로 급격히 낮아진 것을 관찰 할 수 있으며, 이는 필라 도

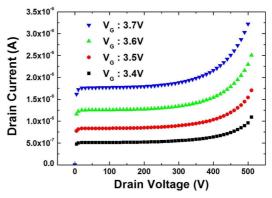

Fig. 4. Simulated  $I_{DS}$ - $V_{DS}$  characteristics of  $Si_{0.9}Ge_{0.1}$  SJ MOSFET.

핑 농도 감소에 의해 저항이 증가하여 소자에 흐르는 전류의 흐름이 억제되었기 때문이다. 따라서, 필라의 도핑 농도를 감소시킬 경우, 어느 정도의 항복 전압 향 상이 가능하지만, 입력 대비 출력 특성이 매우 낮아져 전력 소자 적용에 부적절한 것으로 판단된다.

Fig. 3의 결과에서 볼 수 있듯이 구조를 변경하여 실 리콘 초 접합 금속-산화막 반도체 전계 효과 트랜지스 터의 특성을 향상시키는 것은 제한적이다. 이는 채널 재료로 사용된 실리콘의 물성 한계에 기인한다. 따라서 실리콘 대신 물성이 우수한 실리콘-게르마늄 화합물 반 도체 재료를 사용하여 초 접합 금속-산화막 반도체 전 계 효과 트랜지스터 특성을 시뮬레이션 하였다. Fig. 4 는 게르마늄 함량이 10% 인 실리콘-게르마늄 에피 층 을 이용한 초 접합 금속-산화막 반도체 전계 효과 트랜 지스터의 드레인 전류 - 드레인 전압 특성 곡선에 대 한 시뮬레이션 결과이다. 동일한 도핑농도와 두께를 갖 는 실리콘 에피 층을 이용하여 제작된 초 접합 금속-산 화막 반도체 전계 효과 트랜지스터와 비교하여 항복 전압 특성이 향상됨과 동시에 포화 상태의 드레인 전 류가 증가된 것을 알 수 있다. 이는 실리콘-게르마늄 화합물 이 실리콘보다 밴드갭이 작기 때문에, 동일한 턴-온 전압에서 캐리어들이 P/N 접합 장벽을 쉽게 넘 어갈 수 있게 되기 때문이다[14-15]. 물론 게르마늄 함 량을 더욱 증가시켜 추가적인 포화 드레인 전류 특성 향상이 가능하지만, 게르마늄 함량이 지나치게 높을 경 우, p-바디의 채널층 밴드가 휘어짐이 커지게 되어 포 화 상태 영역이 사라지게 되고 결국에는 실리콘 평면 금속-산화막 반도체 전계 효과 트랜지스터처럼 항복 전압이 크게 감소하는 현상이 나타나게 된다. 더욱이, 실제 실리콘-게르마늄 에피 공정에 있어 게르마늄 함 량이 증가함에 따라 실리콘과의 격자상수 차이가 커지

게 되고, 이로 인하여 많은 양의 결정 결함이 자발적으 로 형성되어, 다량의 누설전류가 발생하는 문제점이 발 생할 수 있다[16]. 따라서 본 시뮬레이션 결과를 바탕 으로 고품질의 실리콘-게르마늄 에피 공정 최적화를 통해 고성능의 초 접합 금속-산화막 반도체 전계 효과 트랜지스터 구현이 가능할 것으로 예측된다.

#### 4. 결

본 논문에서는 SILVACO TCAD 시뮬레이션을 이용 하여 실리콘 평면 금속-산화막 반도체 전계 효과 트랜 지스터, 실리콘 초 접합 금속-산화막 반도체 전계 효과 트랜지스터, 실리콘-게르마늄 초 접합 금속-산화막 반 도체 전계 효과 트랜지스터의 소자 특성을 연구하였다. 실리콘 초 접합 금속-산화막 반도체 전계 효과 트랜지 스터의 경우, 필라에 의해 드레인 전압 인가에 따른 공 핍층 확장이 억제되어 실리콘 평면 금속-산화막 반도 체 전계 효과 트랜지스터 보다 높은 항복 전압 특성이 나타남을 알 수 있었다. 반면 실리콘 평면 금속-산화막 반도체 전계 효과 트랜지스터의 경우, 펀치-스루 현상 에 의해 낮은 드레인 전압에도 누설 전류의 양이 증가 하여 항복 전압이 급격히 감소함을 관찰하였다. 초 접 합 금속-산화막 반도체 전계 효과 트랜지스터의 항복 전압 특성을 향상시키는 관점에서 필라의 도핑농도를 감소시키는 것 보다는 실리콘 에피 층의 두께를 증가 시키는 것이 보다 효과적이었다. 이는 저농도의 필라를 적용할 경우, 소자의 저항이 증가하여 전류의 흐름을 억제하기 때문이다. 반면 실리콘 에피 대신 실리콘-게 르마늄 에피를 적용한 초 접합 금속-산화막 반도체 전 계 효과 트랜지스터의 경우, 동일 구조의 실리콘 초 접 합 금속-산화막 반도체 전계 효과 트랜지스 터보다 항 복 전압과 포화 상태의 드레인 전류가 동시에 증가되 었으며, 이는 실리콘-게르마늄의 밴드갭이 실리콘보다 작기 때문에 빌트-인 장벽 높이가 낮아져 캐리어들이 보다 쉽게 이동할 수 있기 때문으로 판단된다. 즉, 우 수한 물성을 갖는 실리콘-게르마늄 화합물 반도체를 이용하여 초 접합 금속-산화막 반도체 전계 효과 트랜 지스터를 제작 할 경우, 기존의 실리콘 초 접합 금속-산화막 반도체 전계 효과 트랜지스터보다 향상된 동작 특성을 갖는 소자를 구현 할 수 있다.

#### 참고문헌

1. Eun Sik Jung, Sin Su Kyoung and Ey Goo Kang, "Design and Fabrication of Super Junction MOSFET

- Based on Trench Filling and Bottom Implantation Process", J. Electr. Eng. Technol., 9(3), pp.964-969, (2014).

- 2. H. W. Lee, E. S. Jung, R. Oh, and M. Y. Sung, "Study on Design of 60V TDMOSFET for protection circuit Module", J. of KIEEME, 25(5), pp.340-344, (2012).

- 3. J. S. Lee, E. G. Kang and M. Y. Sung, "Improvement of electrical characteristics of vertical NPT trench gate IGBT using trench emitter electrode," J. of KIEEME, 19(10), pp.912-917, (2007).

- 4. Saeed Jahdi, Olayiwola Alatise, Roozbeh Bonyadi, Petros Alexakis, Craig A. Fisher, Jose A. Ortiz Gonzalez, Li Ran and Philip Mawby, "An Analysis of the Switching Perfoemance and Robustness of Power MOSFETs Body Diodes: A Technology Evaluation," IEEE Trans. Power Electron., PP(99), pp.1-12, (2014).

- 5. S. S. Kyoung, J. S. Lee, S. H. Kwak, E. G. Kang and M. Y. Sung, "A Novel Trench IGBT with a Deep P+ Layer beneath the Trench Emitter", IEEE Trans. Electron Devices, 30(1), pp.82-84, (2009).

- 6. Wei Wu, Bo Zhang, Xiaorong Luo, Zhaoji Li, "Low specific on-resistance power MOSFET with a surface improved super-junction layer", Superlattices Microstruct., 72(1-10), (2014).

- 7. R. J. P. Lander, C. J. Emeleus, B. M. McGregor, E. H. C. Parker, T. E. Whall, A. G. R. Evans and G. P. Kennedy, "Study of Hall and effective mobilities in pseudomorphic Si<sub>1-x</sub>Ge<sub>x</sub> p-channel metal-oxide-semiconductor field-effect transistors at room temperature and 4.2K," J. Appl. Phys., 82(10), pp.1424-1426, (2001).

- 8. C. W. Leitz, M. T. Currie, M. L. Lee, Z.-Y. Cheng, D. A. Antoniadis and E. A. Fitzgerald, "Hole mobility enhancements and alloy scattering-limited mobility in tensile strained Si/SiGe surface channel metaloxide-semiconductor field-effect transistors", J. Appl. Phys., 92(7), pp.3745-3751, (2014).

- 9. M. J. Palmer, G. Braitwaite, T. J. Grasby, P. J. Phillips, M. J. Prest, E. H. C. Parker, T. E. Whall, C. P. Parry, A. M. Waite, A. G. R. Evans, S. Roy, J. R. Watling, S. Kaya and A. Asenov, "Effective mobilities in pseudomorphic Si/SiGe/Si p-channel metaloxide-semiconductor field-effect transistors with thin silicon capping layers", Appl. Phys. Lett., 78(10), pp.1424-1426, (2001).

- 10. Adel S. Sedra and Kenneth C. Smith, Microelectronics CIRCUITS, FIFTH EDITION, pp.254-255, (2004).

- 11. Jung Yong Lee, "Avalanche Phenomenon at The Ultra Shallow N+-P Silicon Junctions", J. of KSDT., 6(3), pp.47-53, (2007).

- 12. Elizabeth Kho Ching Tee, Marina Anrina, Florin

- Udrea, Alexander Hoelke, Liang Yew Ng, Wan Azlan Bin Wan Zainal Abidin, Steven John Pilkington and Deb Kumar Pale, "Analysis on the off-state design and characterization of LIGBTs in partial SOI technology", *Solid-State Electron.*, 96, pp.38-43, (2014).

- 13. Rene P. Zingg, "On the specific On-Resistance of High-Voltage and Power Devices", *IEEE Trans. Electron Devices*, 51(3), pp.99-102, (2001).

- 14. T. E. Whall and E. H. C. Parker, "SiGeheterostructures for CMOS technology", *Thin Solid Films*, 367(1-2), pp.250-259, (2000).

- 15. Shekhar Srivastava, Lalit Maurya and Vijay Kr Sri-

- vastava, "Comparative Study of SiGe MOSFET with Single Substrate MOSFET Using Visual TCAD", *International J. of Emerging Trends in Science and Technology*, 01(04), pp.527-531, (2014).

- 16. M. Oehme, J. Werner, O. Kirfel, and E. Kasper, "MBE growth of SiGe with high Ge content for optical applications", *Appl. Surf. Sci.*, 254()19, pp.6238-6241, (2008).

접수일: 2014년 9월 2일, 심사일: 2014년 9월 10일,

게재확정일: 2014년 9월 22일