http://dx.doi.org/10.6113/TKPE.2013.18.1.110

# 보상전압 첨가를 통한 B4 인버터 성능향상

이동명<sup>†</sup>

Performance Improvement of B4 Inverters by Adding Compensation Voltage

Dong-Myung Lee<sup>†</sup>

**Abstract** - This paper proposes a current ripple reduction method to improve the control performance of B4 type inverter that is studied for cost-effective drive systems. B4 inverters employ only four switches and they have a center-tapped connection between the split dc-link capacitors and one phase of a three-phase motor or load. In the B4 topology, unbalanced three-phase voltages will be generated due to the dc-link voltage ripple. To solve this problem, this paper presents a voltage distortion compensation method that adjusts the voltage reference with the consideration of dc-link voltage ripple. The validity of the proposed method is verified by simulation and excremental results with an induction machine.

Keywords: B4 inverters, voltage ripple, split dc-link capacitor, ripple compensation

#### 1. 서 론

최근 전력전자 기술의 발달과 에너지 절감 및 제어성능 향상에 대한 요구의 증가로 가변속 인버터 시스템의 적용이 확대되고 있다. 이러한 가변속을 위한 인버터시스템의 적용은 시스템의 성능 향상이라는 장점은 있으나, 제품 가격의 상승을 가져와 저가격화를 위한 연구가 활발히 진행 중이다. 저가격화를 위한 하나의 방법으로 4개의 스위치를 사용하여 3상 전동기의 속도 제어하는 방식이 소개되었다<sup>[1]</sup>. 이하, 본 논문에서는 이러한방식의 인버터를 B4인버터라 칭한다.

B4 인버터는 3상 전동기의 한 상이 DC 링크 커패시터의 중성점에 연결된 구조이며, B4 방식을 사용하여 3상 평형 전압의 발생을 위한 스위칭 기법은 여러 논문을 통해 소개되었다<sup>[2]-[3]</sup>. 이러한 B4 인버터는 스위칭 소자수의 저감에 따른 장점은 있으나, 상하로 분리된 DC 링크단을 가짐으로 인해서 상하 DC 링크단 전압차에의해 발생전압의 왜곡이 발생하는 고유의 문제점을 가지고 있으며, 이를 해결하기 위한 여러 기법이 발표되고 있다<sup>[4]-[7]</sup>

DC 링크단 전압 변동에 따른 전압 왜곡 현상을 보상

하기 위하여, [4]에서는 B4 인버터의 스위칭 시간 계산을 직접 검출된 DC 링크단 전압을 이용하는 방식을 제안하였으며, [6]에서는 DC 링크단 중성점에 흐르는 전류검출을 통하여, 출력전압의 왜곡을 보상하였다. [7]에서는 B4 인버터에서 발생하는 DC 링크단의 불평형 현상의 원인과 결과를 자세히 분석하였다.

최근에 B4 인버터는 유도전동기에 대한 적용뿐만 아니라 영구자석전동기에 적용하는 연구도 활발히 진행되고 있다<sup>[8-10]</sup>. 또한 B4 인버터는 저가격회로에 대한 적용뿐만 아니라, 인버터 고장시의 비상운전 등을 위한 수단으로 연구되고 있다<sup>[11]</sup>. 이와 더불어, 전동기제어분야 뿐만 아니라 신재생 에너지, 전력품질 보상기와 같은 분야로의 적용이 시도되고 있다<sup>[12]</sup>. 따라서 적용이 확대되고 있는 B4 인버터의 제어성능향상 특히 분리된 DC 링크단 커패시터에 기인하는 전압 변동을 보상하는 연구가필요하다고 하겠다.

기존의 왜곡 보상기법은 순시치 DC 링크단 전압을 이용하여 스위칭 시간을 계산한다던가, 전류 정보를 이용하여 출력전압의 왜곡을 보상하고 있어, 추가적인 회로 및 정밀한 전압검출이 필요하다. 따라서, 본 논문에서는 DC 링크단의 전압차이를 고려하여 보상 시간을 결정하는 저자가 발표한 [5]의 기법을 보완하여 보다 간단한 B4 인버터 성능개선 방법을 제안하고자 한다.

삼상 인버터의 공간전압 PWM (SVPWM) 발생시 최근에는 옵셋 첨가와 같은 방식으로 기존의 SVPWM에서 영역을 구별하는 등의 연산을 거치지 않고 PWM 시

School of Electronic and Electrical Eng., Hongik Univ. Tel: +82-2-320-3047 Fax: +82-2-320-1193 Manuscript received Oct. 5, 2012; accepted Jan. 15, 2013

Paper number: TKPE-2013-18-1-13 ISSN: 1229-2214

<sup>+</sup> Corresponding author: dmlee@hongik.ac.kr,

간의 결정이 이루어지고 있다. 따라서 이러한 PWM 방식의 추세를 따라 본 논문에서는 보상 전압을 인가하는 방식으로 B4 인버터의 전압왜곡 현상에 따른 전류 리플발생 현상을 저감하고자 한다. 2장과 3장에서 전압왜곡현상을 분석하고, 보상 전압의 크기 결정 방법 및 제안한 알고리즘에 대해 설명하며, 4장에서는 유도전동기를대상으로 모의실험 및 실험을 통하여 제안된 기법의 타당성을 보인다.

#### 2. B4 인버터

## 2.1 B4 인버터의 구조와 동작원리

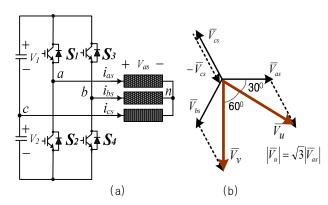

스위칭 소자 6개를 사용하는 B6 인버터는 각각의 레그가 전동기 각상에 연결된 구조이다. 이에 비해 B4 인버터는 그림 1(a)와 같이 전동기의 한상이 상하로 분리된 DC 링크단 커패시터의 중간단에 연결되고 나머지두상은 인버터의 레그에 연결된 구조이다.

B4 인버터는 4개의 스위치를 이용하여 2개의 전압 벡터를 생성한다. 이 두개의 전압은 3상 평형전압을 발생하기 위하여 DC 링크 중성점에 연결된 상에 역상의 전압을 인가하는 방식으로 전압을 생성시킨다. 이렇게 발생된 두 전압 ( $V_{u_r}$ ,  $V_{v_r}$ )은 평형 3상 전압과 영상분 전압을 가진 형태가 되어 3상 전동기의 제어가 가능하다 $^{[1]}$ .

그림 1(b)는 B4 인버터의 u, v 레그에 대한 폴 전압의 페이저이다. 그림 1(a)와 같이 전동기의 c상이 DC 링크 단의 중성점에 연결된 경우이다. 이 경우 B4 인버터에서 생성한  $V_{u}$ ,  $V_{c}$ 전압은 정상분 전압과  $-V_{c}$ 에 해당하는 영상분 전압을 전동기 혹은 부하 a, b상에 각각 인가한형태를 가진다. 한편, 논문에서 제시된 분석 및 실험 등의 조건은 모두 전동기의 c상이 DC 링크 중간단에 연결된 구조 즉, 그림 1(a)의 형태를 기준으로 한다. 삼상평형 전압을 얻기 위한 2개의 전압 벡터,  $V_{u}$ ,  $V_{c}$ 는 식(1)과 같이 나타낼 수 있으며,  $V_{u}$ ,  $V_{c}$ 의 위상차는 60도이다.  $T_{u}$ 와  $T_{c}$ 는 각각  $V_{u}$ ,  $V_{c}$ 를 생성하기 위한 스위칭 시간이다. 여기서,  $m_{e}$ 는 변조율,  $T_{c}$ 는 샘플링 시간이다.

Fig. 1 B4 inverters (a) configuration and (b) phase diagram corresponding to the configuration shown in (a)

Table 1 Phase voltages corresponding to each mode

| mo<br>de | S<br>1 | S<br>3 | $V_{as}$                                       | $V_{bs}$                               | $V_{cs}$                             |

|----------|--------|--------|------------------------------------------------|----------------------------------------|--------------------------------------|

| 1        | 0      | 0      | $-\frac{1}{3}V_2$                              | $-\frac{1}{3}V_2$                      | $\frac{2}{3}V_2$                     |

| 2        | 0      | 1      | $\Bigg  -\frac{1}{3} \big( 2 V_2 +  V_1 \big)$ | $\frac{1}{3} \big( 2 V_1 +  V_2 \big)$ | $\frac{1}{3} \big( V_2 -  V_1 \big)$ |

| 3        | 1      | 0      | $\frac{1}{3}\big(2V_1+V_2\big)$                | $-\frac{1}{3}\big(2V_2+V_1\big)$       | $\frac{1}{3}\big(V_2-V_1\big)$       |

| 4        | 1      | 1      | $\frac{1}{3}V_1$                               | $\frac{1}{3}V_1$                       | $-\frac{2}{3}V_1$                    |

$$\begin{split} V_{u} &= \frac{1}{2} \left( 1 + m_{a} \sin \left( \theta - \frac{\pi}{6} \right) \right) V_{dc} \\ V_{v} &= \frac{1}{2} \left( 1 + m_{a} \sin \left( \theta - \frac{\pi}{2} \right) \right) V_{dc} \\ \Rightarrow & \\ T_{u} &= \frac{1}{2} \left( 1 + m_{a} \sin \left( \theta - \frac{\pi}{6} \right) \right) T_{s} \\ T_{v} &= \frac{1}{2} \left( 1 + m_{a} \sin \left( \theta - \frac{\pi}{2} \right) \right) T_{s} \end{split} \tag{1}$$

스위칭 모드에 따라 상하단 커페시터 중 하나의 커페시터만이 부하와의 전력전달에 관여하는 현상이 발생한다. 표 1에 나타난 4가지 전압 중 모드 1, 스위칭 상태(0,0)은 그림 1에서  $S_2$ ,  $S_4$ 가 온이 되는 경우로 하단 커페시터만이 전동기와의 전력 전달에 관여하고 있다. 이에 비하여  $S_1$ 과  $S_3$ 과 온이 되는 모드 4(1,1)에서는 상단커페시터만이 전력 전달에 관여함을 알 수 있다. 따라서 B4 인버터의 경우 모드에 따라 전력전달에 관여하는 커페시터가 달라짐으로 인해, 상하단 커페시터의 전압  $V_1$ 과  $V_2$ 에 전압 리플이 발생함을 알 수 있다.

#### 2.2 전압왜곡 현상

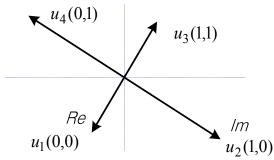

해석의 간편화를 위하여  $u_I(0,0)$ 을 실수축으로 하여 4개의 전압을 나타내면 그림 2와 같이 나타낼 수 있다. 전압의 실수축 성분 및 허수축 성분은 표 2와 같이 나타난다. 그림 2는  $V_I$ 과  $V_2$ 의 전압이 동일한 이상적인 경우의 전압 벡터도이다. 즉,  $V_I$ = $V_2$ 인 경우 4개의 전압 벡터는 직교한다.

| Table 2 | Magnitude of voltage components in real and  |

|---------|----------------------------------------------|

|         | imaginary axis corresponding to each voltage |

|         | vector                                       |

| mo<br>de | $S_{I}$ | S3 | Vec<br>tor | Re.                            | Im.                                    |

|----------|---------|----|------------|--------------------------------|----------------------------------------|

| 1        | 0       | 0  | $u_1$      | $V_2$                          | 0                                      |

| 2        | 0       | 1  | $u_4$      | $\frac{1}{2}\big(V_2-V_1\big)$ | $-\frac{\sqrt{3}}{2}\big(V_1+V_2\big)$ |

| 3        | 1       | 0  | $u_2$      | $\frac{1}{2}\big(V_2-V_1\big)$ | $\frac{\sqrt{3}}{2}\big(V_1+V_2\big)$  |

| 4        | 1       | 1  | $u_3$      | $-V_1$                         | 0                                      |

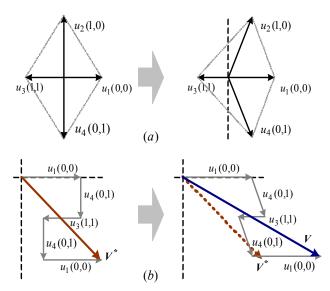

B4 인버터의 전압왜곡 현상은 다음과 같이 설명할 수있다.  $V_2=V_1$ 일 때 직교하던 4개의 전압벡터는  $V_2>V_1$ 인경우 그림 3(a)과 같이 오른쪽으로 기울어진 전압벡터가 된다.  $V_2$ 와  $V_1$ 이 동일한 경우 실수축 성분 (Real)이영이 되어  $u_1$  또는  $u_3$ 에 직교하던  $u_4$  전압벡터가  $V_2$ 가  $V_1$ 보다 크면 표 2에서 알 수 있듯이 실수부 성분으로

Fig. 2 Four effective voltage vectors of B4 inverter aligned  $u_l$  on the real axis

Fig. 3 Reference voltage  $(V^*)$  and the developed voltage (V) affected by the voltage difference in upper and lower dc-link

$(V_2 - V_1)/2$ 로 나타나는 값이 양의 크기를 갖게 되어 오른쪽으로 기울어진 전압벡터가 된다. 또한  $u_1(0,0)$ 이  $u_3(1,1)$ 에 비해 커지게 된다.

상하 DC 링크단의 전압차가 존재하는 경우 제어기에서 지령치 전압을 생성하기 위한  $S_1$ 의 스위칭 시간,  $S_3$ 의 스위칭 시간을 식 (1)에 따라 그대로 인가하면 상하단 DC 링크단의 전압차에 의한 왜곡된 전압발생으로 의해서 그림 3(b)와 같이 지령치 전압과 발생전압에는 오차가 발생하게 된다. 반대의 경우인,  $V_1 \!\!\!> \!\!\!\!> \!\!\!\!V_2$ 인 경우에는  $u_2$ ,  $u_4$ 가 좌측으로 치우치고,  $u_3 \!\!\!> \!\!\!\!> \!\!\!\!u_I$ 이 되므로 원하는 지령치 전압보다 좌측으로 기울어지고 전압의 크기 또한 커진 왜곡된 전압을 발생한다. 한편, 전압 왜곡양은  $\Delta V(V_2-V_1)$  크기에 비례한다.

### 3. 제안하는 전압왜곡 보상 기법

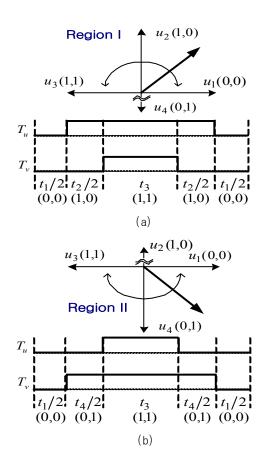

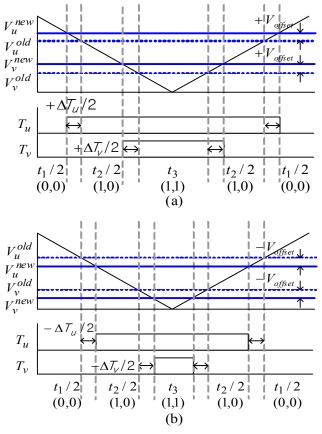

그림 3에서 설명한 것과 같이  $V_{\mathcal{D}}V_{\mathcal{I}}$ 인 경우 사인 (Sinusoidal) PWM에 의해 계산된  $T_{u}$ ,  $T_{v}$ 를 보상 없이 그대로 인가한 경우,  $t_{\mathcal{I}}$ 시간동안 인가된  $u_{\mathcal{I}}$ 전압의 크기가 커짐으로 인해 실제적인  $u_{\mathcal{I}}$ 전압의 인가시간이 증가되고, 이에 비해  $u_{\mathcal{I}}$ 건압은 작게 인가된 결과가 된다. 따라서, 전압의 왜곡을 감소시키기 위하여 계산된  $u_{\mathcal{I}}$ 의 인가시간  $t_{\mathcal{I}}$ 은 감소시키고,  $u_{\mathcal{I}}$ 의 인가시간  $t_{\mathcal{I}}$ 는 증가시켜야 한다. 그림 4는 Center aligned PWM의 영역에 따른 온 시간을 나타낸다. 우선 그림 4로 부터 지령치 전압의 위치는 크게 두 영역  $I_{\mathcal{I}}$ 과 영역  $I_{\mathcal{I}}$ 으로 나눌 수 있음을 볼 수 있다.

영역 I은  $T_u > T_v$ 인 구간이고, 영역 II는  $T_u < T_v$ 인 영역이다. 제안하는 방식의 전압왜곡 보상 기법은 식 (1)에의해 계산된 전압 지령치에 보상전압 ( $V_{offset}$ )을 첨가해주는 아래의 식의 형태로 나타난다.

$$V_{nEw}^* = V_{old}^* + V_{offset} \tag{2}$$

식 (2)의  $V_{offset}$  첨가에 따른 효과를 설명하기 위하여이에 앞서 그림 4를 이용하여, 전압벡터 인가시간에 따른 왜곡현상 보상에 대한 설명을 한다. 영역 I에 전압벡터가 존재하는 경우 전압왜곡 보상은 아래와 같이 시행되어야 한다. 우선 샘플링 시간을  $T_s$ 라 할 때  $V_{>}$   $V_{1}$ 인 경우 그림 3(b)와 같이 지령치 전압벡터에 비하여 인가시간을 변경하지 않고 전압벡터를 인가한 경우 실제발생 전압벡터는 우측으로 치우치게 된다. 따라서 이를보상하기 위해서는  $U_{3}$ 벡터의 인가시간인  $t_{3}$ 은 증가시키고,  $U_{1}$ 벡터의 인가시간인  $t_{5}$ 는 감소시켜야 한다. 이 경우그림 4(a)의 영역 I에서  $t_{3}$  증가,  $t_{1}$ 의 감소는  $T_{u}$ 와  $T_{v}$ 의 증가임을 알 수 있다. 한편,  $V_{1}$ >  $V_{2}$ 인 경우는 반대 경우이므로 전압왜곡을 감소하기 위해서는  $t_{3}$ 는 감소,  $t_{1}$ 는 증가시켜야 하며, 이는  $T_{v}$ 와  $T_{u}$ 를 감소시키는 조건과 일

치하게 된다.

영역  $\Pi$  구간에서의 전압 왜곡 보상에 대해서 알아보면 다음과 같다.  $V > V_I$ 인 경우  $u_i$ 전압은 영역 I에서와 마찬가지로 우측으로 기울어져 있으므로,  $t_I$ 의 인가시간은 줄이고  $t_3$ 의 인가시간은 증가시켜야 한다. 이 조건은  $T_{u_i}$   $T_{v_i}$ 의 증가를 의미한다. 따라서, 지령치 전압 벡터가 존재하는 영역에 관계없이  $V > V_I$ 인 경우에는  $T_u$ 와  $T_v$ 는 증가하여야 하고, 이와 반대의 경우인  $V_i > V_2$ 인 경우  $T_v$ 와  $T_v$ 를 감소시켜야 한다.

본 논문에서 제안하는 방식은 식 (2)에서와 같이 지령치 전압벡터에 보상 전압량 즉,  $V_{offset}$ 을 인가하여 전압 외곡현상을 보상한다. 따라서 보상전압  $V_{offset}$ 에 인가에 따른 전압벡터의 인가시간  $(t_l,\ t_l,\ t_l)$ 의 변화는 옵셋전압 인가시의  $T_{ll}$ ,  $T_{ll}$ 의 변화를 도식화한 그림 5를 통해서 알 수 있다.

앞서 그림 4에서 보았듯이  $V_2 \gt V_1$ 인 경우에  $T_u$ 와  $T_v$ 를 증가시켜  $u_1$ 벡터의 인가시간인  $t_3$ 은 감소시키고,  $u_3$ 벡터의 인가시간인  $t_3$ 는 증가시켰다.  $V_{offset}$ 을 통하여 이를 구현하기 위해서는 양의 옵셋 전압이 인가되는 형태가 되어야 한다.

Fig. 4 Regions [(a)-I, (b)-II] and corresponding  $T_u$  and  $T_v$

$T_u$ 와  $T_v$ 가 감소함을 알 수 있다. 그림 5는  $T_u$ > $T_v$ 인 영역 I에 대한 옵셋 전압에 따른 스위칭 시간의 변화에 대해 나타내고 있으나, 그림 4에서 알 수 있듯이 지령치전압이 위치한 영역에 관계없이  $V_{>>}V_v$ 인 경우는 각 레그 인버터의 상단 스위치의 인가시간의 증가, 반대의 경우에는 상단스위치의 인가시간 감소가 이루어지면 되므로, 영역 II와 같은  $T_u$ < $T_v$ 인 경우에서도 양의 옵셋 전압인가시  $T_u$ ,  $T_v$  증가, 음의 옵셋 전압 인가시  $T_u$ ,  $T_v$  증가, 음의 옵셋 전압 인가시  $T_u$ ,  $T_v$  감소됨을 그림 5를 통해 미루어 짐작할 수 있으므로, 옵셋 전압 인가를 통해 지령치 전압과 실제 발생 전압의 왜곡 현상을 감소시킬 수 있음을 알 수 있다. 한편,  $V_{>>}V_v$ 인 경우에는 양의 옵셋 전압, 반대의 경우에는 음의 옵셋 전압을 더해주어야 하므로 옵셋 전압의 형태는 다음의 식을 나타난다.

$$V_{offset} = k(V_2 - V_1) \tag{3}$$

한편, 식 (3)의 K값은 옵셋 전압의 크기를 결정하기위한 값으로, 상하단 DC 링크단의 전압차가 존재하는 경우에 발생한 전압을 이상적인 경우와 동일하게 하도록 옵셋 전압  $(V_{offset})$ 을 조정하여 구할 수 있다. 이상적인 전압 상태에서의  $u_I-u_I$  전압벡터는 표 2로부터, 아래와 같이 표시할 수 있다.

Fig. 5 Changement of  $t_1$ ,  $t_3$  with variation of offset voltage by (a) positive and (b) negative values

$$\begin{aligned} \mathbf{u_1} &= V_2 = \frac{1}{2} V_{dc} \\ \mathbf{u_2} &= j \frac{\sqrt{3}}{2} V_{dc} \\ \mathbf{u_3} &= -V_1 = -\frac{1}{2} V_{dc} \\ \mathbf{u_4} &= -j \frac{\sqrt{3}}{2} V_{dc} \end{aligned} \tag{4}$$

이에 비하여  $V_2 > V_1$ 인 경우를 예로 하여 표 2를 참고하여 각 벡터를 표시하면 식 (5)와 같이 나타낼 수 있다. 여기서,  $V_{dc} = V_1 + V_2$ ,  $\Delta V = V_2 - V_1$ 이다.

$$\mathbf{u_{1}} = \frac{1}{2} V_{dc} + \frac{1}{2} \Delta V

\mathbf{u_{2}} = \frac{1}{2} \Delta V + j \frac{\sqrt{3}}{2} V_{dc}

\mathbf{u_{3}} = -\frac{1}{2} V_{dc} + \frac{1}{2} \Delta V

\mathbf{u_{4}} = \frac{1}{2} \Delta V - j \frac{\sqrt{3}}{2} V_{dc}$$

(5)

그림 5(a)의 경우를 통해 설명하며, 이때 전압 벡터는  $u_l,\ u_2,\ u_3$ 가 이용되고  $V_2 \!\!>\! V_I$ 을 인해서 양의 옵셋 전압을 인가하여  $\Delta T_u, \Delta T_v$ 를 생성하는 경우이다. 그림 5(a)에서 지령치 전압의 생성은 아래의 식과 같다.

$$t_1 \boldsymbol{u_1} + t_2 \boldsymbol{u_2} + t_3 \boldsymbol{u_3} = \boldsymbol{V}^* T_s \tag{6}$$

식 (6)에 식 (4)를 대입하여 정리하면 이상적인 경우 아래의 식이 성립한다.

$$\frac{1}{2} V_{dc} t_1 + j \frac{\sqrt{3}}{2} V_{dc} t_2 + t_3 (-V_1) = \mathbf{V}^* T_s$$

(7)

식 (7)과 동일한 방법으로 식 (6)에 식 (5)로 표시된  $V_{2} > V_{1}$ 인 경우의 각 전압 벡터의 수식을 대입 정리한 후식 (6)의  $\textbf{V}^{*}T_{s}$ 를 대치하여 정리하면 식 (8)을 얻을 수있다. 여기서, 전압왜곡을 보상하기 위해서 인가하는 옵셋 전압은  $V_{u}$  및  $V_{v}$ 에 동일한 크기로 인가되므로  $\Delta T_{u} = \Delta T_{v} = \Delta T$ 의 관계를 가진다.

$$\Delta T = \frac{\frac{1}{2}\Delta V}{V_{dc} + \frac{1}{2}\Delta V} \cdot T_s \simeq \frac{\frac{1}{2}\Delta V}{V_{dc}} \cdot T_s$$

(8)

$\Delta T/T_s = V_{offset}/V_{dc}$ 의 관계식이 성립하므로 식 (8)로부터 아래의 식 (9)을 구할 수 있다. 한편, 식 (9)에서  $\Delta V/V_{dc}$ 를 10%로 설정하면,  $V_{offset}$ 는  $\Delta V/2$ 보다약간 작은 값임을 알 수 있으며, 실험 및 시뮬레이션에

서는  $\frac{\Delta V}{2.2} = \frac{V_2 - V_1}{2.2}$  으로 설정하였다. 즉, 실험 및 시 뮬레이션에서 k= 1/2.2로 설정하였다.

$$V_{offset} = \frac{\frac{1}{2}\Delta V}{1 + \frac{1}{2}\Delta V/V_{dc}} \cong \frac{1}{2}\Delta V$$

(9)

## 4. 시뮬레이션 및 실험 결과

## 4.1 시뮬레이션 블록 및 시뮬레이션 결과

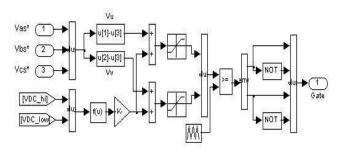

제안된 방법의 타당성을 검증하기 위하여 Simulink를 사용하여 시뮬레이션 하였다. 그림 6은 전체 시뮬레이션 블록 중 전압 지령치를 생성하는 부분이다. 시뮬레이션 에서는  $V_{u}$ ,  $V_{v}$ 는 식 (1)로 부터 구할 수 있으나,  $-V_{c}$ 를 인가하는 것으로 생각하여 인가 전압식은 아래의 식을 통해 구하였다.

$$V_u = V_{as} - V_{cs}, \quad V_v = V_{bs} - V_{cs}$$

(10)

그림 6과 같이 원지령치  $V_{U_s}$   $V_{V}$ 에  $K(V_{Z^*}V_I)$ 의  $V_{offset}$ 전 압이 더해져서 최종 지령치 전압이 생성되며, 이 최종치 전압이 반송파와 비교되어 게이트 신호가 발생된다.

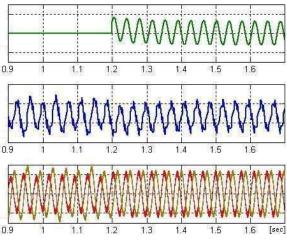

그림 6은 t=1.2초에 제안된 보상기법을 적용한 경우의 시뮬레이션 파형을 보여준다. 위로부터  $V_{othert}$ , 상단 커패시터 전압  $(V_I)$ 과 b상과 c상의 상전류  $(i_{bs}, i_{cs})$ 를 나타낸다. 보상 전후를 결과 파형을 비교해 보면, 식 (2)와 (3)에 의해 결정된 보상전압을 인가함으로 인해서 DC 링크단의 전압 리플의 형상이 규칙적인 형상을 가지게 되었음을 알 수 있으며, 상전류의 리플이 제안한 기법을통해 제거되어 평형된 삼상 전류가 흐름을 알 수 있다.

그림 7(a), (b)는 보상전과 보상후의 시뮬레이션 파형을 각각 나타낸 것이다. 보상 전의 상전류의 편차가 b상을 100%로 했을 때 대략 130%이였던 c상전류가 그림 7(b)에 나타난 것과 같이 상전류의 크기가 동일하게 됨을 확인할 수 있었다. 한편, 보상 전 a, b, c상의 전류 THD는 각각 2.18% 2.32%, 5.36% 이였고 보상 후에는 각각 1.36%, 1.33% 1.39%로 나타나, 본 알고리즘 적용을통해서 현저히 전류 형상이 개선됨을 확인할 수 있었다.

Fig. 6 Simulation block for generating voltage reference

## 4.2 실험 결과

그림 9는 실험장치 중 하드웨어부를 보인다. 인버터

Fig. 7 Simulation waveform: from top to bottom  $V_{offset}$   $5[V/\text{div.}], V_I 10[V/\text{div.}], \text{ and } i_{bs} \& i_{cs} 2[A/\text{div.}]$

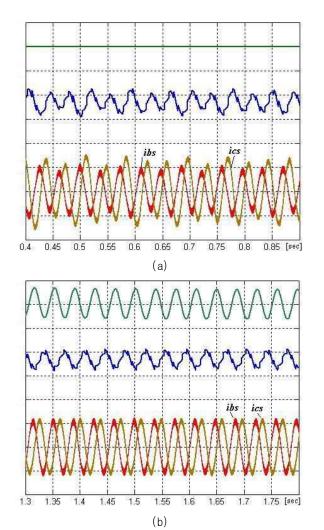

Fig. 8 Simulation results (a) without compensation and (b) with compensation: from top to bottom  $V_{offset}$   $5[V/\text{div.}], \ V_I \ 20[V/\text{div.}], \ \text{and} \ i_{bs} \ \& \ i_{cs} \ 2[\text{A/div.}]$

의 스위칭 주파수는 8 [kHz]이며 제어보드는 DSP320 F28335를 사용하였다. 상하단 커패시터 전압 측정을 위하여 전압 센서를 사용하였으며, 상하단 DC 링크단 커패시터는 각각 940 [ $\mu$ F]를 사용하였다. 4극 1마력 유도 전동기를 V/F 제어하였으며. 전동기 속도는 770 [rpm] 무부하이다. 한편, 입력 전압은 단상 220 [V]이다.

Fig. 9 Experimental setups for B4 inverters

Fig. 10 Experimental waveform (a) without compensation and (b) with the proposed compensation method: from top to bottom  $V_{offset}$  10[V/div.], upper capacitor voltage ( $V_l$ ), 30[V/div.],  $i_{bs}$  &  $i_{cs}$  1.5[A/div.]

(b)

그림 10(a)와 (b)는 각각 보상이 없는 경우와 제안한 방식을 적용한 경우의 실험 파형이다. 그림 10은 그림 8의 시뮬레이션 파형과 동일하게, 위로부터 옵셋 전압, 상단 커패시터의 전압, b와 c상의 전류 파형을 나타낸다. 그림 8의 시뮬레이션 파형과 동일하게 제안된 방식을 통한 전류 리플 보상 알고리즘 적용 이후 상전류의 크기차가 줄어들고, 전류 파형의 개선이 현저하게 나타남을 볼 수 있다. 또한 시뮬레이션과 같이  $V_1$ 의 리플도보상이후 보다 일정한 리플을 보임을 알 수 있다.

#### 5. 결 론

본 논문에서는 B4 인버터를 이용한 3상 전동기 제어기에 대하여 간단한 보상기법을 통하여 인버터의 성능향상 기법을 제안하였다. B4 인버터의 전압 왜곡 현상은 상하단 DC 링크 커패시터의 전압차에 의해 발생함을 분석하였으며, 지령치 전압에 상하단 DC 링크단 전압 오차의 크기에 비례하는 옵셋 전압을 추가하는 방식으로 지령치 전압과 실제 발생치의 오차를 저감하여 전동기 전류의 불평형을 제거하였다. 유도전동기에 적용한실험 및 시뮬레이션을 통하여, 제안한 방식의 타당성을보였으며, 제안한 방식의 적용을 통하여 저가격 가변속시스템, 인버터 고장에 따른 비상운전 수단 및 신재생에너지원을 위한 전력변환기 분야의 적용을 위해 연구가 진행되고 있는 B4 인버터의 제어 성능 향상에 기여하리라 생각된다.

이 논문은 2012년도 정부(교육과학기술부)의 재원으로 한국연구재단의 기초연구사업 지원을 받아 수행된 것임 (2010-0008884)

### 참 고 문 헌

- [1] H. van der Broeck, and J. van Wyk, "A comparative investigation of a three-phase induction machine with a component minimized voltage-fed inverter under different control options," *IEEE Trans. on Indus. Appli,*. Vol. 20, No. 2, pp. 309–320, Mar./Apr. 1984.

- [2] F. Blassbjerg, H. Kragh, D.O. Neacsu, and J.K. Pedersen, "Comparison of modulation strategies for B4-inverters," EPE, Vol. 2, pp. 378–385, 1997.

- [3] C.B. Jacobina, and B.R. Correa, "Induction motor drive system for low-power applications," *IEEE Trans. on Indus. Appli.*, Vol. 35, No. 1, pp. 52-61, Jan./Feb. 1999.

- [4] F. Blaabjerg, D.O. Neacsu, and J.K. Pederson, "Adaptive SVM to compensate dc-link voltage ripple for four-switch three-phase voltage-source inverter," *IEEE Trans. on Power Elect.*, Vol. 14, No. 4, pp. 743-752, July 1999.

- [5] D.M. LEE, J.Y. Oh, and D.H. Cheong, "A voltage compensation method to improve the control performance for B4 inverters," *Power Elect. Annual Conf.*, pp. 317–320, 2000.

- [6] J.H. Kim, J.S. Hong, and K.H. Nam, "A current distortion compensation scheme for four-switch inverters," *IEEE Trans. on Power Elect.*, Vol. 24, No. 4, pp. 1032–1040, April 2009.

- [7] R. Wang, J. Zhao, and Y. Liu, "A comprehensive investigation of four-switch three-phase voltage source inverter based on double Fourier integral analysis," *IEEE Trans. on Power Elect.*, Vol. 26, No. 10, pp. 2774–2787, Oct. 2011.

- [8] B.K. Lee, T.H. Kim, and M. Ehsani, "On the feasibility of four-switch three-phase BLDC motor drives for low cost commercial applications: topology and control," *IEEE Trans. on Power Elect.*, Vol. 18, No. 1, pp. 164– 172, Jan. 2003.

- [9] M.N. Uddin, T.S. Radwan, and M.A. Rahman, "Fuzzy-logic-controller-based cost-effective fourswitch three-phase inverter-fed IPM synchronous motor drive system," *IEEE Trans. on Industry Appli.*, Vol. 42, No. 1, pp. 21–30, Jan./Feb. 2006.

- [10] C.T. Lin, C.W. Hung, and C.W. Liu, "Position sensorless control for four-switch three-phase brushless DC motor drives," *IEEE Trans. on Power Elect.*, Vol. 23, No. 1, pp. 438–444, Jan. 2008.

- [11] B.A. Welchko, T.A. Lipo, T.M. Jahns, and S.E. Schulz, "Fault tolerant three-phase AC motor drive topologies: a comparison of features, cost, and limitations," *IEEE Trans. on Power Elect.*, Vol. 19, No. 4, pp. 1108-1116, July 2004.

- [12] H.G. Park, S.H. Jang, D.C. Lee, and H.G. Kim, "Low-cost converters for micro wind turbine systems using PMSG," *ICPE '07*, pp. 483-487, Oct. 2007.

#### 이동명(李東明)

1969년 8월 25일생. 1994년 한양대 전기공학과 졸업. 1996년 동 대학원 전기공학과졸업(석사). 2004년 조지아공대 ECE 졸업(공박). 1996년~2000년 LG전자 DA연구소주임연구원. 2004년~2006년 삼성 SDI 중앙

현구소 책임연구원. 2007년 한양대 BK21 연구교수. 2012년 Texas A&M 대학 방문교수. 2008년∼현재 홍익대 전자전기공 학부 부교수. 당 학회 편집위원.