# 마이크로스트립과 슬롯라인 천이기술을 이용한 전송선로 구현과 전력 분배기에 응용

## Transmission Line using Microstrip-Slotline Transition Technology and Its Application to Power Divider

김 영\*, 심석현\*, 윤영철\*\*

Young Kim\*, Seok-Hyun Sim\*, and Young-Chul Yoon\*\*

#### 요 약

본 논문은 마이크로스트립과 슬롯라인 천이기술을 이용한 소형 전력분배기 설계를 제안하였다. 마이크로스트립과 슬롯라인 천이기술은 전력 분배기를 구성하는  $\lambda/4$  전송선로를 멀티 레이어 구조 PCB를 이용하면 두개의  $\lambda/8$  전송선로로 작게 구현할 수 있다. 여기서는 마이크로스트립과 슬롯라인 천이 지점에서 마이크로스트립 전송선로는 via를 사용하여 단락시켰고, 슬롯라인은 스파이럴 구조를 이용하여 전송선로의 길이를 짧게 사용하였다. 이러한 마이크로스트립과 슬롯라인 천이기술의 타당성을 보기위해서 중심주파수 2 GHz 에서 동작하는 전력분배기의 마이크로스트립 선로를 천이기술을 이용한 방법으로 구현하여 그 특성을 시뮬레이션, 제작 및 측정을 하여 기존의 전력분배기와 동일한 특성을 얻었다.

#### **Abstract**

This paper presents a compact power divider using microstrip-slotline transition technology. By using the microstrip-slotline transition, the  $\lambda/4$  transmission lines of the divider can be changed to two  $\lambda/8$  transmission lines in the multilayer structure. In the microstrip-slotline transition, we have used via holes to make a short circuit at the microstrip line and embedded spiral configuration stubs to reduce the electrical length of an open circuit at the slotline end point. For validating the microstrip-slotline technique, we have simulated and implemented the power divider with embedded spiral and via hole configuration circuits at a frequency of 2 GHz. Good agreement between the simulation and the measurement results is obtained at the operating frequency.

Key words: Microstrip-slotline transition, multilayer, spiral configuration stub, power divider

#### I. 서 론

전력 분배기는 초고주파 영역의 수동소자로서 매우 중요한 역할을 수행하는데, 이것은 벡터 모듈레이

터, 고효율의 도허티 증폭기 그리고 측정 시스템의 반사율계(reflectormeter) 등에 사용되고 있다. 현대 무 선 시스템에서는 컴팩트한 소자를 이용한 작은 시스 템과 고속·대용량의 데이터를 처리하는 것을 요구하

<sup>\*</sup> 금오공과대학교 전자공학부(School of Electronic Engineering, Kumoh National Institute of Technology)

<sup>\*\*</sup> 관동대학교 전자정보통신공학부(Department of Electronics & Information Communication Eng., Kwandong University)

<sup>·</sup> 제1저자 (First Author) : 김 영(Young Kim, tel: +82-54-478-7506, email: youngk@kumoh.ac.kr)

<sup>·</sup> 접수일자 : 2013년 10월 8일 · 심사(수정)일자 : 2013년 10월 8일 (수정일자 : 2013년 12월 11일) · 게재일자 : 2013년 12월 30일 http://dx.doi.org/10.12673/jkoni.2013.17.6.687

고 있다. 이러한 요구 사항 때문에 많은 개발자들은 작은 크기의 수동소자를 개발하기 위하여 노력하고 있으며, 그것들은 병렬 캐패시터를 연결한 전송선로를 이용하는 방법[1], 단락된 병렬 결합  $\lambda/4$  전송선로를 이용하는 방법[2], 스텝 임피던스를 사용하는 방법[3], 병렬 오픈 스터브가 연결된 전송선로를 이용하는 방법[4] 그리고 캐패시터가 주기적으로 병렬 연결된 전송선를 이용하는 방법[5]등이 있다.

멀티 레이어 마이크로스트립 구조의 큰 장점은 중앙에 접지 면이 존재하고 상하 두 면 사이에 전력을 전달한다는 것이다. 마이크로스트립과 슬롯라인의천이[6]는 PCB의 한 면을 에칭한 슬롯라인은 반대편면의 마이크로스트립과 수직으로 교차한다. 이때 마이크로스트립 선로는 슬롯라인과 만나는 지점에서 1/4 만큼을 더 확장한다. 이때 슬롯라인과 마이크로스트립 선로는 마그네틱 필드에 의해서 결합된다[7]. 이러한 구성의 단점은 마이크로스트립과 슬롯라인의 1/4 전송선로를 사용하는 것으로 이것이 회로 크기를 줄이는 것을 방해한다. 또한, 마이크로스트립과슬롯라인 천이의 광대역 특성을 얻기 위해서 광대역비아[8]를 사용하는데, 이것은 비아의 크기를 크게함으로서 광대역 특성을 확보할 수 있다.

본 논문에서는 슬롯라인의 임베디드 스파이럴 스터브와 마이크로스트립 비아 홀을 이용한 마이크로 스트립을 이용한 천이구조를 제안한다. 이러한 구조는 천이를 발생하는데 필요한 구조의 크기를 작게 하는데 사용할 수 있으며, 이러한 구성의 타당성을 보이기 위하여 중심주파수 2 GHz에서 전력분배기를 제작하였고, 기존 분배기와 비교하여 동일한 전기적 특성과 기존 것과 비교하여 35%의 면적 크기를 줄였다.

#### Ⅱ. 이론과 설계

#### 2-1 마이크로스트립과 슬롯라인 천이

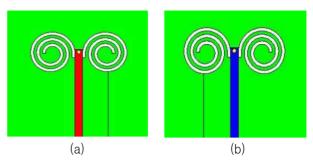

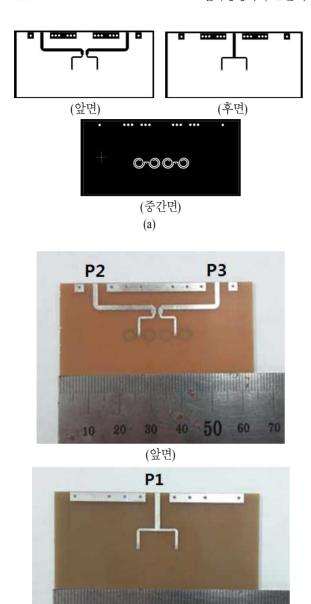

이 절에서는 비아를 이용한 단락회로의 마이크로 스트립과  $\lambda/4$  스파이럴 스터브의 슬롯라인을 이용 한 천이 구조에 대한 해석과 설계에 대해서 설명한 다. 그림 1은 스파이럴 슬롯라인과 비아를 이용한

그림 1. 스파이럴 스터브의 슬롯라인과 비아를 이용한 마이크로스트립으로 구성된 천이구조; (a) 전면 (b) 후면 Fig. 1. Microstrip-slotline transition configuration using slotline of spiral stub and microstrip of via holes; (a) front (b) rear.

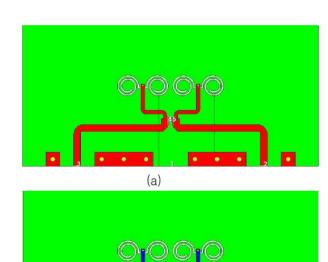

Fig. 2. Wilkinson power divider using microstrip -slotline transition configuration for simulation; (a) front (b) rear.

단락회로의 마이크로스트립을 사용한 천이구조의 전면과 후면을 나타낸 것이다. 멀티 레이어 구조를 사용한 천이의 마이크로스트립 선로는 서로 마주보는 형태로 구성되었으며, 중간 그라운드면의 반대편에 존재한다. 중간의 그라운드 면에는 얇은 슬롯라인이 존재하여 상하에서 연결된 마이크로스트립 선로와 결합된다.

여기서 전력분배기의 설계 목적은 마이크로스트

립 단락을 위한 비아 홀과 슬롯라인 오픈을 위한 스파이럴 스터브를 이용한 천이 기술을 이용하여 전력 분배기의  $\lambda/4$  전송선로를 두 개의  $\lambda/8$  전송선로로 구현하기 위한 것이다. 이때 사용되는 천이 구조는 설계하는 주파수에서 작은 삽입손실과 큰 리턴로스를 얻어야 하므로, 설계하는 과정에서 천이구조에 적합한 마이크로스트립과 슬롯라인 스파이럴 스터브길이와 선폭을 결정하였다.

#### 2-2 마이크로스트립과 슬롯라인 천이

마이크로스트립과 슬롯라인 천이를 이용한 멀티 레이어 기판을 사용하여 윌킨슨 전력 분배기를 설계 하였다. 입력 포트는 공통 그라운드면의 후면에 그리 고, 두 개의 출력 포트는 전면에 위치하였다.

비아 홀을 이용한 마이크로스트립과 스파이럴 스터브의 슬롯라인을 이용한 천이구조를 사용한 윌킨슨 전력분배기의 시뮬레이션 도면은 그림 2에 나타내었다. 그림 2에서 나타난 것처럼 전면에는 두 개의 출력 포트와 고립 저항을 그리고 후면에는 입력 포트를 나타내었다. 중간의 그라운드 면의 얇은 슬롯라인은 전력 분배기의  $\lambda/4$  전송선로를 전면과 후면의 두 개의  $\lambda/8$  전송선로로 나누어진 70.7  $\Omega$ 의 전송선로를 결합시켜주는 역할을 한다. 이러한 이유로, 마이크로스트립과 슬롯라인 천이구조는 작은 삽입 손실과 큰 리턴로스 값을 갖고 있어야 만 한다. 여기에 사용된 슬롯라인은 기존 논문에서 제시한 값으로 구현하면 선폭이 너무 좁아서 제작하는데 어려움이 존재하므로 이러한 것을 없애고 제작하기 쉽게 하기 위하여 80  $\Omega$ 의 임피던스를 선택하여 슬롯라인을 설계하였다.

#### III. 시뮬레이션과 실험 결과

먼저 시뮬레이션을 통하여 마이크로스트립과 슬 롯라인 천이구조의 특성을 확인하였다. 슬롯라인의 스파이럴 스터브의 길이와 선폭은 동작 주파수 2 GHz에 적합하도록 최적화 과정을 통하여 결정하였 다. 최종 결정된 크기는 0.3 mm 선폭과 1.8 turn의 스 파이럴 구조 스터브을 결정하였다.

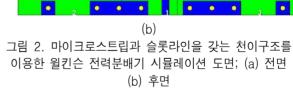

그림 3. 마이크로스트립과 슬롯라인 천이구조의 시뮬레이션 S-파라미터 특성

Fig. 3. Simulated S-parameters of the microstrip -slotline transitions.

이러한 구조로 설계된 마이크로스트립과 슬롯라인 천이의 특성은 그림 3에 S-파라미터로 나타내었다. 이 그림에서 천이구조는 중심 주파수 2 GHz에서 삽입손실 0.3 dB, 그리고 Return Loss는 20 dB 이하를 만족하는 것을 확인하였다. 제안한 마이크로스트립과 슬롯라인 천이구조는 슬롯라인의 양쪽 끝부분을 래디얼 스터브 또는 광대역 비아를 이용한 구조보다다역폭이 작은데 그 이유는 스파이럴 구조의  $\lambda/4$  스터브 때문으로 판단된다. 여기서는 대역폭 보다는 소자의 크기를 작게 구현하는 것을 우선적으로 선택했기 때문에 위의 구조로 설계한 것이다.

천이구조의 시뮬레이션을 위한 에폭시 재질은 유전율  $\epsilon_r = 4.4$ , 유전체 두께 h = 0.787 mm 인 것을 사용하였다. 또한, 중간 그라운드 면의 도체 두께는 0.035 mm 이다. 시뮬레이션에 사용된 툴은 AWR사의 Microwave Office 소프트웨어를 사용하였다.

제안된 윌킨슨 전력 분배기는 시뮬레이션에서 사용된 에폭시와 동일한 규격으로 사용하였고, 중심 주파수는 2 GHz 에서 설계하였다. 마이크로스트립과슬롯라인 천이를 이용한 윌킨슨 전력 분배기의 제작된 사진은 그림 4에 나타내었다. 그림 4(a)는 각 면의패턴을 나타낸 것이고, 그림 4 (b)는 제작된 PCB를나타낸 것이다. 이 그림에서 보면슬롯라인의 스파이럴 구조 때문에 기존 전력 분배기와 비교하여 그 면적 크기를 반으로 할 수 없는 것을 알 수 있다.

그림 4. 마이크로스트립과 슬롯라인 천이구조를 이용한 멀티 레이어 윌킨슨 분배기 PCB 사진; (a) 전면, 후면 그리고 중간면 패턴 (b) 제작된 PCB 사진

(후면) (b)

Fig. 4. Photographs of the implemented multilayer Wilkinson Power divider PCB using microstrip-slotline transition; (a) top, bottom, and middle layer patterns and (b) fabricated multilayer PCB (front and rear).

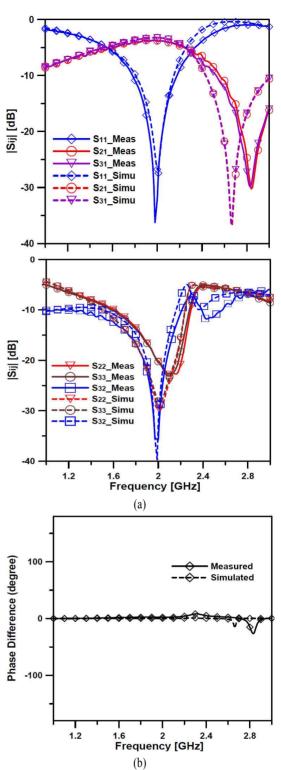

그림 5. 마이크로스트립과 슬롯라인 천이구조를 이용한 멀티 레이어 윌킨슨 분배기 측정 결과; (a) S-파라미터 (b) 출력 포트의 위상 차이

Fig. 5. Results of proposed multilayer Wilkinson power divider using microstrip-slotline transition; (a) S-parameters and (b) phase difference characteristics of output ports.

또한, 그림 5는 네트워크 분석기 HP8374ES를 사용하여 윌킨슨 전력 분배기를 측정한 결과를 나타낸 것이다. 결과를 살펴보면 |S21|과 |S31|의 삽입손실은 중심주파수 2 GHz 에서 각각 3.45 dB, 3.55 dB를 나타내고 있다. 시뮬레이션 값과 0.1 ~ 0.2 dB 차이가 나는 것은 에폭시 재질의 손실과 제작상의 에러에 의한손실이 추가된 것으로 판단된다. 출력 포트 사이의고립도 |S32|는 -25 dB 이하로 측정되었다. 또한, 입출력 포트의 Return Loss는 모두 15 dB 이하의 값을 갖고 있을 알 수 있다. 추가적으로 출력 포트 사이의 위상 차이는 1.5° 이내 이므로 동일 위상을 갖고 있음을 알 수 있다.

측정된 결과와 AWR 사의 Microwave Office로 시 뮬레이션 한 결과를 비교해보면 거의 일치함을 그림 5에서 관찰할 수 있다.

여기서 제시한 마이크로스트립과 슬롯라인 천이를 이용한 윌킨슨 전력 분배기는 기존의 전력 분배기와 면적 크기를 비교해 보면 65% 크기로 줄어든 것을 알 수 있었고, 그 이유는 천이를 위해서 필요한 슬롯라인 스파이럴 구조의 스터브 때문에 공간을 차지하게 되어 더 줄이는 것이 어려웠다.

#### Ⅳ. 결 론

본 논문에서는 마이크로스트립과 스파이럴 구조의 슬롯라인을 이용한 천이구조를 사용한 멀티 레이어의 컴팩트한 윌킨슨 전력 분배기를 설계하였다. 여기서 사용된 마이크로스트립과 슬롯라인의 천이구조로 인하여 기존의 전력분배기와 비교해서 그 면적의 크기를 35% 줄일 수 있었다. 또한, 이 천이 구조를 이용한 윌킨슨 분배기는 중심주파수 2 GHz에서 3.5 dB의 삽입손실, 모든 포트에서 Return Loss는 15 dB이하 그리고 출력 포트사이의 고립도는 -25 dB 이상 얻었다. 출력 포트사이의 위상 차이는 1.5° 이내로 동일한 위상으로 신호가 분배되는 것을 확인하였다.

이러한 설계 방법은 RF와 마이크로웨이브 영역의 수동 소자의 크기를 줄이는 방법으로 사용할 수 있을 것이다.

#### Reference

- [1] Hiro, T., A. Minakawa, and M. Muraguchi, "Reduce d-Size Branch-Line and Rat-Race Hybrids for Unipla nar MMICs," IEEE Trans. Microw. Theory Tech., vol. MTT-38, pp.270-275, Mar. 1990.

- [2] R. Mongia, I. Bahl, and P. Bhartia, RF and Microwave Coupled-Line Circuits, Boston: Artech House, 1999.

- [3] M. Park and B. Lee, "Stubbed Branch Line Balun," *IEEE Microwave Wireless Compon.* Lett., vol. 17, no. 3, pp.169-171, Mar. 2007.

- [4] S. -G. Kwan, Y. Kim, and Y.C. Yoon, "Power Divider using Shunt Open-Stub Loaded Transmission Line," *The Journal of Korea Navigation Institute*, vol. 15-5, pp.774-780, Oct. 2011.

- [5] Y. Kim and Y.C. Yoon, "An Unequal Divider based on Transmission Line with Periodic Capacitor Shunt Connect ion," *The Journal of Korea Navigation Institute*, vol. 16-5, pp.781-786, Oct. 2012.

- [6] A. M. Abbosh and M. E. Bialkowski, "Design of Compact Directional Couplers for UWB Applications," *IEEE Trans. Microw. Theory Tech.*, vol. 55, no. 2, pp.189-194, Feb. 2007.

- [7] S. B. Chon, "Slotline on a Dielectric Substrate," *IEEE Tran s. Microw. Theory Tech.*, vol. MTT-17, pp.768-778, 1969.

- [8] N. Seman, M. E. Bialkowski and W. C. Khor, "Ultra Wideband Vias and Power Dividers in Microstrip-Slot Tec hnology," *Proceeding of APMC 2007*, pp.1-4 Dec. 2007.

## 김 영 (Young Kim)

1988년 2월: 서강대학교 전자 공학과 (공학석사) 2002년 8월: 서강대학교 대학원 전자공학과 (공학박사) 1988년 1월 ~ 1993년 5월 : 이즈텔시스템즈(주) 연구소 선임연구원

1993년 6월 ~ 1998년 2월:

삼성전자(주) 정보통신사업본부 선임연구원 1998년 3월 ~ 2003년 2월 : 두원공과대학 정보통신과 조교수 2003년 3월 ~ 현재: 금오공과대학교 전자공학부 부교수 관심분야 : RF 및 Microwave 회로해석 및 설계, 전력 증폭기 및 선형화기 설계

### 심 석 현 (Seok-Hyun Sim)

2013년 3월 : 금오공과대학교

전자공학부 재학 중

관심분야 : RF 및 Microwave 회로 설계, Metamaterial

## 윤 영 철 (Young-Chul Yoon)

1978년 2월: 서강대학교 전자공학과 (공학사)

1982년 2월: 서강대학교 대학원

전자공학과 (공학석사)

1989년 2월: 서강대학교 대학원

전자공학과 (공학박사)

1987년 9월 ~ 현재 관동대학교

전자정보통신공학부 교수

관심분야 : RF 및 Microwave 회로설계