# Selective Chemical Wet Etching of Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si Multilayer

Yeon-Ho Kil, Jong-Han Yang, Sukil Kang, Tae Soo Jeong, Taek Sung Kim, and Kyu-Hwan Shim

Abstract—We investigate the effect of the ageing time and etching time on the etching rate of SiGe mixed etching solution, namely 1 vp HF (6%), 2 vp H<sub>2</sub>O<sub>2</sub> (30%) and 3 vp CH<sub>3</sub>COOH (99.8%). For this etching solution, we found that the etch rate of SiGe layer is saturated after the ageing time of 72 hours, and the selectivity of Si<sub>0.8</sub>Ge<sub>0.2</sub> layer and Si layer is 20:1 at ageing time of 72 hours. The collapse was appeared at the etching time of 9min with etching solution of after saturation ageing time.

*Index Terms*—Selective etching, SiGe, Si, multi-layer, SON

### I. Introduction

Silicon-on-insulator (SOI) structure is one of the most attractive candidates for metal—oxide—semiconductor devices for low-power and high-speed applications, because it is easy to reduce a coupling capacitance by using this structure [1]. The buried, perfectly insulating SiO<sub>2</sub> layer with a typical thickness of several 100 nm eliminates several leakage paths. Nevertheless, many different SOI structures are presently under investigation with a standard bulk structure. However, the SOI substrate is expensive and the poor thermal conductivity of the buried silicon dioxide may create a heat problem. Specific substrate treatments, such as separation by ion implantation of oxygen, and epitaxial layer transfer, have to be prepared before the device fabrication [2-5]. Moreover, it is difficult to obtain the silicon layer with

damage or the defects occur during the epitaxial growth. Recently, a silicon-on-nothing (SON) transistor, which has a void under the transistor region, has been proposed as one of the ideal structure of SOI, because the dielectric constant at the region below the transistors could be with this structure [6-14]. SON structure was originated from the capability of selectively removing SiGe alloys against Si. Therefore a high selectivity between Si and Si<sub>1-x</sub>Ge<sub>x</sub> is needed. Different methods for selective etching are have been-known, like Electron Cyclotron Resonance (ECR) plasma etching [15], Reactive ion etching (RIE) [16] or selective vapor phase etching with HCl using thermal CVD processes performed in a CVD tool [17, 18]. High temperatures (650 - 750°C) are needed to achieve selectivity around 5 for x=0.2 [17]. And, HF:PAA solution, HF:HNO<sub>3</sub> solution, HF:CH<sub>3</sub>COOH:HNO<sub>3</sub> or H<sub>2</sub>SO<sub>4</sub> solution and HF:H<sub>2</sub>O<sub>2</sub>:CH<sub>3</sub>COOH solution were used for wet etching with a great selectivity compared to Si [19-21]. Wet chemical etching techniques are widely used in semiconductor technology for device processing, identifying crystal symmetries, and revealing threading dislocations. Etching techniques represent a critical step in the fabrication of novel micro- and nano-devices. In addition, selective wet chemical etching was also successfully used for various applications, such as for fabricating micro electro mechanical systems (MEMS) or Si nanowires [19-21]. Two important parameters of chemical selective wet etching have also been checked: ageing time of etching solution and structure collapse during/after the wet etching. It was reported by U. Wieser et al. that HF:H<sub>2</sub>O<sub>2</sub>:CH<sub>3</sub>COOH served as a highly selective etchant in etching Si<sub>l-x</sub>Ge<sub>x</sub> over Si with much higher selectivities [22]. Optimum masking capability of the

defect-free crystalline quality due to the ion-implantation

Manuscript received Jun. 3, 2013; accepted Oct. 1, 2013 Semiconductor Physics Research Center, Chonbuk National University E-mail: tskim@jbnu.ac.kr

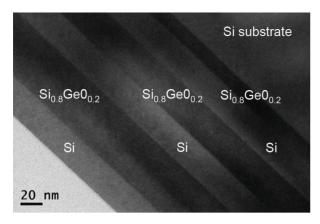

Fig. 1. TEM images of the  $Si_{0.8}Ge_{0.2}/Si$  multilayer grown by using RPCVD.

resist and reliable pattern transfer is achieved by successively applied selective etching. Nanoscale patterning of several different Si/SiGe heterostructures was showed that both the line width and the break undercut nanoscales with the etch depth of the transferred groove depend on the thickness of the Si cap layer. Although the results were repeatable, the exact etching mechanism was not well understood. Indeed, for all SON-based integrations in single or multigates technologies, sacrificial SiGe layers are defining either the BOX or the gate stack. These layers are then efficiently removed by the etching solution with a great selectivity.

In this paper, a comprehensive study of the etching behavior of this high selectivity etchant is presented, including the etch rate dependence of  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  (x = 0.2) on solution ageing time, and of the SiGe layer thickness (from 10 up to 60 nm) on the lateral solution etch kinetics of ( $\mathrm{Si}_{1-x}\mathrm{Ge}_x/\mathrm{Si}$ ) x3 multilayer. Several process parameters have been jointly studied such as etch rates, selectivity and collapse. we propose an innovative process SON enabling fabrication of the desired "super SOI" devices which are capable of quasitotal suppression and excellent electrical performances thanks to the extremely thin silicon (40 nm) and buried dielectric (10 to 60 nm) by using the simple HF:H<sub>2</sub>O<sub>2</sub>:CH<sub>3</sub>COOH solution with a great selectivity.

## II. EXPERIMENT

The samples used for selective wet etching were grown by using reduced pressure chemical vapor deposition (RPCVD) system. The Si substrates were

**Fig. 2.** Schematic of dry etching patterning and generic sample structure used for selective wet etching.

Stripe pattern photo litho - pattern size : 5 um / 100 um ICP/RIE(F) Dry Etching - Etching depth : about 300 nm

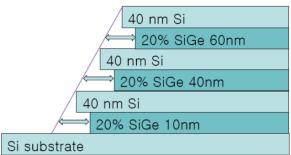

cleaned through a normal cleaning procedure (a hydrogen bake step to clear the surface from native oxide, performed at 1100°C) before the SiGe layer growth. The growth of the SiGe layer was then commenced by switching the SiH<sub>4</sub> and GeH<sub>4</sub> (1.5% diluted in H<sub>2</sub>) into reactor. The flow rates of SiH4 and GeH4 were changed from 10 to 100 sccm and from 40 to 300 sccm, respectively. The flow rate of H<sub>2</sub> was fixed at 10slm. The growth temperature was  $600^{\circ}$ C with a growth rate of 3.2 nm/min for the SiGe layer and a growth rate of 3.8nm/min for the Si layer. Finally, the layer structures were completed by depositing a 40 nm Si cap layer. The Ge concentration in the SiGe layers is 20%. The layer thicknesses and compositions were determined by TEM and EDX and showed excellent agreement with the nominal values. Fig. 1 shows the TEM image of the Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayer grown by using RPCVD. The multilayer structure was consisted of a 10nm-thick Si<sub>0.8</sub>Ge<sub>0.2</sub> layer, 40nm-thick Si layer, 40nm-thick Si<sub>0.8</sub>Ge<sub>0.2</sub> layer, 40nm-thick Si layer, 60nm-thick Si<sub>0.8</sub>Ge<sub>0.2</sub> layer, and 40nm-thick Si cap layer [23].

Samples used for the etching experiments were

typically,  $1 \times 1 \text{ cm}^2$  in size and were cut from 6-inch wafers. Then, samples were spin-coated with a photoresist by using spin-coater at 5000 rpm for 30 s; then, they were placed in an oven for soft baking at 90°C for 30 min. Photolithography was performed using a mask aligner I-line and ultraviolet light (365 nm) with an intensity of approximately 5 mW. Four-inch mask plates with features of lines were used for patterning for the etching experiments.

The samples were etched in a load-locked BMR (HiEtch) high-density plasma etching system consisting of an ICP chamber (operating at 2 MHz) and an additional RF bias (13.56 MHz) for the sample chuck. Helium back-side cooling was incorporated to allow the temperature of the substrate to be controlled more effectively. A CF<sub>4</sub> gas with a purity of 99.999% was introduced for etching [24]. The schematic of dry etching patterning and generic sample structure used for selective wet etching is shown in Fig. 2.

The samples were dipped in a 1:2:3 vol. (6%HF:30%H<sub>2</sub>O<sub>2</sub>:99.8%CH<sub>3</sub>COOH) solution (BPA) [21, 25]. All etching experiments were performed at room temperature without stirring the solution. Immediately after etching, the samples were rinsed for 30 s in deionizer water and subsequently dried with nitrogen gas. The etching rate was determined from the deep profile measured by scanning electron microscopy (SEM).

#### III. RESULT AND DISCUSSION

We consider here SiGe etching solution, namely 1:2:3 (6%HF/30%H<sub>2</sub>O<sub>2</sub>/ 99.8%CH<sub>3</sub>COOH) solution (BPA). This etching solution is known to selectively etch Si<sub>1-x</sub>Ge<sub>x</sub> alloys over pure Si [21, 24, 28, 29]. Two important parameters of chemical selective wet etching have also been checked: ageing time of etching solution and structure collapse during/after the wet etching. First, the effects of Si<sub>1-x</sub>Ge<sub>x</sub> alloys and Si etching by varied processing parameter are discussed. The Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayer was etched in a solution consisting of BPA at room temperature. First of all a new etching solution has been prepared. The Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayers are etched for 5 min in etching solution with ageing time of 0 hours, 24 hours, 48 hours, 72 hours, and 96 hours respectively. Etch rates and depth profiles are determined as a function of ageing time of varied etching solution. The etch rate and selectivity of BPA increases with the ageing time [21].

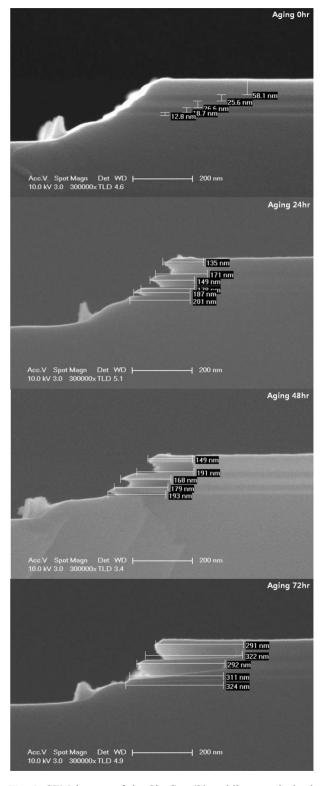

Fig. 3 shows the SEM images of etch depth profiles

**Fig. 3.** SEM images of the Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayer etch depth profiles vs. ageing time at the etching time of 9 min.

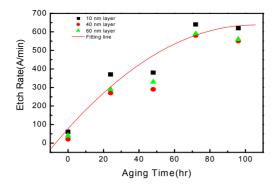

Fig. 4. Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayer etch rate vs. ageing time.

for Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayer as a function of ageing time of varied etching solution. Fig. 4 shows the results of etch rates for Si<sub>0.8</sub>Ge<sub>0.2</sub> layer as a function of varied solution ageing time. It shows that the etch rate of 10nm-thick  $Si_{0.8}Ge_{0.2}$  layer were 60 Å/min, 370 Å/min, 380 Å/min, 640 Å/min, and 640 Å/min as ageing times were 0 hours, 24 hours, 48 hours, 72 hours, and 96 hours, respectively. Also, the etch rate of Si layer were 23 Å/min, 27 Å/min, 22 Å/min, 27 Å/min, and 29 Å/min as ageing times were 0 hours, 24 hours, 48 hours, 72 hours, and 96 hours, respectively. The etch rate of Si<sub>0.8</sub>Ge<sub>0.2</sub> layer is always greater than that of the Si layer and saturation of the Si<sub>0.8</sub>Ge<sub>0.2</sub> layer etch rates is observed as a function of ageing time. And the Si<sub>0.8</sub>Ge<sub>0.2</sub> layer versus Si selectivity strongly depends upon of the etching solution. It was found that the saturated Si<sub>0.8</sub>Ge<sub>0.2</sub> layer versus Si selectivity is over the ageing time of 72 hours, and the selectivity of Si<sub>0.8</sub>Ge<sub>0.2</sub> layer and Si layer is 20:1 at ageing time of 72 hours. Therefore, the proper ageing time of BPA should be 72hours at least.

As observed from the etching rate behavior of Si in HF:H<sub>2</sub>O<sub>2</sub>:CH<sub>3</sub>COOH, the Si atoms is not easy to be oxidized since plenty of HF is available for dissolution of any SiO<sub>2</sub> which may form. This behavior is to be expected as Si is not easily oxidized by H<sub>2</sub>O<sub>2</sub> [26]. The presence of these two plateaus suggests that two different etching processes may be taking place. The etching process in the first plateau region is believed to be the same as for the standard etching of Ge in HF:H<sub>2</sub>O<sub>2</sub> solutions with additional enhancement from the reaction of H<sub>2</sub>O<sub>2</sub> and CH<sub>3</sub>COOH. The etching of Ge with H<sub>2</sub>O<sub>2</sub> solutions has been well studied by a number of authors [30]. Because of the presence of Ge, Si<sub>1-x</sub> Ge<sub>x</sub> is expected to be etched in HF:H<sub>2</sub>O<sub>2</sub> solutions, but should have lower

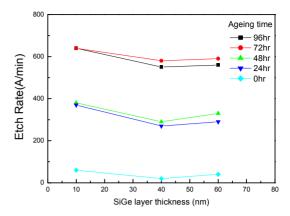

**Fig. 5.**  $Si_{0.8}Ge_{0.2}/Si$  multilayers etch rate vs.as a function of the SiGe layer thickness.

etch rates due to the difficulty in oxidizing the Si atoms [25].

Previously, many studies has taken place using HF:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O for the etching of Ge [27]. However, when this water-based diluents solution was used to etch Si<sub>1-x</sub> Ge<sub>x</sub>, etch rates become lower. And it is evident that little change in the etch rate occurs with stirring and hence no etch rate or waiting time dependence on stirring could be seen for etching Si<sub>1-x</sub>Ge<sub>x</sub> in HF:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (1:2:3) [25]. As mentioned previously, this is to be expected due to the retarded oxidation of Ge in the presence of the Si atoms, which restrict etching. In this situation fewer Ge atoms are available for oxidation [25]. But the presence of the diluents CH3COOH changes the nature of the etching reaction. The etch rates are twice as high when using acetic acid instead of water. It is believed that the reaction between H<sub>2</sub>O<sub>2</sub> and CH<sub>3</sub>COOH in the oxidation of the Ge atoms in Si<sub>1-x</sub> Ge<sub>x</sub> is responsible for the waiting time and two plateau regions observed with this etchant.

As discussed above, the reaction between  $H_2O_2$  and  $CH_3COOH$  is of great importance in understanding the etching behavior found in this study. Carns *et al.* [25] have found that hydrogen peroxide reacts with carboxylic acids to form peroxy acids of the form of  $RCO_3H$  as follows

$$RCO_2H+H_2O_2\rightarrow RCO_3H+H_2O$$

(1)

However, they point out that the reaction is slow even with readily soluble acids such as acetic acid, needing at least 1 hour to form. They also point out that as the amount of  $H_2O_2$  in the solution is reduced, the amount of

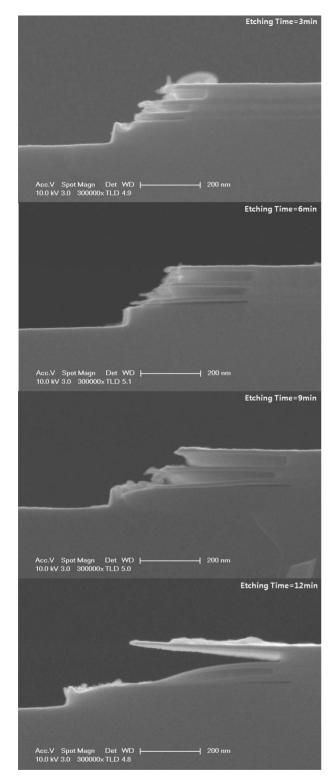

Fig. 6. SEM images of the  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}/\mathrm{Si}$  multilayer etch rate after saturation ageing.

RCO<sub>3</sub>H formed will be reduced since this reaction is reversible. These factors may explain the following reactions between both H<sub>2</sub>O<sub>2</sub> with CH<sub>3</sub>COOH, and Ge with CH<sub>3</sub>COOH. Based on reaction (1), reactions (2) and

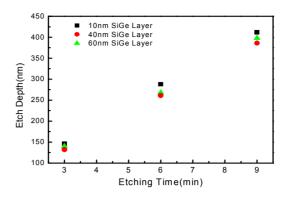

Fig. 7. Si<sub>0.8</sub>Ge<sub>0.2</sub> layer etch depth after saturation ageing.

(3) below may occur

$$2CH_3COOH+2H_2O_2\rightarrow 2CH_3COOOH+2H_2O$$

(2)

The peroxy acid would then be available to ionize the Ge atom as follows

$$Ge+2CH_3COOOH+2e \rightarrow Ge^{+2}+2CH_3COO^{-}+2OH^{-}$$

(3)

In Fig. 4, etch rate between 10nm layer to 40nm layer have no regularity. The etch rate of  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  layers increase when increasing the  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  layer thickness from 40 up to 60 nm. However, the etch rate of SiGe layers decreases when increasing the  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  layer thickness from 10 up to 40 nm, as shown in the Fig. 5. Because, it is found that the etch rate effects is on strain issue under  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  critical thickness [25].

For structure collapse during/after the wet etching, Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayers are etched for after saturated ageing time as a function of varied etching time. Fig. 6 shows the SEM images of etch depth profiles for Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si multilayer as a function of varied etching time after saturation ageing time. Fig. 7 shows the results of etch depth for Si<sub>0.8</sub>Ge<sub>0.2</sub> layers as a function of varied etching time after saturation ageing time. The Si<sub>0.8</sub>Ge<sub>0.2</sub> layers etch depth linearly increase when increasing the etching time from 3 up to 9 min at a saturation ageing time, as shown in the Fig. 7. The collapse was appeared at the etching time of 9 min by using etching solution of after saturation ageing time.

#### IV. CONCLUSIONS

The etch rate and selectivity of BPA increases with the

ageing time between mixing the ingredients and use. The etch rate of Si<sub>0.8</sub>Ge<sub>0.2</sub> layer is always greater than that of Si layer etch rate and saturation of the SiGe layer etch rates are observed at the ageing time of after 72 hours. And the selectivity of Si<sub>0.8</sub>Ge<sub>0.2</sub>.layer and Si layer is 20:1 at ageing time of 72 hours. Therefore, the proper ageing time of BPA should be 72 hours at least. Also, the optimum ageing time of etching solution should be performed in more than 72 hours, and the collapse was appeared at the etching time of 9 min.

#### **ACKNOWLEDGMENTS**

This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2009-0094031) and (Grant No. 2013R1A1A2010053). It was also supported by the Future Semiconductor Device Technology Development Program (Grant No. 10044651) funded By MOTIE (Ministry of Trade, Industry & Energy) and KSRC (Korea Semiconductor Research Consortium).

## REFERENCES

- [1] T. Skotnicki, Microelectronic Engineering, 84 (2007) 1845.

- [2] K. Izumi, M. Doken, and H. Ariyoshi, Electron. Lett., 14 (1978) 593.

- [3] T. Yonehara, K. Sakaguchi, and N. Sano, Appl. Phys. Lett., 64 (1994) 2108.

- [4] M. Bluel, Electron. Lett., 31 (1995) 1201.

- [5] K. Bernstein, and N. J. Rohrer, SOI CIRCUIT DESIGN CONCEPTS, Chap. 2. Academic Publishers (2002)

- [6] M. Jurczak, T. Skotnicki, M. Paoli, B. Tormen, J. Martins, J. L. Regolini, D. Dutartre, P. Ribot, D. Lenoble, R. Pantel, and S. Monfray, IEEE TRANSACTIONS ON ELECTRON DEVICES, 47 (2000) 2179.

- [7] V. Kilchytska, D. Flandre, and J.-P. Raskin, Applied Surface Science, 254 (2008) 6168.

- [8] S. Chiussi, F. Gontad, R. Rodríguez, C. Serra, J. Serra, B. León, T. Sulima, L. Höllt, and I. Eisele, Applied Surface Science, 254 (2008) 6030.

- [9] T. Sato, H. Nii, M. Hanano, K. Takenaka, H.

- Hayashi, K. Ishigo, T. Hirano, K. Ida, N. Aoki, T. Ohguro, K. Ino, I Mizushma, and Y. Tsunashima, Electron Devices Meeting, p. 37. IEDM Technical Digest. International (2001).

- [10] S. Monfray, D. Chanemougame, S. Borel, A. Talbot, F. Leverd, N. Planes, D. Delille, D. Dutartre, R. Palla, Y. Morand, S. Descombes, M-P.Samson, N. Vulliet, T. Sparks, A. Vandooren, and T. Skotnicki, Electron Devices Meeting, p. 635. IEDM Technical Digest. International (2004).

- [11] S. Hanison, P. Corone1, F. Leverd, R. Cerutti, R. Palla, D. Delille, S. Bore1, S. Jullian, R. Pante1, S.Descombes, D. Dutartre, Y. Morand, MP. Samson, D. Lenoble, A. Talbot, A. Villaret, S. Monfray, P. Mazoyer, J. Bustos, H. Brut, A. Cros, D. Munteanu, J-L. Autran, and T.Skotnicki, Electron Devices Meeting, p. 18. IEDM '03 Technical Digest. IEEE International (2003).

- [12] S. Borel, V. Caubet, D. Lafond, O. Kermarrec, and Y. Campidelli, IEEE Transactions on Electron Devices, 47 (2000) 2179.

- [13] C. Durand, F. Casset, P. Renaux, N. Abelé, B. Legrand, D. Renaud, E. Ollier, P. Ancey, A. M. Ionescu, and L. Buchaillot, IEEE ELECTRON DEVICE LETTERS, 29 (2008) 494.

- [14] S. Monfray, T. Skotnicki, C. Fenouillet-Beranger, N. Carriere, D. Chanemougame, Y. Morand, S. Descombes, A. Talbot, D. Dutartre, C. Jenny, P. Mazoyer, R. Palla, F. Leverd, Y. Le Friec, R. Pantel, S. Borel, D. Louis, N. Buffet, Solid-State Electronics, 48 (2004) 887.

- [15] Takeuchi, Matsuura, Murota, Appl. Phys. Lett., 77 (2000) 1828.

- [16] Y. Zhang, G. S. Oehrlein, and E. de Fèsart, J. Appl. Phys., 71 (1992) 1936.

- [17] Y. Yamamoto, K. Köpke, B. Tillack, Thin Solid Films, 517 (2008) 90.

- [18] N. Loubet, T. Kormann, G. Chabanne, S. Denorme,D. Dutartre, Thin Solid Films, 517 (2008) 93.

- [19] J. L. Liu, Y. Shi, F. Wang, Y. Lu, R. Zhang, P. Han, S. L. Gu, and Y. D. Zheng, Appl. Phys. Lett., 68 (1996) 352.

- [20] N. Loubet, F. Boeuf, S. Monfray, C. Fenouillet-Beranger, S. Denorme, G. Bidal, T. Skotnicki, and D. Dutartre, ECS Transactions, 16 (2008) 29.

- [21] U. Wiesera, U. Kunzea, K. Ismailb, and J. O. Chub, Physica E, 13 (2002) 1047.

- [22] U. Wieser, D. Iamundo, U. Kunze, T. Hackbarth and U. König, Semiconductor Science and Technology 15 (2000) 862.

- [23] T. S. Kim, Y-H. Kil, M. I. Shin, T. S. Jeong, S. Kang, C-J. Choi, and K. H. Shim, ECS Transactions, 33 (2010) 211.

- [24] T. S. Kim, H. Y. Yang, Y. H. Kil, T. S. Jeong, S. Kang, and K. H. Shim, J. Korean Phys. Soc., 54 (2009) 2290.

- [25] T. K. Carns, a M. O. Tanner, and K. L. Wang, J. Electrochem. Soc., 142 (1995) 1260.

- [26] D. Godbey, H. Hughes, E Kub, M. Twigg, L. Palkuti, P. Leonov, and J. Wang, Appl. Phys. Lett., 56 (1990) 373.

- [27] D. J. Godbey, A. H. Krist, K. D. Hobart, and M. E. Twigg, J. Electrochem. Soc., 139 (1992) 2943.

- [28] Bo Jin, Xi Wang, Jing Chen, Xinli Cheng, and Zhijun Chen, Appl. Phys. Lett., 87 (2005) 051921.

- [29] B. Holländer, D. Buca, S. Mantl, and J. M. Hartmann, J. Electrochem. Soc., 157 (2010) H643.

- [30] Kirt R. Williams, Kishan Gupta, and Matthew Wasilik, J. MEMS, 12 (2003) 762.

Yeon-Ho Kil received the B.S. in the Department of Semiconductor of Science and Technology from Chonbuk National University, Korea, in 2007 and M.S. degree in the School of Semiconductor and Chemical Engineering from

Chonbuk National University, Korea, in 2009, respectively. He is currently pursuing the Ph.D. degree in the School of Semiconductor and Chemical Engineering from Chonbuk National University, Korea. His interests include Ge on Si growth and characterization.

Jong-Han Yang received the B.S. in the Department of Physics from Chonbuk National University, Korea, in 2010. He is currently pursuing the M.S. degree in the School of Semiconductor and Chemical Engineering from Chonbuk National

University, Korea. His research interests include semiconductor and optoelectronic device.

**Sukil Kang** received the B.S., and M.S. degrees in the Department of Physics from Chonbuk National University, Korea, in 1988, and 1990, respectively, and the Ph.D. degree from the Department of Physics and Astronomy, University of Tennessee,

Knoxville, in 2001. In 2007, he joined the Faculty of Department of Physics, Chonbuk National University, where he is currently Professor. His research interests include Oxides and semiconductor materials growth and characterization.

**Tae Soo Jeong** received the B.S., M.S., and Ph.D. degrees in the Department of Physics from Chonbuk National University, Korea, in 1985, 1988, and 1993, respectively. In 2001, he joined the Faculty of Semiconductor Physics Research

Center, Chonbuk National University, Korea, where he is currently a Research Professor. His research interests include optoelectronic device, Ge on Si growth and optical characterization.

**Tack Sung Kim** received the B.S., M.S., and Ph.D. degrees in the Department of Physics from Chonbuk National University, Korea, in 1988, 1990, and 1996, respectively. In 2001, he joined the Faculty of Semiconductor Physics Research

Center, Chonbuk National University, Korea, where he is currently a Research Professor. His research interests include optoelectronic device, Ge on Si growth and optical characterization.

**Kyu-Hwan Shim** received the B.S. degree in 1984 and the M.S. degree in 1986 from the Department of Materials Science and Engineering, Korea University in Korea. He received the Ph.D. degree in 1997 from the Department of Materials

Science and Engineering, University of Illinois at Urbana-Champaign, USA. He joined the Electronics and

Telecommunications Research Institute (ETRI) as a researcher in 1986, and became a principal researcher in 2000. He performed many national projects to develop specific semiconductor devices like MESFET, MOSFET, HBT, HEMT using compound semiconductors like GaAs, GaN, and SiGe. Ever since his movement to Chonbuk National University in 2004, he has been leading Intelligent Semiconductor Research Laboratory (ISRL) as a professor in the Department of Semiconductor Science and Technology. The ISRL focuses its research area on SiGe, Ge-on-Si, and III-nitrides for the development of new electronic and photonic devices. Meanwhile, he founded a start-up, Sigetronics, Inc., in 2008, in which various specific semiconductor devices including Zener (for GaN-based LEDs), TVS, FRD, SBD, ESD/EMI filters have developed been commercialized.