# 배터리 용량측정을 위한 고해상도 Integrating Sigma-Delta ADC 설계

Design of a High-Resolution Integrating Sigma-Delta ADC for Battery Capacity Measurement

박 철 규\*, 장 기 창\* 우 선 식\*, 최 중 호\*\* Chulkyu Park\*, Kichang Jang\*, Sunsik Woo\*, Joongho Choi\*\*

#### Abstract

Recently, with mobile devices increasing, as a variety of multimedia functions are needed, battery life is decreased. Accordingly the methods for extending the battery life has been proposed. In order to implement these methods, we have to know exactly the status of the battery, so we need a high resolution analog to digital converter(ADC). In case of the existing integrating sigma-delta ADC, it have not convert reset-time conversion cycle to function of resolution. Because of this reason, all digital values corresponding to the all number of bits will not be able to be expressed. To compensated this drawback, this paper propose that all digital values corresponding to the number of bits can be expressed without having to convert reset-time additional conversion cycle to function of resolution by using a up-down counter. The proposed circuit achieves improved SNDR compared to conventional converters simulation result. Also, this was designed for low power suitable for battery management systems and fabricated in 0.35um process.

#### 요 약

최근 모바일 기기의 수요의 증가와 더불어 다양한 멀티미디어 기능을 요구함에 따라 배터리 사용시간이 줄어들고 있다. 이에 따라 배터리 사용시간을 늘이기 위한 여러 가지 방법들이 제안되고 있다. 이러한 방법을 구현하기 위해서는 배터리 상태를 정확히 알아야 하며, 이를 위한 고해상도 아날로그-디지털 변환기를 필요로 하게 된다. 기존의 integrating sigma-delta ADC의 경우, 초기화-시간 변환시간을 해상도로 변환을 하지 않는 단점이 있다. 이런 단점으로 인해 bit수에 해당되는 모든 디지털 값을 표현 할 수 없게 된다. 위와 같은 단점을 보완하기 위해본 논문에서는 올림/내림 계수기를 사용함으로써 초기화-시간 변환시간을 해상도로 변환을 하지 않고도 bit수에 해상되는 모든 디지털 값을 표현 가능하게 하였다. 이로 인해 기존 변환기의 시뮬레이션 결과에 비해 향상된 SDNR을 보여주었다. 또한 휴대용 배터리 관리 시스템에 적합하도록 저전력으로 설계를 진행 하였으며, 0.35-um 공정으로 제작이 이루어졌다.

Key words: Sigma-Delta Modulation, Analog Compensation, Digital Calibration, LSB Calibration

\*서울市立大學校 電子電氣컴퓨터工學部

(School of Electrical and Computer Engineering. University of Seoul)

- ★ 교신저자 (Corresponding author)

- ※ 이 논문은 2010년도 서울시립대학교 교내학술연구비에 의하여 연구되었음

接受日:2011年 12月 15日, 修正完了日: 2012年 02月 10日 揭載確定日: 2012年 02月 17日

# I . 서론

오늘날 전력반도체는 컴퓨터, 통신, 가전 및 자동차 등 중추적인 전자 어플리케이션에 적용되고 있다. 이러한 어플리케이션은 IT 기기의 성능을 향상시키는 것과 동시에 친환경 에너지 절감형 스마트제품으로의

발전을 목표로 하고 있다. 따라서 이를 위한 고급전력관리 기술 개발이 요구되고 있다. 이와 같은 분야에서 활용되는 리튬전지는 휘발유보다 더 휘발성이 강한 액체가 들어 있다. 따라서 과충전시 전류 제어보호회로가 없다면 직/병렬로 연결되어 있는 특정부분에 과전류가 흐르게 되고 전지발화 현상이 나타나게 된다. 이런 현상을 방지하기 위해 안전한 보호회로가 필요하고 이런 요구를 만족하기 위한 기술이 휴대용 배터리 전력 제어 IC(BMIC)가 필요하다.

BMIC는 휴대기기 및 전기자동차의 배터리 전력제어를 지능적으로 구현 할 수 있고, 이들 자체적으로 고효율로 동작하기 위해 저전력으로 동작되어야 한다. 이와 같은 IC에 사용되는 데이터 변환기는 높은 정확도 및 선형성을 필요로 한다. 다시 말해 높은 해상도를 요구하며, 주변 환경 및 오프셋, 이득 에러에 대해둔감해야 한다. 이러한 조건을 만족하는 데이터 변환기로는 sigma-delta modulation에 기반을 둔 integrating converter가 적합하다. 이 변환기의 특징으로는 낮은 변환 속도를 가지고 있으나, 높은 해상도 및 낮은 소모 전력을 보여주며 간단한 구조로 인해추가적인 디지털 프로세싱이 용이하다는 장점이었다.[1]

기존의 single slope방식 ADC의 연산증폭기에서 발생하는 오프셋 및 스위치로부터 발생하는 전하주입현상의 에러를 보정하기 위해 아날로그 보상기법을 사용하고, ADC 시스템 상의 오프셋 및 이득 에러를 바로 잡기 위한 디지털 교정기법을 사용하였다.[2-3] 또한, 최하위 비트의 정확성 향상을 위해 새로운 기법을 적용하여 성능을 개선하였다. 구현한 integrating sigma-delta ADC는 해상도 16-bit, 전원전압 3.3V에서 전체 소모 전류 240uA를 사용하여 0.79mW의 소모 전력을 나타낸다.

# Ⅱ. 본론

#### 1. Integrating Sigma-Delta ADC

가. 구조 및 동작위리

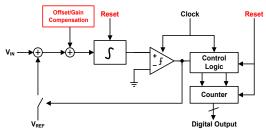

1차 integrating sigma-delta ADC의 일반적인 블록선도는 그림 1에 나타나 있다. 구성 블록으로는 들어오는 입력에 대한 입력 전압을 누적해주는 적분기, 누적된 값과 기준전압을 비교해주는 비교기, 기타 제어 블록 및 계수기로 구성 되어 있다. 기본 동작 원리는 다음 1-2와 같으며, 1-2를 반복 수행함으로써디지털 데이터를 출력하게 된다.[1]

1. 각각의 아날로그-디지털 변환 시 적분기 및 계 수기가 초기화를 한 후, 데이터 변환을 시작한다. 2. 적분기에서는 고정된 사이클 동안 입력 전압을 누적하게 된다. 비교기에서는 적분기 출력이 기준전 압보다 높을 경우, 감지 신호를 내보내게 된다. 이 때, 적분기에서는 감지 신호와 함께  $V_{REF}$  전압을 감산해주게 되고, 계수기에서는 감지 신호가 생성 될 때마다 가산을 하게 된다. 이와 같은 과정을 고정된 사이클 동안 반복 하게 되고, 계수기에 출력 되는 데이터 (N)은 다음과 같다.

$$N=2^n V_{IN}/V_{REF} \tag{1}$$

여기에서 n은 고정된 사이클을 의미하며  $V_{IN}$ 은 입력 전압,  $V_{REF}$ 는 기준 전압이 된다. N은 계수기의 출력 값으로 아날로그-디지털 변환기의 디지털 데이터 값이 된다.

Fig. 1. Block Diagram of Integrating Sigma-Delta ADC 그림 1. Integrating Sigma-Delta ADC의 블록선도

# 나. 아날로그 보상 기법

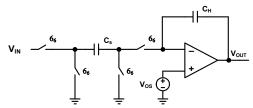

일반적인 적분기의 구조는 그림 2에 나타나 있다.

Fig. 2. Structure of Integrator 그림 2. 적분기 구조

하지만, 연산증폭기에 그림과 같이 오프셋 전압이 발생 하였을 경우,[2-3] 입력과 출력의 전달 함수는 식(6)과 같다. 전달 함수를 구하기 위해 커패시터 전하량 보존의 법칙에 의해 해석 할 수 있다.

$\Delta Q_S$  = C<sub>S</sub>의 전하 변화량

$\Delta Q_H$  =  $C_H$ 의 전하 변화량

이며, 다음과 같이 해석 할 수 있다.

$$\Delta Q_S = C_S(0 - V_{OS}) - C_S(V_{IN}[n-1] - 0)$$

(2)

$$\Delta \textit{Q}_{\textit{H}} = \textit{C}_{\textit{H}} \big( \textit{V}_{\textit{OS}} - \textit{V}_{\textit{OUT}}[n] \big) - \textit{C}_{\textit{H}} \big( \textit{V}_{\textit{OS}} - \textit{V}_{\textit{OUT}}[n-1] \big) (3)$$

전하량 보존 법칙에 따라 정리하면 다음과 같다.

$$\Delta Q_{S} = \Delta Q_{H} \tag{4}$$

$$-C_S V_{OS} - C_S V_{IN}[n-1] =$$

$$C_H V_{OS} - C_H V_{OUT}[n] - C_H V_{OS} + C_H V_{OUT}[n-1]$$

(5)

$$V_{OUT}[n] = V_{OUT}[n-1] + \left(\frac{C_S}{C_H}\right)V_{IN}[n-1] + \left(\frac{C_S}{C_H}\right)V_{OS}(6)$$

Fig. 3. FFT Simulation Result 그림 3. FFT 시뮬레이션 결과

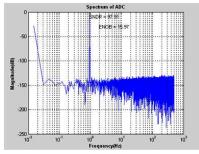

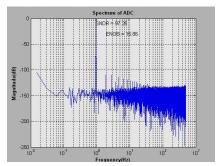

수식 (4)-(6)과 같이 매 사이클 마다 연산 증폭기의 오프셋 전압은 적분기의 출력에 그대로 반영되는 문제점이 발생하게 된다. 그림 3의 FFT 시뮬레이션 결과에서 보듯이 오프셋이 누적됨에 따라 DC 주파수성분의 크기가 커지는 것을 확인 할 수 있다. 이러한 문제점을 보정하기 위해 n번의 사이클을 추가하여 위의 문제를 해결 하였다.[1]

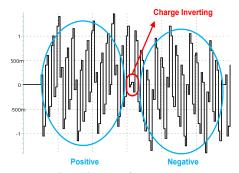

동작 원리는 다음과 같다. 첫 번째 구간 동안 적분기는  $(C_S/C_H)V_{IN}$ 을 각각 사이클 동안 더해준다. 이때, 적분기의 출력 전압  $V_{OUT}$ 이 높은 경우,  $V_{REF}$  전압을 빼주게 되고 반대로  $V_{OUT}$ 이 낮은 경우,  $V_{REF}$  전압을 더해 주게 된다. 이 때 올림/내림 계수기에서는  $V_{REF}$  전압을 빼줄 경우 가산을 하며,  $V_{REF}$  전압을 더할 경우 감산을 수행한다. 첫 번째 구간 동안 적분기에 출력 값은 식(7)과 같다.

$$V_{OUT1} = \left(\frac{C_{\!S}}{C_{\!H}}\right)\!\left[2^n\,V_{I\!N}\!-\!\left(N_{\!S\!1}-N_{\!A\!1}\right)V_{REF}\!+\!2^{n+1}\,V_e\right]\ \ \, (7)$$

두 번째 구간은 첫 번째 구간동안 수행하여 얻은 전압을 반전 해주는 구간으로 식(8)과 같다.

$$V_{OUT2} = -V_{OUT1}$$

(8)

세 번째 구간은 첫 번째 구간과 연산이 유사하지만, 차이점은 적분기가  $(C_S/C_H)V_{IN}$ 을 각각 사이클 동안 빼주게 된다. 또한 올림/내림 계수기는  $V_{REF}$  전압을 빼줄 경우 감산을 하며,  $V_{REF}$  전압을 다할 경우가산을 수행한다. 세 번째 구간의 동작을 마친 뒤의적분기 출력 값은 식(9)와 같다.

$$V_{OUT2} = -V_{OUT1}$$

$$+ \left(\frac{C_{S}}{C_{H}}\right) \left[-2^{n} V_{IN} - \left(N_{S1} - N_{A1}\right) V_{REF} + 2^{n+1} V_{e}\right] \tag{9}$$

위의 식을 다시 정리하면 식(10)과 같으며, 연산증폭기의 오프셋 전압 및 스위치로부터 발생되는 에러전압이 최종 출력에서 상쇄 됨을 확인 할 수 있다. 여기에서  $2N=N_{51}-N_{41}-N_{52}+N_{42}$

$$V_{OUT} = \left(\frac{C_S}{C_H}\right) \left[-2^{n+1} V_{IN} + 2NV_{REF}\right]$$

(10)

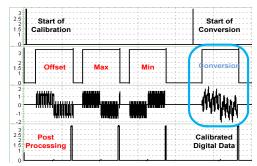

나. 디지털 교정 기법

추가적인 디지털 프로세싱으로 ADC 시스템에서 발생하는 오프셋 및 이득 에러를 교정해 줄 수 있 다.[4-7]

이 논문에서 사용된 기법은 다음과 같으며, 세 가 지의 데이터를 필요로 한다.

첫 번째, 시스템 오프셋을 교정하기 위한 데이터로 ADC가 동작을 할 때, 내부에서 자동적으로 입력 전압 0을 인가하게 된다. 이 때 내부 신호(Zero)와 함께 디지털 값을 내보내게 되며, MCU에서는 Zero Data를 저장 해 놓게 된다. 두 번째, 이득 에러를 교정하기 위한 데이터로 입력 전압을 최대값 및 최소값을 인가하게 된다. 이 때 출력 신호들(Max, Min)과 함께 디지털 코드를 내보내게 되며, MCU에서 Max Data

Table 1. Processing of the MCU 표 1. MCU 연산 과정

| Zero Data  | Zero 신호와 함께 출력된 데이터          |

|------------|------------------------------|

| Max Data   | Max 신호와 함께 출력된 데이터           |

| Min Data   | Min 신호와 함께 출력된 데이터           |

| Old Data   | 외부 입력에 대한 출력 데이터             |

| Data1      | Old Data - Zero Data         |

| Data2      | Max Data - Min Data          |

| Final Data | Data1×2 <sup>16</sup> /Data2 |

및 Min Data를 저장 해 놓게 된다. 이렇게 저장 된데이터는 미리 입력 해 놓은 연산에 따라 수행하게되고, MCU에서는 교정된 최종 데이터를 얻게 된다. 미리 입력 해 놓은 연산 과정 및 최종적으로 얻는 데이터는 표.1과 같다. 아래 그림 4-5는 아날로그 보상기법 및 디지털 교정 기법에 대한 시뮬레이션 파형이다. 그림 4는 아날로그 보상 기법에 대한 파형을 보여주며, 첫 번째, 두 번째, 세 번째 구간에 맞는 Positive, Charge Inverting, Negative 구간을 나타나고 있다. 그림 5는 디지털 교정 기법에 대한 파형으로 표 1의 출력 및 저장의 연산과정을 나타내고 있다.

Fig. 4. Waveform of Analog Compensation 그림 4. 아날로그 보상 기법 결과 파형

Fig. 5. Waveform of Digital Calibration 그림 5. 디지털 교정 기법 결과 파형

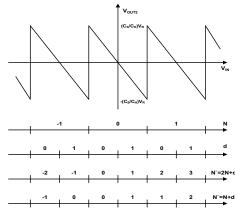

#### 다. 최하위 비트 교정 기법

Integrating sigma-delta ADC의 정확성을 올리기위해 최하위 비트 교정 기법을 제안하였다. 하나의데이터에 대한 변환이 끝났을 때의 적분기 출력은 식(11)과 같으며, 그림 6은 적분기 입력에 따른 적분기 출력의 관계를 나타내는 그림이다.

$$V_{OUT} = \left(\frac{C_S}{C_H}\right) \left[-2^{n+1} V_{IN} + 2N V_{REF}\right]$$

(11)

Fig. 6. Method of LSB Calibration 그림 6. 최하위 비트 교정 방법

그림 6의 첫 번째 줄의 N은 올림/내림 계수기에서 연산을 마친 출력 값을 나타내고, d는 적분기의 출력에 따른 부호를 나타내고 있다. 식(11)에서 알 수 있듯이 올림/내림 계수기의 총 계산 횟수는  $2N = 2^{N+1}$ 이다. 하지만, 실제적으로 올림/내림 계수기가 계산을하는 횟수는 반전 구간 및 초기화 구간을 제외한  $2^{N+1}$ -2의 횟수가 된다. 이러한 계산 과정에서 발생하는 에러를 제거하기 위해 적분기의 입력과 출력에 관계로부터 최하위 비트를 교정 하였다.

기존의 방법은 그림 6의 세 번째 줄과 같다. 이는 올림/내림 계수기로부터 나온 출력에서 적분기 출력의 극성에 따라 교정을 해줘서 n+1bit의 해상도를 얻을 수 있는 것을 보여준다. 하지만, 본 논문에서는 올림/내림 계수기를 사용함으로써 부호 비트 결정이 간편해지는 것을 바탕으로 그림 6의 네 번째와 같이 교정을 해주었다. 올림/내림 계수기에서 나오는 출력을 2로 나눈 뒤, 적분기의 출력의 극성으로 교정을 해주는 방법으로 n+1(부호 비트 + 크기 비트)bit의 해상도를 얻을 수 있다.

그 결과, 아날로그-디지털 변환기의 bit수에 해당되는 모든 디지털 출력 값을 얻을 수 있었고, 이로써 향상된 해상도를 얻을 수 있었다.

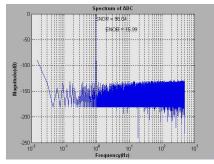

성능을 비교하기 위해 두 가지 방법에 대해 FFT 시뮬레이션을 수행하였고, 그림 7-8은 FFT 시뮬레이션 결과를 나타낸 그림이다. 기존의 경우에는 97.24dB의 SNDR 결과를 보였으며. 제안된 방법의 경우에는 98.04dB로 기존에 비해 향상된 결과를 얻을 수 있었다.

Fig. 7. Conventional Simulation Result 그림 7. 기존 방법의 시뮬레이션 결과

Fig. 8. Proposed Simulation Result 그림 8. 제안된 방법의 시뮬레이션 결과

# Ⅲ 결론

본 논문에서는 새로운 방법의 최하위 교정 기법을 제안하였다. Integrating sigma-delta ADC에서는 절대 정확도 향상을 위해 최하위 비트를 교정하는 방법이 들어가야 한다. 기존의 방법에는 전체 구간 중, 반전 구간 및 초기화 구간에서의 입력에 대한 가/감산에 대한 연산을 하지 않음으로써의 오차가 발생을 하게 된다. 해상도가 증가할수록 입력에 대한 연산의수가 증가하여 반전 구간 및 초기화 구간에 대한 비중이 줄어들어 오차가 줄어들어 무시를 하였다. 하지만, 본 논문에서는 연산을 하지 않는 구간으로부터 발생하는 에러 값 교정 기법을 사용하여 기존에 비해향상된 결과 검증을 하였다.

## 참고문헌

[1] J. Robert, G. C Temes, V. Valencic, R. Dessoulavy, and P. Deval, "A 16-Bit low-voltage CMOS A/D converter" *IEEE J. Solid-State Circuit*, vol. SC-22, pp 157-63, 1987

- [2] J. Robert and V. Valencic, "Offset and charge injection compensation in an incremental analog-to-digital converter" in Proc. European Solid-State Circuits Conf. (Toulouse, France), pp. 45–48. Sept. 1985.

- [3] J. Robert, G. C. Temes, F. Krummenacher, V. Valencic, and P. Deval, "Offset and clock-feedthrough compensated switched-capacitor integrators" *Electron. Lett*, vol.21, pp. 941–942, Sept. 26, 1985

- [4] K. S. Tan, S. Kiriaki, M. De Wit, J. Fattaruso, C. Y. Tsay, W. Matthews, and R. Hester, "Error correction techniques for high-performance differential A/D converters" *IEEE J. Solid-State Circuit*, vol.25, pp 1318–1327, 1990

- [5] G. Azzopardi, I. Grech, J. Micallef, and F. Maloberti "A Low Voltage High Resolution Pipelined Incremental ADC" *IEEE Electronics, Circuit and System Int. Conf.* vol.3, pp 1499–1502, 1999

- [6] P. C. Maulik, M. S. Chadha, W. L. Lee, P. J. Crawley "A 16-Bit 250-kHz Delta-Sigma Modulator and Decimation Filter" *IEEE J. Solid-State Circuit*, vol.35, pp. 458-467, April, 2000 [7] T. Ndjountche, F. L. Luo, R. Unbehauen "A High-Frequency Double-Sampling Second-Order Delta Sigma Modulator" *IEEE Trans. Circuit and Sys. II*, vol.52, pp 841-845, Dec, 2005

#### 저 자 소 개

#### 박 철 규 (학생회원)

2010년: 서울시립대학교 전자전 기컴퓨터공학부 학사졸업 2012년: 서울시립대학교 전자전 기컴퓨터공학과 석사졸업 2012년 3월 ~ 현재: 서울시립대 학교 대학원 전자전기컴퓨터공학 과 박사과정

<주관심분야> Analog IC Design Power Management IC Design

## **장 기 창** (비회원)

2007년 : 서울시립대학교 전자전 기컴퓨터공학부 학사졸업 2009년 : 서울시립대학교 전자전 기컴퓨터공학과 석사졸업 2011년 3월 ~ 현재 : 서울시립대 학교 대학원 전자전기컴퓨터공학 과 박사과정

<주관심분야> Analog IC Design Power Management IC Design

# **우 선 식** (비회원)

2011년: 서울시립대학교 전자전 기컴퓨터공학부 학사졸업 2011년 3월 ~ 현재: 서울시립대 학교 대학원 전자전기컴퓨터공학 과 석사과정 〈주관심분야〉 Analog IC Design Power Management IC Design

## **최 중 호** (정회원)

1987년 : 서울대학교 전자공학 학

사졸업

1989년 : 서울대학교 전자공학 석

사졸업

1993년 : University of Southern California 전기공학 박사졸업 1996년 ~ 현재 : 서울시립대학교

전자전기컴퓨터 공학부 정교수

<주관심분야> BB-AFE(Filter, ADC, DAC..)

PMIC(DC-DC Converter, PFC, LLC, LED Driver)

BMIC(ADC, Protection)

EMIC(DC-DC Converter)