# FPGA를 이용한 공간벡터 변조 PWM 및 디지털 제어부의 System On Programmable Chip 설계

논 문 61P-1-10

# Design of Space Vector Modulation PWM and Digital Control of System On Programmable—Chip Using FPGA

황 정 원\*·김 승 호\*\*·양 빈\*\*·이 천 기\*\*\*·박 승 엽<sup>†</sup> (Jeong-won Hwang·Seung-ho Kim·Bin Yang·Seung-yub Park)

Abstract - This paper presents implementation of SVPWM technique for three phase Voltage Source Inverter using FPGA. Software-based vector-control calculations much this drawback, in order to improve the hardware-vector-control tries. Without the need for additional software, vector control algorithm is designed to be modular SOPC, and DSP will reduce most of the operations. In this paper, the SVPWM that using HDL for the AC motor vector control algorithm level, and the dead time part and the speed control in order to controled a speed detector and designed in the form of modules. Then ALTERA corporation Cyclone III series EP3C16F484 can be verified by implemented.

Key Words: FPGA, SVPWM, PWM, VHDL, One chip, SOPC

#### 1. 서 론

현대의 제어기법은 전동기 시스템에서 디지털화된 알고리즘을 DSP를 이용하여 소프트웨어적으로 제어기를 구성하게됨으로써 고속, 고성능의 연산 및 제어오차를 줄일 수 있지만, 소프트웨어 기반 벡터제어 알고리즘은 긴 연산 수행기간을 요구하므로 고성능의 마이크로프로세서가 필요하다[1].특히, 교류 전동기의 제어를 위한 필요한 제어 알고리즘은 행렬이나 삼각 함수 연산이 다수 포함되어 복잡한 연산과정이 요구된다[2]. 이러한, 벡터제어 알고리즘을 소프트웨어로구현하기 위해 고성능 DSP나 마이크 컨트롤러의 사용은 제어기 설계에 있어 상당한 시간을 소프트웨어 공정으로 소모하고, 적용 시스템에 따라 새로운 소프트웨어가 필요하므로시간적 소모가 많다.

이러한 소프트웨어 기반의 벡터제어의 단점을 개선하기 위해 본 논문에서는 하드웨어적으로 벡터제어 알고리즘을 모듈화하여 FPGA(Field Programmable Gate Array)에 SOPC(System on Programmable Chip)로 구성하고자 한다. 이러한 방법은 DSP의 연산량을 최대한 줄이고, 제어 알고 리즘에서 공간벡터변조(SVPWM, Space Vector PWM) 및 속도검출에 필요한 알고리즘들이 하드웨어로 대체 되므로 소프트웨어적으로도 간단한 설계가 되므로 개발 시간도 단 축이 된다.

본 논문에서는 HDL(Hardware Description Language)을 이용하여 알고리즘 레벨에서 교류전동기의 벡터제어를 위한 SVPWM, 데드타임부 등과 속도제어를 위한 속도 검출부 등을 모듈화 하여 설계한 후 ALTERA사의 CyclonⅢ Series 인 EP3C16F484에 SOPC형태로 구현 하여 검증하고자 한다.

#### 2. 기존의 벡터제어 시스템 및 속도 검출

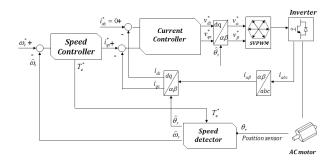

그림 1은 일반적인 교류전동기 구동 시스템의 전체 구성 도이다. 그림 1과 같이 일반적인 교류 전동기 구동 시스템의 필수 요소는 크게 속도검출부, 속도제어부, 전류제어부, 인버 터부로 구분할 수 있다. 속도검출부는 위치 센서로부터 받은 위치/속도 정보를 검출하여, 제어가 가능한 신호를 만들어 속도제어에 필요한 정보를 전달하고, 속도제어부와 전류제어 부는 주로 DSP와 디지털 로직 IC로 구성되며 속도 제어와 전류 제어에 필요한 연산을 수행하고 이에 따라 발생할 PWM 신호를 만들어 인버터에 전달한다. 인버터에서는 최 적 PWM, 삼각파 비교 PWM, SVPWM 등을 통해 구현할 수 있으며, 그 중 SVPWM 기법은 다른 방식에 비해 직류 링크 이용률이 높고, 고조파 왜형을 줄일 수 있는 장점이 있 으나 연산이 복잡하고 연산시간이 오래 걸리므로, 일반 프로 세서보다는 고속 프로세서를 이용할 경우 적합한 방식이다. SVPWM 개념은 2차원 공간상의 임의의 공간벡터 즉, 출력 전압이나 출력 전류 벡터를 7개의 가능한 특정 벡터 중 임 의의 벡터와 인접한 두 개의 공간벡터와 그 벡터를 유지하 는 시간을 나타내는 가중치와의 곱으로 표현하는 것이다 [2][3].

E-mail : psy@changwon.ac.kr 접수일자 : 2011년 11월 28일 최종완료 : 2012년 1월 4일

<sup>\*</sup> 정 회 원 : 마산대학교 전기과 교수

<sup>\*\*</sup> 정 회 원 : 창원대학교 전자공학과 박사과정

\*\*\* 준 회 원 : 창원대학교 전자공학과 석사과정

† 교신저자, 정회원 : 창원대학교 전자공학과 교수

그림 1 일반적인 교류전동기 구동 시스템

Fig. 1 Typical AC motor driver system

#### 2.1 공간벡터 변조법

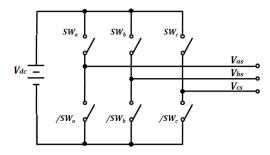

전압형 인버터의 간략화 된 모양은 그림 2와 같으며, 큰 직류전압을 스위칭 하여 개루프 교류전압을 만들어 내거나 폐루프로 원하는 교류전류를 공급할 수 있다.

그림 2 PWM 전압형 인버터

Fig. 2 PWM voltage source inverter

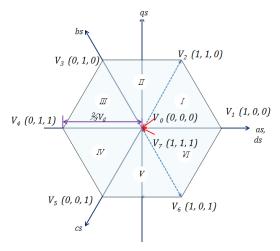

그림 3 2차원 공간에서의 인버터 전압벡터

Fig. 3 Inverter voltage vector of 2-D space

PWM 전압형 인버터에 있어서 요구되는 공간전압벡터  $V_{

m s}$ 는 식(1)과 같이 표시된다.

$$V_s(t) = \frac{2}{3} [v_{as}(t) + av_{bs}(t) + a^2 v_{cs}(t)] \tag{1}$$

여기서  $v_{as}, v_{bs}, v_{cs}$ 는 각각 a, b, c상의 상 전압을 나타낸다. 임의의 공간전압벡터는 인버터를 통해 곧바로 실현될 수는 없고 인버터의 스위칭을 통해 얻을 수 있는 6개의 출력전압 벡터와 2개의 무효벡터 즉, 스위치가 모두 1이거나 0인 상태를 조합하여 근사적으로 얻어낸다.

전압원 인버터의 출력 전압 벡터는 각 인버터 암의 온/오 프 상태에 따라 결정되는데, 논리'1'은 상위 스위치가 온, 논 리'0'은 하위 스위치가 온 일 때를 의미한다.

그림 3은 60°간격으로 공간적으로 배치되어 있는 6개의 2차원 공간에서의 유효 인버터 전압벡터이다.  $V(1)\sim V(2)$ 와 2개의 영 전압 벡터 V(0), V(7)이 이루는 고정 프레임 평면상에 중첩되어 나타나 있다[4]. 여기서 인버터를 통해 선간에 인가할 수 있는 전압은  $V_{dc}$ 이므로 3상이 모두 여자 되는 6개의 유효벡터( $V(1)\sim V(6)$ )는 한 상에 절대치로  $2/3V_{dc}$ 가 걸리고 나머지 두 상에는  $1/3V_{dc}$ 가 인가된다. 즉, 회전하는 기준벡터  $V^*$ 는 인버터 스위칭 상태의 조합으로 얻을 수있는 8개의 전압벡터이다.

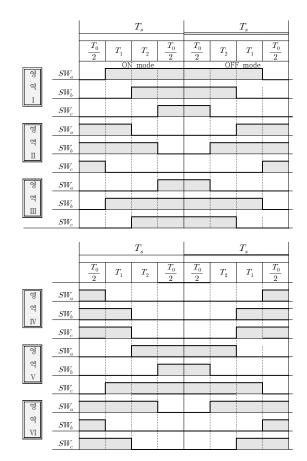

그림 4 3상 대칭변조법의 스위칭 패턴

Fig. 4 Switching pattern of symmetrical 3-phase modulation

SVPWM에 의해 계산된 전압패턴을 전동기에 인가하면, 3상의 PWM펄스가 공간벡터와 유기적인 결합으로 스위칭을 행하므로, 스위칭 횟수를 줄일 수 있다[4]. SVPWM 기법은 두 전압벡터를 시간적인 평균으로 합성한 지령전압에 해당

하는 출력전압벡터를 말하며, 이를 수행하는 과정에서 인버터의 각 스위치는 한 샘플링주기에 한 번씩만 온 되거나 오프 된다. 3상 대칭 변조는 대칭 PWM 패턴주기를 가지도록 영 전압벡터를 스위칭주기  $T_s$ 의 처음과 마지막에  $T_0/2$ 씩 분할하여 설정하는 방식이다.

3상 대칭 변조법의 스위칭패턴을 도시하면 그림 4와 같다. 한 주기에 한 번씩 온/오프가 이루어져야 하므로 영역 I, III, V에서는 영 전압벡터  $V_0$ 를 먼저 인가하고, 영역 II, IV, VI에서는  $V_2$ 을 먼저 인가한다.

식 (3)은 영역 I의 지령전압  $V^*$ 를 발생하기 위하여 인가하는 전압벡터를 식으로 표현하면 식(2)와 같다.

$$T_s V^* = \frac{T_0}{2} V(0) + T_1 V(1) + T_2 V(2) + \frac{T_0}{2} V(7)$$

(2)

3상 변조는 스위치 2개가 동시에 스위칭 되지 않고 각각하나씩 스위칭 되며,  $T_{sw}$ 가  $T_s$ 의 2배가 되고, 2상 변조와 달리  $T_{sw}$ 내에서 영 전압 벡터를  $V_0, V_7$ 를 교번 하여 사용한다. 그리고, SVPWM에 의해 계산된 전압 패턴을 전동기에 인가하면, 3상의 PWM펄스가 공간 벡터와 유기적인 결합으로스위칭을 행하므로, 스위칭 횟수를 줄일 수 있다[4].

#### 2.2 M/T method를 사용한 속도 검출 방법

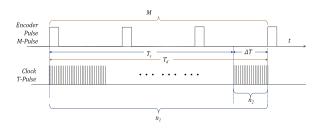

M/T method를 사용하여 속도 검출 하는 방법은 엔코더의 시작 필스와 끝 필스를 동기 시켜 속도를 계산한다. 이것은 다소 복잡한 회로와 연산을 필요로 하지만, 저속에서 고속까지 거의 일정하고 높은 정밀도를 갖는 속도 값을 얻을수 있다. 그림 5에 M/T method를 사용한 속도측정의 원리를 보였다. M/T method를 사용할 때 측정시간  $T_d$ 는 엔코더 필스와 동기가 되도록 결정하고 이는 하드웨어적으로 또는 소프트웨어적으로 쉽게 구현가능 하다.

속도 측정의 기본원리는 엔코더 펄스 수 M과  $\Delta T$ 시간 동안의 클럭 수  $n_2$ 으로 각각 회전 각도와 시간  $T_d$ 를 알 수 있고 이 값을 이용하여 속도를 측정할 수 있다. 이때 M-pulse를 세기 위한 Mcounter와 T-pulse를 세기 위한 Tcounter가 필요하다. 그림 5는 M/T-method를 이용하여 속도를 검출하는 방법이다.

그림 5 M/T-Method를 이용한 속도 측정

Fig. 5 The speed measurement which uses M/T-Method

M/T-method를 이용하여 속도를 계산하는 식은 식(3)과 같이 계산된다.

$$\omega = \frac{\Delta\Theta}{T_d} = \frac{2\pi \cdot M}{T_t \cdot n_1 \cdot N_{pulse}} [rad/s]$$

(3)

여기서,  $\Delta\Theta$  는 계산되는 각도 차이고,  $T_d$  는 속도 측정시간,  $T_t$  는 기준 주파수 입력이고, M 과  $N_{pulse}$ 는 각각  $T_d$  동안의 엔코더 펄스수와 전동기 1회전 당 출력되는 엔코더 펄스 수이다.  $n_1$ 은  $T_d$  동안의 기준 주파수의 클럭 수이이다. (3)식을 본 논문에서 적용하는 엔코더 펄스의 4체배회로가 포함된 경우는 식(4)와 같이 속도가 계산된다.

$$\omega = \frac{\pi \cdot M}{2T_i \cdot n_1 \cdot N_{milse}} [rad/s] \tag{4}$$

#### 2.3 Dead Time

공간 전압 벡터 PWM 방법에서는 계산된 스위칭 함수에 따라 인버터의 각 스위치  $Sw_a$ ,  $Sw_b$ ,  $Sw_c$  를 구성하는 위, 아래의 전력용 반도체 소자가 각각 온/오프 할 때 서로 상보형으로 동작한다. 그러나, 이들 스위칭 소자가 이상적으로 동작한다면 정확히 지령전압에 해당하는 출력 전압을 발생하지만, 일반적으로 스위칭 소자는 턴 오프(turn-off) 시간이턴 온(turn-on) 시간 보다 길기 때문에 인버터의 스위치  $Sw_a$ ,  $Sw_b$ ,  $Sw_c$  를 각 각 상보형으로 동작시키면 3상 인버터스위치의 각 래그(leg)를 구성하는 위, 아래의 스위치가 동시에 온 상태로 되어 순간적인 전원 단락이 발생할 수 있다. 따라서 인버터의 각 스위치를 스위칭함수에 따라 온/오프할 때는 순간적 단락이 발생하지 않도록 먼저 위, 아래의 스위치를 모두 일정한 시간동안 오프 시켜야 하는데 이 시간을 데드타임이라하며  $T_{Dc}$ 로 표시한다.

#### 3. 제안된 SOPC의 구현 기법

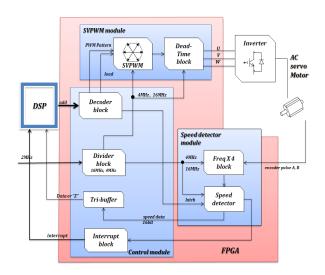

연산 시간의 단축을 위해 본 논문에서는 DSP가 담당하는 전류 제어에 관련된 부동 소수점 수학 연산을 제외한 나머지 디지털 연산을 SOPC로 구현함으로써 DSP의 연산량을 최소화 시키고자 한다. 이러한 원-칩화는 전동기 제어 보드의 하드웨어 설계 시 회로의 구성을 단순화하는 장점도 있다[5][6][7].

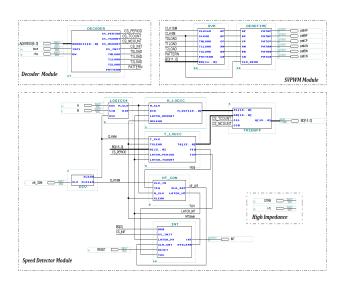

본 논문에서는 크게 세 부분으로 나누어 설계하였다. 제어 모듈은 DSP와 정보 교환과 속도검출이나 SVPWM제어 패턴을 출력하기위한 제어신호를 디코딩하는 Decoder 와 제어에 필요한 여러 시점을 만들어 내는 주파수 분주회로, DSP 인터럽트 처리를 위한 인터럽트 제어기 등이 포함되어 있다. SVPWM module 은 SVPWM 패턴을 구성하고 있고, 마지막으로 속도 검출을 위한 Speed detector 모듈 로 구분하여 설계하였다. 그림 6은 SOPC기법이 적용된 교류전동기구동 시스템 블록도이다.

그림 6 SOPC로 구현한 교류전동기 구동 시스템 Fig. 6 AC motor driver system with SOPC

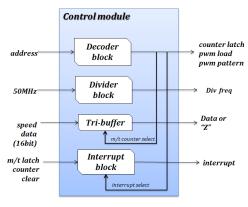

#### 3.1 Control 모듈

제어 모듈에서는 속도 검출과 분주, 인터럽트 처리를 위 한 블록으로 DSP의 어드레스 신호에 따라 제어신호를 생성 하는 디코더 블록으로 나누어 설계하였다. 디코더 블록 (Decoder block)은 특정 어드레스 신호가 들어오면 엔코더 출력펄스인 M pulse와 기준이 되는 주파수 T pulse 세는 신호를 인가하고, SVPWM에 패턴 나가는 시점을 제공하는 블록이고, 분주 블록(Divider block)은 속도 검출을 하기 위 해서는  $T_{\rm e}$ 를 세는 기준 클럭과 속도 4체배에 필요한 클럭이 필요하다. 입력 클럭을 50Mb를 사용하므로 이것을 분주하여 속도 검출에 필요한 클럭을 만드는 블록이다. 그리고, 카운 터의 정보를 가지고 어드레스에 따라 엔코더 펄스 래치 값 과 기준 클럭 래치값을 선택적으로 DSP로 보내어 값을 전 달하는 3상 버퍼와 T,가 끝날 때마다 DSP에서 속도 연산 을 인터럽트로 처리하도록 인터럽트 발생 블록으로 나누어 설계 하였다. 그림 7은 제어 모듈에 대한 신호처리 블록도 이다.

그림 7 제어 모듈의 블록도

Fig. 7 Block diagram of control module

#### 3.2 SVPWM 모듈

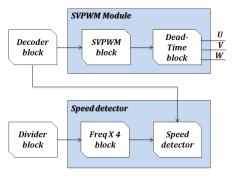

그림 8은 본 논문에서 설계한 SVPWM모듈과 속도 검출의 블록도이다. SVPWM모듈은 SVPWM패턴을 생성하는 블록과 데드타임 블록(dead time block)으로 나누어 설계 하였다

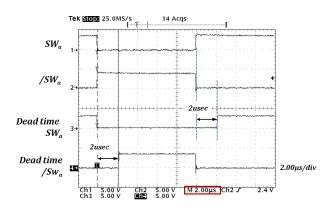

본 논문에서는 여러 가지 면에서 우수한 특성을 보이는 3상 대칭 변조를 구현하였다. 3상 대칭 변조를 행함으로 대칭 출력 전류를 기대할 수 있어 제어 및 추정 알고리즘 수행시 이용되는 전류, 전압에 대한 정현성을 뒷받침해 준다. 하지만 실제 SVPWM 적용 시 스위칭 주기마다 4회의 패턴 변경을 요구하므로 이에 따른 수행 시간의 손실과 구현상의 번거롭다는 문제점이 있다. 그리고, DSP에서 스위칭 주기를 계산하여 ON/OFF 시간이 결정되면 VHDL로 설계된 FPGA에서 그림 4와 같은 패턴을 형성하여 정해진 패턴 순서대로 출력하도록 하여 구현상의 문제점을 극복하였다. 데드타임 블록은 SVPWM 에서 나오는 신호가 상승 에지 일때,  $T_{De}$ 지연 후에 데드타임 파형을 출력하고, 하강 에지 일때는 그대로 출력한다. 본 논문에서는  $2\mu$ S의 데드타임을 제공한다.

그림 8 SVPWM 모듈과 속도 검출 블록도

Fig. 8 Block diagram of SVPWM module and Speed detector

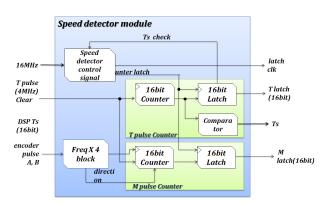

#### 3.3 Speed detector 모듈

증분형 로터리 엔코더는 회전속도 뿐 만 아니라 회전방향을 검출할 수 있도록 90도의 위상차를 갖는 A, B상 두 개의 출력을 가지고 있으며, 대부분의 경우 위치검출에도 사용할수 있도록 1회전 당 1개의 펄스를 발생하는 Z상의 출력도 갖고 있다.

M/T-method는 엔코더의 시작 펄스와 끝 펄스를 동기 시켜 속도를 계산한다. 이것은 다소 복잡한 회로와 연산을 필요로 하지만, 저속에서 고속까지 거의 일정하고 높은 정밀도를 갖는 속도 값을 얻을 수 있다. 따라서 본 논문에서 는 이방법을 이용하여 속도를 검출한다. 속도 검출 모듈에서는 엔코더 정보를 더 정밀하게 이용하기 위한 체배 회로, 속도검출을 하기위해 펄스 카운터 회로와 제어신호를 만드는 블록으로 구성된다. 4체배 블록에서는 속도에 대한 정밀 정보와특히 저속에서의 펄스의 손실을 막기 위해 펄스를 4체배 하여 펄스 수를 4배로 늘려 상승, 하강 에지 모든 정보를 이용하여 보다 정확한 속도 계산이 이루어지도록 하였다. 방향판별에서는 4체배 한 펄스 몇 개를 지나서 방향 판별을 하

므로 그릇된 방향판별이 있을 수 있으나, 본 논문에서는 정 방향과 역방향의 패턴 인식을 통해 방향이 바뀔 때마다 방 향판별신호를 정확하게 출력되도록 설계 하였다.

그림 9 속도검출 모듈의 블록도

Fig. 9 Block diagram of speed detector module

그림 9은 속도 검출 모듈에 대한 블록도이다. 속도검출 블록에서 M\_pulse counter는 비동기 리셋으로 동작하며, 엔코더 필스를 4체배 한 필스가 들어올 때마다 카운터 값을 증가시키고, 속도검출에 필요한 제어신호를 만드는 블록에서 latch 신호의 상승 에지 일 때, 그 값을 래치하여 16bit 래치에 저장한다. 원래 M/T 속도검출 방법에서  $T_s$ 시간 후부터다음 엔코더 펄스가 나타나는 시간까지 세어  $\Delta T$ 시간을 하지만. 본 논문에서는 처음부터 카운터 하여 DSP의 data와비교하여  $T_s$ 시간이 되었음을 알리는 신호를 만들고,  $T_d$ 시간 즉,  $T_s + \Delta T$ 까지 카운터하고, 제어신호가 상승 에지 일때, 카운터 값을 latch 하도록 설계 하였다.

제어신호 블록은 속도 검출에 필요한 제어신호를 만드는 블록으로써, 50Mb 입력을 받아 분주하여 기준 신호  $T_s$ 가 되었음을 알리는 신호가 들어오면 클럭에 동기 시켜 처리고, 16bit latch 시점을 제공한다.

#### 5. 시뮬레이션 및 실험결과

본 논문에서는 설계된 속도검출 및 공간벡터 변조 모듈을 ALTERA사의 저가형 모델인 CyclonIII Series EP3C16F484를 이용하여 구현하였다. EP3C16F484는 15,408개의 LE(Logic Element)를 가지고 56M9K Embedded Memory Blocks, 504K total RAM bits , 56 embedded multipliers , 4 PLLs , 347 user I/O pins을 가진 FineLine BGA 484-pin package 이다[9]. SRAM을 이용하는 휘발성 소자 이므로, 최종적으로 로직회로가 완성되면 Configuration EPROM 같은 비휘발성 소자에 구현을 한다.

그림 10는 실제 FPGA에 설계된 전체 시스템 회로이다. 전제 15,408개의 LE중 1,302개를 사용하여 8.45% 사용률과 전체 592개의 레지스터가 사용되었다. 표 1은 구현된 벡터제 어기의 사양을 나타낸다.

그림 10 실제 FPGA에 설계된 전체 시스템

Fig. 10 Designed the entire system in the actual FPGA

#### 표 1 벡터제어기 사양

Table 1 Design summary of the vector controller

| EP3C16U<br>484C6 | Resource | Used design | Ratio |

|------------------|----------|-------------|-------|

| LE               | 15,408   | 1,302       | 8.45% |

| Resister         | 15,408   | 592         | 3.84% |

| I/O pin          | 347      | 44          | 13%   |

그림 11은 4체배 및 방향 판별에 대한 시뮬레이션 파형으로 각 상의 상승에지, 하강에지마다 펄스 출력 되는 4체배된 파형과 정방향일 때 0, 역방향일 때 1로 출력되는 방향판별신호이다.

**그림 11** 4체배 및 방향 판별

(cos = A 상, sin = B 상, m\_clk : 4체배, dir : 방향 파벽)

Fig. 11 4 Multiple circuit and direction detector

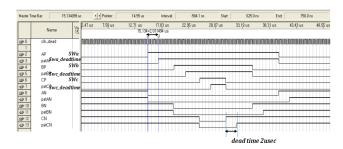

그림 12는 데드타임에 대한 시뮬레이션 파형이다. AP, BP, CP, AN, BN, CN는 SVPWM 패턴이고, patAP, patBP, patCP, patAN, patBN, patCN 은 데드타임 2 $\mu$ s 가 적용된 SVPWM 패턴이다. 하강에지에서는 신호가 그대로 출력되고, 상승에지에서면 2usec 지연된 파형이 출력이 된다.

그림 12 데드 타임 시뮬레이션 결과

Fig. 12 Simulation Result of Dead Time

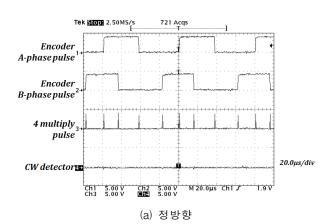

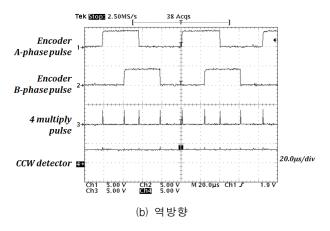

그림 13은 엔코더 펄스와 펄스를 4체배한 파형으로써, 모터의 회전 방향이 (a)는 정방향일 때, (b)는 역방향일 때이다. 상승에지와 하강에지에 맞추어 체배 파형이 잘 나타나고 있으며 방향 판별도 정확하게 된다.

**그림 13** 4체배 파형

Fig. 13 4 multiple wave

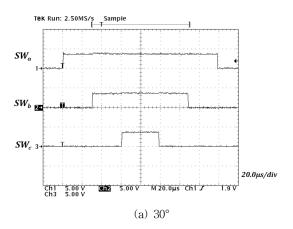

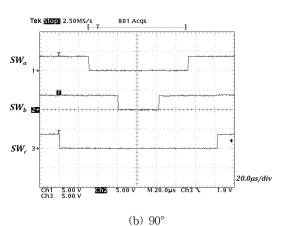

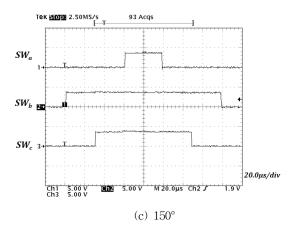

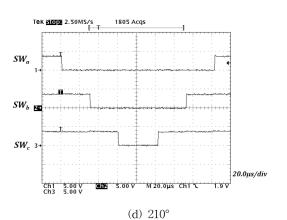

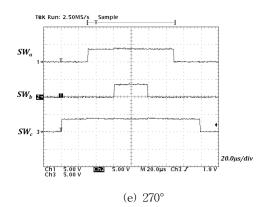

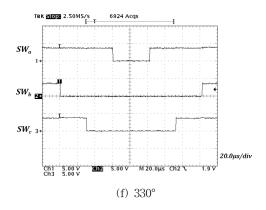

그림 14는 VHDL로 구현된 벡터제어기의 공간벡터의  $\mathbb{1}\sim \mathbb{6}$ 영역의 패턴으로써 정확하게 출력됨을 알 수 있다. 이때 각 벡터는 30°, 90°, 150°, 210°, 270°, 330°이고  $t_0=t_1=t_2$ 이다. 그림 4와 패턴이 일치한다.

그림 14 벡터 제어기를 통해 변조된 3상 대칭 변조의 패턴 Fig. 14 Pattern of 3-phasor symmetry modulation by vector controller

그림 15 데드타임 블록을 통과한 출력파형이다. 시뮬레이션 결과와 유사하게 데드타임를 통과한 파형이 상승 에지만 거의  $2\mu$ s 후 상승 에지가 나타나 정확한 데드타임이 적용 된다

**그림 15** Dead time 실험 결과

Fig. 15 Result of Dead time part

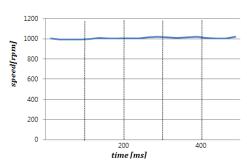

그림 16은 전동기가 시계 방향으로 회전 할 경우 실험결과로, 파형이 매끄럽지 못한 이유는 제어기법이 적용되지 않았기 때문이다. 이 결과는, 정상상태 응답일 때로, 지령속도 1000[rpm], 샘플링 타임은 1[ms]이다.

**그림 16** 속도 검출결과(1000rpm)

Fig. 16 Result of speed detection

표 2에서는 소프트웨어로 벡터제어 시스템을 구성했을 때와 SOPC 형태의 하드웨어 벡터제어 시스템의 연산 시간을 비교한 결과 이다. SVPWM모듈과 속도검출모듈을 모두 SOPC로 구현했을 때가 소프트웨어 만으로 구현했을 때보다 6배 정도 빠른 처리 속도를 보인다. 소프트웨어 벡터제어 시스템은 TMS320F28336 으로 구현하였다.

#### 표 2 소프트웨어 벡터제어 시스템과 SOPC 벡터제어 시 스템 비교

Table 2 Compare with SW vector control system and SOPC vector control system

| System       |                         | CPU Calculation time |                           |

|--------------|-------------------------|----------------------|---------------------------|

|              |                         | SVPWM                | SVPWM +<br>speed detector |

| only S/W     | F28336<br>(150MHz)      | 98.32ms              | 115.68ms                  |

| SW +<br>SOPC | EP3C16U484C6<br>(50MHz) | 24.02ms              | 18.53ms                   |

#### 6. 결 론

본 논문에서는 연산 시간의 단축을 위해 본 논문에서는 DSP가 담당하는 전류 제어에 관련된 부동 소수점 수학 연 산을 제외한 나머지 디지털 연산을 FPGA에 SOPC형태로 구현함으로써 DSP의 연산량을 최소화 시켰다. 그 결과, DSP의 많은 연산을 디지털 형태로 하드웨어가 부담하게 되 므로 연산 시간이 6배 이상 단축됨을 알 수 있다. 이러한 SOPC화는 전동기 제어 보드의 하드웨어 설계 시 회로의 구 성을 단순화하고, 제어 알고리즘에서 SVPWM 및 속도검출 에 필요한 알고리즘들이 제거 되므로 소프트웨어적으로도 간단한 설계가 되므로 개발 시간도 단축이 됨을 알 수 있었 다. 이러한 저전력, 고성능, 고효율성을 가진 FPGA 기술의 발전은 IP나 소프트 코어 기술로 FPGA 내 DSP를 설계하 고, 본 논문에서 제안된 속도검출, SVPWM 등 디지털 회로 들을 HDL로 설계하여 FPAG에 구현하면 외부 DSP 없이도 전동기 벡터제어 시스템 구동이 가능하고, 보다 완벽한 의미 의 SOPC를 구현 할 수 있을 것이다.

#### 참 고 문 헌

- [1] 설승기, "전기기기 제어론", 브레인 코리아, 2002

- [2] T. G. Habetler, "A Space Vector-Based Rectifier Regulator for AC/DC/AC Convertors", EPE Proc., Firenze, vol. 2, pp. 107–107, 1991.

- [3] Marian P.Kazmierkowski, "Novel Space Vector Based Current Controllers for PWM-Inverters", IEEE Trans, on Power ELEC, vol.6, no.1,1991 pp. 158-166.

- [4] 윤덕용 "공간전압벡터 PWM 기법을 이용한 영구 자석 형 동기 전동기의 속도제어". 1995

- [5] Ying-Yu Tzou and Hau-Jean Hsu, "FPGA realization of space vector PWM control IC for three phase PWM inverters", IEEE Trans. on Power Electronics, Vol.12, No.6, 1997, pp 953-963.

- [6] Zhaoyong Zhou, Tiecai Li, Toshio Takahashi and Edd Ho, "FPGA Realization of a High-performance Servo Controller for PMSM", Proceedings of APEC 2004, in press.

- [7] R.RAJENDRAN, N.DEVARAJAN, "FPGA Implementation of Space Vector PWM Technique for Voltage Source Inverter Fed Induction Motor Drive", 2009 Second International Conference on Computer and Electrical Engineering

- [8] W.P.Hew, et al, ""Realization of space vector modulation technique in a single FPGA chip for induction motor drive PWM,"" IEEE International Conference on Electron Devices and Solid State Circuits, Hong Kong, pp.817–820, Dec.2005

- [9] Altera, Cyclone III Device Handbook, Volume1" 2008.

## 저 자 소 개

#### 황 정 원 (黃 貞 苑)

1975년생. 1993년 인제대 전자공학과 졸업. 2012년 창원대 대학원 전자공학과 졸업(박사) 2011년~현재 마산대 전기과 전임강사

E-mail: likewori@masan.ac.kr

#### 김 승 호 (金 勝 浩)

1977년생, 2000년 7월 중국 연변대학교 응용 수학과 졸업, 2002년 9월~2006년 8 월: 중국 연길시 연변대학 사범분원 전임 강사, 2008년 9월~현재 창원대 전자공학 과 박사수료

#### 양 빈(楊 鑌)

1980년생, 2005년 7월 중국 요녕 과학기술대학교 전신학과 졸업, 2009년10월 ~ 2010년8월 Liaoning Julong Financial Equipment Corp.(중국) 선임연구원, 2010년9월 ~ 현재 창원대학교 전자공학과 박사과정

#### 이 천 기 (李 千 紀)

1984년 생, 2011년 2월, 창원대학교 전자 공학과 졸업, 2011년 3월 ~ 현재 : 창원 대학교 전자공학과 석사과정

### 박 승 엽 (朴 勝 燁)

1958년생. 1981년 고려대 전기공학과 졸업. 1988년 동대학원 전기공학과 졸업(박사). 1988년~현재 창원대 전자공학과 교수.

E-mail: psy@changwon.ac.kr