# Effects of Post Annealing on the Electrical Properties of ZnO Thin Films Transistors

Mi Ran Moon, Chee-Hong An<sup>1</sup>, Sekwon Na<sup>1</sup>, Haseok Jeon<sup>1</sup>, Donggeun Jung, Hyoungsub Kim<sup>1</sup>, Hoo-Jeong Lee<sup>1,\*</sup>

Department of Physics, Institute of Basic Science, and Brain Korea 21 Physics Research Division, Sungkyunkwan University, Suwon 440-746, Korea <sup>1</sup>School of Advanced Materials Science and Engineering, Sungkyunkwan University, Suwon 440-746, Korea

\*Correspondence to: Lee HJ, Tel: +82-31-290-7365 Fax: +82-31-290-7371 E-mail: hlee@skku.edu

Received November 29, 2012 Revised December 4, 2012 Accepted December 4, 2012 This paper reports the effects of post-annealing of ZnO thin films on their microstructure and the device performance of the transistors fabricated from the films. From X-ray diffraction and transmission electron microscopy characterization, we uncovered that the grain size increased with the annealing temperature escalating and that the film stress shifted from compressive to tensile due to the grain size increment. Electrical characterization revealed that the grain size increase damaged the device performance by drastically lifting the off-current level. By annealing the devices in an  $O_2$  ambient (instead of air), we were able to suppress the off-current while improving the electron mobility.

Key Words: ZnO, Thin-film transistor, Grain size, Electron mobility, Thin film stresses

### **INTRODUCTION**

Research interests on ZnO-based thin film transistors (TFTs) are on rise (Bae & Im, 2004; Fortunato et al., 2005; Yao & Li, 2005; Sun & Rogers, 2007). ZnO and its derivatives (InGaZnO, SnZnO, InZnO, etc) offer a unique combination of technologically important features such as a high electron mobility, an excellent transparency, and a stability superior to that of amorphous silicon (Normura et al., 2004). Successfully developing them for transistors could enable some nextgeneration electronics including transparent electronics and flexible electronics. Vigorous research activities are in progress in harnessing this class of materials as the channel layer of TFTs to achieve a high device performance. In particular, understanding the fundamentals of these materials and its influence on the device performance is an integral part of these research efforts (Bae et al., 2003; Carcia et al., 2003; Hoffman et al., 2003; Norris et al., 2003). For instance, ZnO

thin films are typically polycrystalline and the electrical properties of the transistors based on these films are expected intimately related to their microstructural features such as grain boundaries (Hossain et al., 2003). Here, we annealed ZnO films to modulate the microstructure, and examined the effects of the annealing on the microstructure of the ZnO films and the electrical properties of their transistors. Among various deposition methods, radio frequency (RF) magnetron sputtering technique is widely adopted owing to its process simplicity and wide-area deposition capability (Hwangbo et al., 2008; Kim et al., 2008; Sahu et al., 2008; Venkatachalam et al., 2008). The microstructure of sputtered ZnO films are known very sensitive with the process conditions (such as deposition power, partial oxygen pressure, and post-deposition annealing) and hence the device performance (Levinson et al., 1982). Fortunato et al. (2005) reported the effects of the RF power on the crystallinity and Hall mobility of ZnO films while other studies embarked

This work was in part supported by the Korea Research Foundation Grant funded by the Korean Government (MEST) (KRF-2008-005-J00702). This research was also financially supported by the Ministry of Knowledge Economy (MKE) and Korea Industrial Technology Foundation (KOTEF) through the Human Resource Training Project for Strategic Technology.

<sup>©</sup> This is an open-access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted noncommercial use, distribution, and reproduction in any medium, provided the original work is properly cited. Copyright © 2012 by Korean Society of Microscopy

on the effects of the partial oxygen pressure during the deposition and post-annealing in hydrogen environment (Bae et al., 2003; Carcia et al., 2003). In our previous study, we employed different RF powers to generate ZnO films with different grain sizes and demonstrated a sensitive increase of the electron mobility with the grain size (Hwang et al., 2008). Despite the efforts to elucidate the role of the microstructure, the effects of post annealing - the most widely-used way of altering the microstructure of polycrystalline films - on the device performance have not been thoroughly investigated. Here, we annealed ZnO films at various temperatures under different ambients (air and  $O_2$ ) and delved into how the annealing affected the overall microstructure of the ZnO films and furthermore the electrical properties of the TFTs.

## MATERIALS AND METHODS

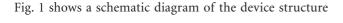

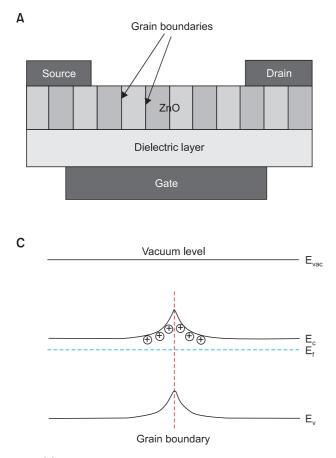

Fig. 1. A schematic diagram of the device structure used in this study.

adopted in this study, which is based on a bottom-gated TFT structure and utilizes a highly doped Si substrate as the gate electrode. First, SiO<sub>2</sub> gate dielectric with the thickness of 100 nm was thermally grown on a highly-doped p-Si (100) wafer (0.001~0.005  $\Omega$ cm), followed by deposition of an undoped ZnO active layer in an Ar ambient of 10 mTorr in a RF (13.56 MHz) magnetron sputtering system. The substrate temperature was room temperature and the sputtering power was set to 50 W. The ZnO films were deposited through a shadow mask having a size of 500×1,140  $\mu$ m to define the active channel regions.

After the deposition of ZnO films, thermal annealing was performed at various temperatures ( $300^{\circ}$ C,  $400^{\circ}$ C, and  $500^{\circ}$ C) in different ambients (air and O<sub>2</sub>) for 1 hour in a furnace. As the source and drain electrodes of the transistors, Al films were deposited using a thermal evaporation system and patterned using a typical lift-off process. The channel width (W) and length (L) of the fabricated TFTs were 100 µm and 50 µm, respectively. To reduce the contact resistance, rapid thermal annealing was carried out at 200°C for 2 min in N<sub>2</sub> ambient. The electrical characteristics of the transistors were measured using an Hewlett-Packard (HP) semiconductor parameter analyzer (HP4145B). We conducted microstructure analysis on the deposited ZnO films using X-ray diffraction (XRD) and transmission electron microscopy (TEM).

### **RESULTS AND DISCUSSION**

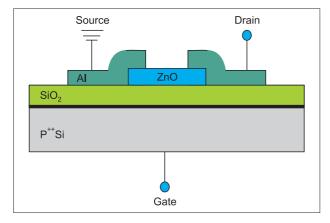

Shown in Fig. 2A are XRD curves obtained from ZnO films, as-deposited and annealed at various temperatures (300°C, 400°C, and 500°C). For all the samples, the XRD curves show the dominant peak around 34.3°, the position of which is coincident with that of the (0002) reflection of the hexagonal ZnO phase. This result represents the presence of a strong

**Fig. 2.** (A) XRD data obtained from  $\theta$ -2 $\theta$  scans for ZnO films, as-deposited and annealed at various temperatures (300~500°C), and (B) a graph of ( $d_{film}$ - $d_{bulk}$ )/ $d_{bulk}$  and biaxial stresses for the as-deposited and annealed samples. XRD, X-ray diffraction.

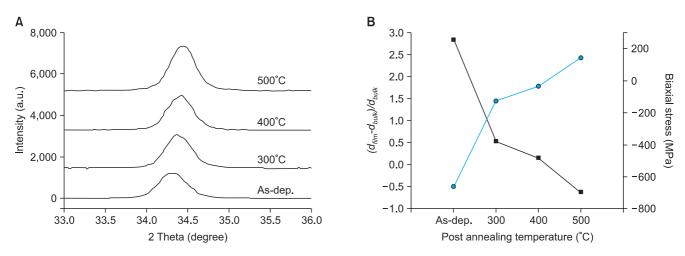

Fig. 3. Bright-field TEM images of ZnO films. (A) As-deposited, (B) annealed at 300°C, and (C) annealed at 500°C. The high resolution image shown in (D) was taken from the sample annealed at 300°C. TEM, transmission electron microscopy.

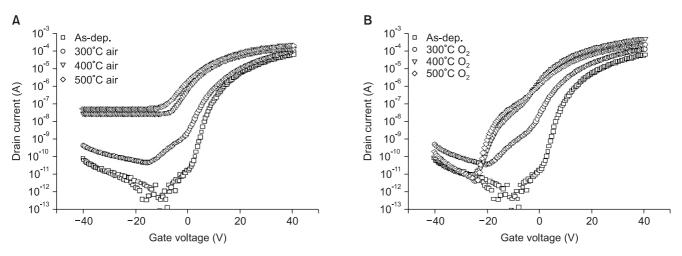

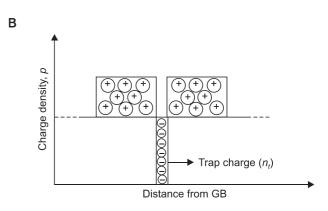

Fig. 4. Transfer curves of TFTs fabricated from the as-deposited and annealed ZnO films in an ambient of (A) air and (B) O<sub>2</sub>. Note: the drain voltage was set to 10 V. TFTs, thin film transistors.

(0002) texture in the films. The intensity of the peak escalates with the annealing temperature increasing, signaling an improvement in the crystallinity of the films (that is, the increment of the grain size).

Another noticeable feature observed in the graph is a systematic shift in the peak position for the samples annealed at elevated temperature. In the XRD curves of thin films, the shift of a peak position usually arises from bi-axial stresses present in the films (Venkatachalam et al., 2008). Fig. 2B shows the strain of the films in the film-normal direction  $[\varepsilon = (d_{film} - d_{bulk})/d_{bulk}]$  measured from the shifts of the (0002) peak position. From this measurement, we could estimate biaxial stresses in the films using the following relationship (Sahu et al., 2008).

$$\sigma_{film} = \frac{2c_{13}^2 - c_{33}(c_{11} + c_{12})}{2c_{13}} \cdot \varepsilon$$

For the elastic constants  $c_{ij}$ , the data obtained from single crystalline ZnO could be used:  $c_{11}$ =208.8,  $c_{33}$ =213.8,  $c_{12}$ =119.7,  $c_{13}$ =104.2 *GPa* (Cebulla et al., 1998). From this calculation, we determined the biaxial stresses of our samples, as shown in Fig. 2B. The as-deposited film was found in a compressive stress (~700 MPa), consistent with other studies on ZnO thin films, which report a film stress of 200~600 MPa and attribute the origin of the stress to atomic peening occurring during sputtering (Cebulla et al., 1998; Zhang et al., 2004; Li et al., 2007). The graph also displays a stress relaxation after annealing. The compressive stress continues to decline with

the annealing temperature increasing until the stress becomes tensile upon annealing at 500°C. This shift of the stress state, from compressive to tensile with the temperature rising, could be explained in connection with the grain size increase confirmed earlier from the peak intensity increase, since a grain size increase means a reduction in the grain boundary area, which would entail the development of a tensile stress in the film.

TEM characterization revealed the details of the microstructure of the ZnO films, which closely parallel with the XRD results, as shown in the bright field images of Fig. 3A-C. The image taken from the as-deposited sample displays a typical columnar structure, in which the grains were grown vertically with a width of around 8 nm. The images also disclose that the columns of the grains became wider upon annealing at 300°C and the grains grew further for the sample annealed at a higher temperature (500°C), which agrees well with the XRD results. In high resolution imaging, the grains dominantly display the lattice images of (0002) planes, as shown in Fig. 3D, which affirms the strong (0002) texture of our films observed in the XRD curves.

Next, we characterized the electrical properties of the transistors fabricated from the as-deposited and annealed ZnO films, as shown in the transfer curves of Fig. 4. The drastic change of the shapes of the curves shown in the graph marks a strong influence of the annealing. Raising the annealing temperature did not only increase the on-current but also the off-current level drastically from 10<sup>-11</sup> A to 10<sup>-7</sup> A. The rise of the on-current contributed to the increase of the mobility for the samples annealed at higher temperatures, which was largely shadowed by the concurrent drop of the

#### Table 1. The summary of the electrical properties of the TFTs

|         | Mobility<br>(cm²/V·s) | Threshold<br>voltage (V) | On/off ratio<br>current | Subthreshold slope (V/dec.) |

|---------|-----------------------|--------------------------|-------------------------|-----------------------------|

| As-dep. | 2.3                   | 11.7                     | ~10 <sup>7</sup>        | 1.5                         |

| 300°C   | 3.4                   | 10.57                    | $10^{6}$                | 2.1                         |

| 400°C   | 3.8                   | -0.38                    | $10^{4.5}$              | 2.5                         |

| 500°C   | 4.9                   | -2.08                    | 10 <sup>3.5</sup>       | 2.7                         |

TFTs, thin film transistors.

**Fig. 5.** (A) A schematic diagram of TFT with a ZnO channel layer populated with vertical grain boundaries, (B) the distribution of charges in the vicinity of a grain boundary, and (C) an energy band diagram that shows the formation of a double Schottky barrier around a grain boundary (redrawn from Hossain et al., 2003). TFT, thin film transistor; GB, grain boundary.

on/off-current ratio due to the off-current surge (see Table 1 for the details of the device performance).

Such a drastic rise of the off-current level generally means a significant increase in the background carrier concentration in the ZnO films. In the framework proposed in a study on modeling of polycrystalline ZnO-based TFTs, this behavior could be connected to the grain size increase caused by the annealing (Singh et al., 2007). In this model, as schematically illustrated in Fig. 5, grain boundaries - treated as a thin layer full of trap sites - capture charge carriers in the vicinity, which leads to the formation of depletion regions and double Schottky barriers in the energy band diagram, as illustrated in Fig. 5C. As such, the reduction of grain boundary areas would result in a drop in the trapped charge density and hence an increase in the free charge carrier concentration. Thus, while the increment of the grain size could improve the electron mobility by reducing the number of potential barriers, it could also critically damage the device performance by raising the background carrier concentration and thus increasing the off-current level.

Next, we annealed some samples in  $O_2$  ambient in an attempt to suppress the off-current rise by infusing oxygen into the films during annealing and thereby reducing the concentration of oxygen vacancies, the major source for charge carriers. Shown in Fig. 4B are transfer curves obtained from the samples. The curves are in a sharp display of the effects of the  $O_2$  annealing: As the annealing temperature increases, the off-current rises only slightly while the on-current increases substantially. The electron mobility also

improved significantly from 2.3 cm<sup>2</sup>/V·s for the as-deposited samples to 5.0 cm<sup>2</sup>/V·s for the 500°C annealed samples. One unusual feature of the curves obtained from the samples annealed at high temperatures (300°C-, 400°C-, 500°Cannealed samples in O<sub>2</sub> ambient, and 200°C - annealed samples in air) is the presence of a small shoulder peak around the turn-on voltage. We suggest that such shoulder peaks might arise from two possibilities, gate leakage and the presence of a parasitic channel layer. Further investigation is in progress to acquire full understanding of this behavior and to improve the device performance.

#### SUMMARY

In this study, we investigated the effects of post-annealing of ZnO thin films on their microstructure and the device performance of the transistors fabricated from the films. From XRD and TEM characterization, we uncovered that the grain size increases with the annealing temperature escalating and that the film stress shifts from compressive to tensile because of the grain size increment. From electrical characterization of the devices, we found that although the grain size increase raised the on-current by reducing the number of potential barriers, it also critically damaged the device performance by raising the background carrier concentration and thus increasing the off-current level. We also confirmed that annealing the devices in an  $O_2$  ambient (instead of air) suppressed such off-current rise by infusing oxygen into the films while improving the electron mobility.

### REFERENCES

- Bae H S and Im S (2004) ZnO-based thin-film transistors of optimal device performance. J. Vac. Sci. Technol. B 22, 1191.

- Bae H S, Yoon J H, Kim J H, and Im S (2003) Photodetecting properties of ZnO-based thin-film transistors. Appl. Phys. Lett. 83, 5313.

- Carcia P F, McLean R S, Reilly M H, and Nunes G (2003) Transparent ZnO thin-film transistor fabricated by rf magnetron sputtering. *Appl. Phys. Lett.* **82**, 1117.

- Cebulla R, Wendt R, and Ellmer K (1998) Al-doped zinc oxide films deposited by simultaneous rf and dc excitation of a magnetron plasma: relationships between plasma parameters and structural and electrical film properties. *J. Appl. Phys.* **83**, 1087.

- Fortunato E, Barquinha P, Pimentel A, Goncalves A, Marques A, Pereira L, and Martins R (2005) Fully transparent ZnO thin-film transistor produced at room temperature. *Adv. Mater.* **17**, 590.

- Hoffman R L, Norris B J, and Wager J F (2003) ZnO-based transparent thin-film transistors. Appl. Phys. Lett. 82, 733.

- Hossain F M, Nishii J, Takagi S, Ohtomo A, Fukumura T, Fujioka H, Ohno H, Koinuma H, and Kawasaki M (2003) Modeling and simulation of polycrystalline ZnO thin-film transistors. J. Appl. Phys. 94, 7768.

- Hwang B I, Park K, Chun H S, An C H, Kim H, and Lee H J (2008) The effects of the microstructure of ZnO films on the electrical performance of their thin film transistors. *Appl. Phys. Lett.* **93**, 222104.

- Hwangbo S, Lee Y J, and Hwang K S (2008) Photoluminescence of ZnO layer on commercial glass substrate prepared by sol-gel process. *Ceramics International* **34**, 1237.

- Kim D C, Kong B H, Jun S O, Cho H K, Park D J and Lee J Y (2008) Pressure dependence and micro-hillock formation of ZnO thin films grown at low temperature by MOCVD. *Thin Solid Films* **516**, 5562.

- Levinson J, Shepherd F R, Scanlon P J, Westwood W D, Este G, and Rider M (1982) Conductivity behavior in polycrystalline semiconductor thin film transistors. J. Appl. Phys. 53, 1193.

- Li C, Furuta M, Matsuda T, and Hirao T (2007) RF power and thermal annealing effect on the properties of zinc oxide films prepared by radio frequency magnetron sputtering. *Research Lett. in Materials Science* **2007**, 26459.

- Normura K, Ohta H, and Hosono H (2004) Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* **432**, 488.

- Norris B J, Anderson J, Wager J F, and Keszler D A (2003) Spin-coated zinc oxide transparent transistors. J. Phys. D **36**, L105.

- Sahu D R, Lin S Y and Huang J L (2008) Investigation of conductive and transparent Al-doped ZnO/Ag/Al-doped ZnO multilayer coatings by electron beam evaporation. *Thin Solid Films* **516**, 4728.

- Singh S, Srinivasa R S, and Major S S (2007) Effect of substrate temperature on the structure and optical properties of ZnO thin films deposited by reactive rf magnetron sputtering. *Thin Solid Films* **515**, 8718.

- Sun Y and Rogers J A (2007) Inorganic semiconductors for flexible

electronics. Adv. Mater. 19, 1897.

- Venkatachalam S, lida Y, and Kanno Y (2008) Preparation and characterization of Al doped ZnO thin films by PLD. *Superlattices and Microstructures* **44**, 127.

- Yao Q J and Li D J (2005) Fabrication and property study of thin film transistor using rf sputtered ZnO as channel layer. *J. Non-Cryst Solids* **351**, 3191.

- Zhang Y, Du G, Yang X, and Yang S (2004) Effect of annealing on ZnO thin films grown on (001) silicon substrate by low-pressure metalorganic chemical vapour deposition. Semicond. Sci. Technol. **19**, 755.