http://dx.doi.org/10.6113/TKPE.2012.17.6.500

# 결합인덕터를 이용한 전압 클램프 3-레벨 고승압 컨버터

김수한 $^{1}$ , 차헌녕 $^{\dagger}$ , 김흥근 $^{2}$ , 최병조 $^{3}$

# Clamp-mode Three-level High Voltage Gain Boost Converter using Coupled Inductor

Su-Han Kim<sup>1</sup>, Hon-Nyong Cha<sup>†</sup>, Heung-Geun Kim<sup>2</sup>, and Byung-Cho Choi<sup>3</sup>

**Abstract** – In this paper, a non-isolated high step-up and high efficiency boost converter is proposed. By using the 3-level boost converter structure, the proposed converter can obtain higher voltage gain than conventional high step-up converters. The voltage spike of the switching device is well clamped by using the clamp circuit composed of a clamp diode and a capacitor and the energy of the leakage inductor of coupled inductor is effectively transferred to output. Due to the 3-level structure, the equivalent switching frequency of the coupled inductor is doubled, which results in reduced inductor size. A 500 W prototype converter is built and tested to verify performance of the proposed converter.

Keywords: boost converter, clamp-mode, coupled inductor, high voltage gain, 3-level converter

# 1. 서 론

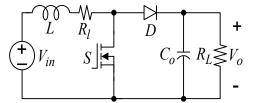

최근 연료전지, 태양광 셀, 그리고 배터리와 같은 낮은 입력전압을 가지는 에너지원에 사용되어 높은 출력 전압을 요구하는 고 승압 부스트 컨버터가 널리 사용되어지고 있다. 그림 1은 기존의 승압형 컨버터를 나타낸다.

그림 1에서 인덕터의 기생저항성분 (Equivalent Series Resistance, ESR)을 고려한 컨버터의 입출력 전압비는 다음과 같이 나타내어진다.

$$\frac{V_o}{V_{in}} = \frac{1}{(1-D)(1 + \frac{R_l}{R_I(1-D)^2})}$$

(1)

여기서 D는 컨버터의 시비율 (duty ratio)를 나타낸다. 식 (1)에 보듯이  $R_l=0$  이면 시비율 증가에 따라 무한 대의 전압이득을 가질 수 있으나 실제로는 인덕터에 존 재하는 기생저항성분으로 인해 컨버터 전압비는 시비율 D가 약 0.9 이상일 경우 오히려 출력전압이 떨어지게된다<sup>[1]</sup>. 또한 그림 1의 컨버터는 스위치 소자의 정격이컨버터 출력전압에 의해 결정되므로 높은 입출력 전압비를 가지는 경우 정격전압, 전류가 높은 스위칭 소자를 사용하여야 하는 치명적인 단점이 있다.

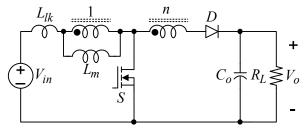

이러한 앞에서 언급한 문제점을 극복하기위해 최근 고승압, 고효율의 컨버터가 많이 소개 되었다<sup>[2-9]</sup>. 그림 2는 결합인덕터를 이용하여 원하는 고승압의 기능을 구현하는 방식이다. 인덕터의 기생저항 성분을 무시한 그림 2 회로의 입출력 전압비는 다음과 같다.

$$\frac{V_o}{V_{in}} = \frac{1 + nD}{1 - D} \tag{2}$$

여기서 n은 결합인덕터의 1, 2차 권선비를 나타내고  $L_{lk}$ 는 결합인덕터의 누설 인덕턴스를 나타낸다. 결합인덕터 권선비 n을 증가시킴으로서 원하는 고승압비를 구현할

Fig. 1 Boost converter with inductor parasitic resistance

Paper number: TKPE-2012-17-6-5 ISSN: 1229-2214 Corresponding author: chahonny@knu.ac.kr, School of Energy Eng., Kyungpook National University

Tel: +82-53-950-8972 Fax: +82-53-950-8979

<sup>&</sup>lt;sup>1</sup> School of Energy Eng., Kyungpook National University

Dept. of Electrical Eng., Kyungpook National University

School of Electronics Eng., Kyungpook National University Manuscript received Jul. 20, 2012; accepted Oct. 16, 2012

수 있고 낮은 전압 정격을 가진 스위치를 사용할 수 있는 장점이 있다. 하지만 결합인덕터의 누설인덕턴스로 인해 스위칭 소자에 과도한 전압 오버슈트가 발생하게된다. 이를 해결하기위해 스위칭 소자와 병렬로 스너버회로가 추가적으로 필요하게 되는 단점이 있다.

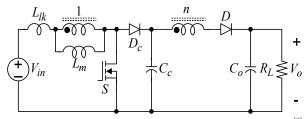

그림 3은 그림 2의 컨버터에서 발생하는 전압 오버슈트를  $D_c$ 와  $C_c$ 로 구성된 클램프회로를 이용하여 전압 오버슈트를 줄이는 전압 클램프 고승압 컨버터이다<sup>[2]</sup>. 결합인덕터의 누설인덕턴스 에너지를 효율적으로 이용하는 구조로써 높은 효율을 기대할 수 있다.

그림 3에서 결합인덕터의 누설인덕턴스가 자화 인덕 턴스보다 아주 작다고 가정하면 입력전압에 대한 클램 프 커패시터 전압과 출력전압은 다음과 같이 나타난다.

$$\frac{V_{Cc}}{V_{in}} = \frac{1}{1 - D} \tag{3}$$

$$\frac{V_o}{V_{in}} = \frac{1+nD}{1-D} \tag{4}$$

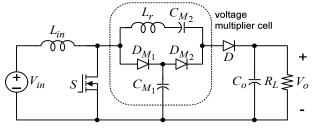

그림 4는 전압 체배기 (voltage multiplfier cell)를 이용한 고승압 컨버터를 나타낸다<sup>[3]</sup>. 주 스위치가 인덕터  $(L_r)$ 로 인해 영전류 스위칭을 하므로 고효율의 컨버터 구현이 가능한 장점이 있다.

그림 3과 4의 승압형 컨버터가 앞에서 언급한 여러 장점이 있지만 입력단에 위치한 인덕터의 등가 주파수가 스위칭 주파수와 동일하므로 인덕터의 사이즈를 줄이기 위해서는 스위칭 주파수를 올려야 하는 단점이 있다. 이에 본 논문에서는 그림 3, 4보다 더 높은 전압 이득을 가지면서 입력 인덕터 사이즈를 많이 줄일 수 있는 3-레벨 고승압 컨버터를 제안한다.

Fig. 2 High voltage gain boost converter using coupled inductor

Fig. 3 Clamped-mode coupled inductor boost converter<sup>[2]</sup>

# 2. 제안된 결합인덕터를 이용한 전압 클램프 3-레벨 고승압 컨버터

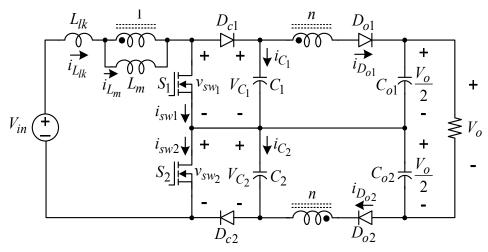

본 논문에서는 그림 3, 4 보다 더 높은 승압비를 얻고 결합인덕터의 사이즈를 줄일 수 있는 3-레벨 전압 클램 프 고승압 컨버터를 제안한다. 그림 5는 제안한 전압 클 램프 3-레벨 고승압 컨버터의 전체 회로도를 나타낸다.

#### 2.1 동작모드해석

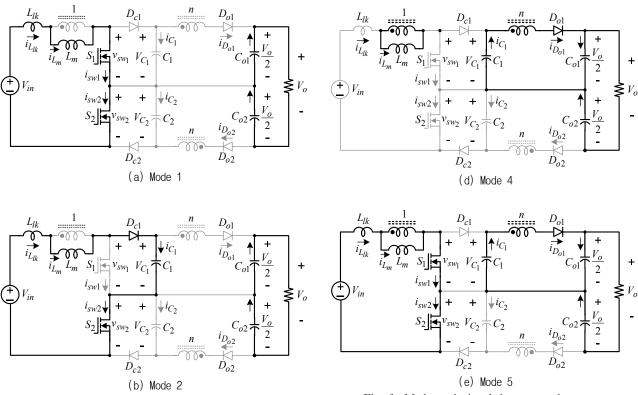

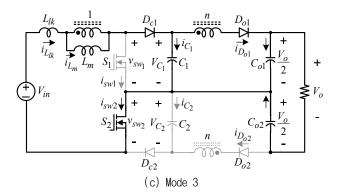

그림 6은 제안한 컨버터의 동작모드를 나타낸다. 본 논문에서는 해석의 편의를 위해 결합인덕터의 기생저항 성분은 없고 스위치  $S_1$ ,  $S_2$ 의 출력 기생 커패시턴스 또한 없다고 가정한다. 결합인덕터의 1차와 두 2차측 권선비는 1:n:n으로 정의하며 결합인덕터는 자화 인덕턴스  $(L_n)$ 와 누설인덕턴스  $(L_k)$ 의 등가회로로 표현한다. 출력 커패시터  $C_{o1}$ ,  $C_{o2}$ 에 걸리는 전압은 동일하다고 가정한다. 따라서

$$V_{C_{o1}} = V_{C_{o2}} = \frac{V_o}{2} \tag{5}$$

### 1) 모드 1 (0-t<sub>1</sub>)

모드 1에서는 스위치  $S_1$ ,  $S_2$ 가 모두 턴 온이 되며 결합인덕터의  $L_m$ 과  $L_k$ 에 입력 에너지가 저장이 된다. 따라서 클램프 다이오드  $D_{\rm cl}$ ,  $D_{\rm c2}$ 는 역바이어스 된다. 출력 다이오드  $D_{\rm o1}$ ,  $D_{\rm o2}$  역시 결합인덕터의 극성 때문에 역바이어스가 걸리게 되어 전류가 흐르지 못한다. 따라서  $L_k$ 와  $L_m$ 에 흐르는 전류는 다음과 같이 일정하게 증가한다.

$$i_{L_{l_k}} = \frac{V_{in}}{L_m + L_{l_k}} t \cong \frac{V_{in}}{L_m} t$$

(6)

#### 2) 모드 2 $(t_1-t_2)$

$t=t_1$ 에서  $S_1$ 이 턴 오프 되면  $S_1$ 의 드레인-소스 전압이 상승한다.  $S_1$ 의 전압이 클램프 커패시터 전압 $(V_{C_1})$ 과 같게 되면 클램프 다이오드  $D_{cl}$ 이 도통하게 되며  $L_{lk}$ 와  $L_m$ 의 전류가 클램프 커패시터  $C_1$ 을 충전하면서  $S_2$ 로 흐르게 된다.

Fig. 4 Voltage multiplier cell integrated with classical dc-dc converter<sup>[3]</sup>

Fig. 5 Proposed clamped-mode 3-level high voltage gain boost converter using coupled inductor

Fig. 6 Mode analysis of the proposed converter

# 3) 모드 3 $(t_2-t_3)$

클램프 커패시터 전압 $(V_{C_1})$ 이 증가하면  $L_m$  양단의 전압 또한 역으로 증가하므로  $t_2$ 에서 출력다이오드  $D_{o1}$ 이 도통하게 된다.  $D_{o1}$ 이 도통하게 되면  $L_m$  양단의 전압은  $(V_{C_1}-V_o/2)/n$ 로 일정하게 된다. 이로 인해  $L_k$ 와  $C_1$ 이 공진을 시작하여  $L_k$ 에 저장된 에너지가  $C_1$ 으로 전달되면서  $C_1$ 을 충전한다. 따라서  $L_k$ 에 흐르는 전류는 감소하고  $C_1$  전압은 상승하게 된다. 이 모드에서는  $D_{o1}$ 이도통되어 있으므로  $L_k$ 에 흐르는 전류는  $C_1$ 에 흐르는

전류와  $D_{o1}$ 에 흐르는 전류의 합이다. 즉

$$i_{L_{lk}} = i_{C_1} + i_{D_{o1}} \tag{7}$$

또한 결합인덕터  $L_m$ 에 흐르는 전류는  $L_{lk}$ 에 흐르는 전류와 2차측 권선에 흐르는 전류  $(i_{D_{\rm el}})$ 의 1차측으로 환산한 전류와의 합이다. 즉

$$i_{L_m} = i_{L_{lk}} + ni_{D_{0,1}} \tag{8}$$

$L_m$ 에 흐르는 전류는 일정 하다고 가정하면  $L_k$ 에 흐르는 전류가 공진을 해서 서서히 감소하므로 식 (8)에 의해서  $D_{\rm ol}$ 에 흐르는 전류는 이와 비슷한 기울기로 서서히 증가하게 된다. (그림 7 참조)

## 4) 모드 4 (t3-t4)

$L_{lk}$ 에 흐르는 전류가 감소하여  $t_3$ 에서 0이 되면 클램프 다이오드  $D_{cl}$ 은 꺼지게 되며 식 (8)에 의해서 출력다이오드 전류 $(i_{D_{cl}})$ 는  $i_{L_m}/n$ 의 기울기로 감소하게 된다.  $D_{cl}$ 이 꺼져 있으므로  $i_{D_{cl}}$ 는  $C_1$ 에서 모두 공급이 되므로  $C_1$  전압이 방전을 하여 서서히 감소한다.

#### 5) 모드 5 $(t_4 - t_5)$

$t_4$ 에서  $S_1$ 이 다시 턴 온 된다. 이때  $L_k$ 양단에 걸리는 전압은 입력전압과 1차측으로 환산된 결합인덕터 2차측 전압의 합으로서 다음과 같다.

$$v_{L_{lk}} = V_{in} + (\frac{V_o}{2} - V_{C_1})/n \tag{9}$$

따라서  $L_{lk}$ 전류는 식 (10)과 같이  $v_{L_{lk}}/L_{lk}$ 의 기울기를 가지면서 결합인덕터의 자화전류  $(i_{L_m})$ 의 크기까지 상승한다.

$$i_{L_{lk}} = \frac{v_{L_{lk}}}{L_{lk}} t$$

(10)

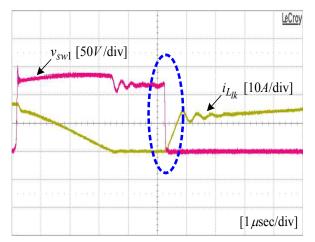

앞의 식 (8)에 보듯이  $L_m$ 에 흐르는 전류는  $L_k$ 에 흐르는 전류와 결합인덕터 2차측 권선에 흐르는 전류  $(i_{D_{o1}})$ 의 1차측으로 환산한 전류와의 합이다. 식 (10)에서  $i_{L_k}$ 가 일정한 기울기로 상승하므로  $i_{D_{o1}}$ 는 비슷한 기울기로 감소하여  $i_{L_k}$ 가  $i_{L_m}$ 이 되는  $t_5$ 에서 0으로 된다.  $D_{o1}$ 의 전류가 일정한 기울기를 가지면서 턴 오프 되므로  $D_{o1}$ 의 역방향 회복전류 (reverse recovery current)의 영향을 현저히 줄일 수 있는 장점이 있다. 또한 이 모드에서 스위치 전류  $(i_{sw1})$ 는  $L_k$  전류와 동일하므로  $S_1$  턴 온시 전압, 전류가 오버랩 되는 구간이 없으므로 영전류 턴 온이 가능하다.

$t=t_5$  이후 부터는 앞에서 설명한 것과 같은 동작을 반복하고 3-레벨 컨버터의 아래쪽 부분을 구성하는  $S_2$ ,  $C_2$ ,  $D_{c2}$ ,  $D_{o2}$  또한 다음 싸이클에서 이와 동일하게 동작 을 한다.

그림 7은 제안한 회로의 주요 동작파형을 나타낸다.

#### 2.2 전압이득 유도

$L_{lk}$ 가  $L_m$ 보다 아주 작을 경우 결합인덕터의  $L_{lk}$ 는 전압이득에 거의 영향이 없으므로 본 논문에서는 전압 이득 유도 시 무시하였다 $^{[2]}$ . 그림 7에서 결합인덕터  $L_m$ 의 volt-sec 조건을 이용하여 입력전압과 클램프 커패시터 전압  $(V_{C_l})$  사이의 전압 관계식은 다음과 같이 유도된다.

$$V_{in}D = (V_{C_1} - V_{in})(1 - D)$$

(11)

$$\frac{V_{C_1}}{V_{in}} = \frac{1}{1 - D} \tag{12}$$

Fig. 7 Key waveforms of the proposed converter

여기서 D는 그림 7에 나타난 것처럼 스위치  $S_1$ ,  $S_2$ 가 동시에 턴 온 되는 구간으로 정의하였다. 또한 출력 커패시터  $C_{o1}$ 의 전압은  $V_{C_1}$ 과 결합인덕터 2차측 전압의 합이므로 다음과 같이 표현되어 진다.

$$V_{C_{o1}} = \frac{V_o}{2} = V_{C_1} + n(V_{C_1} - V_{in})$$

(13)

식 (12)와 (13)으로부터 최종 입출력 전압이득은 다음과 같이 유도된다.

$$\frac{V_o}{V_{in}} = \frac{2(1+nD)}{1-D} \tag{14}$$

식 (14)에서 보듯이 제안한 컨버터의 전압이득은 그림 3의 방식보다 2배 더 높은 승압비를 얻을 수 있다. 또한 결합인덕터의 등가 스위칭 주파수가 컨버터 스위칭 주파수의 두 배가 된다. 따라서 결합인덕터 사이즈를 많이 줄일 수 있는 장점이 있다.

그림 3의 경우와 마찬가지로  $S_1$ ,  $S_2$ 가 영전류 스위칭이 되고 스위치 전압이 클램프 커패시터 전압으로 클램프 되므로 낮은 전압 스트레스를 갖는 스위칭 소자를 사용할 수 있다.

#### 3. 실험결과

본 논문에서 제안한 회로의 성능 검증을 위해 500 W의 시제품을 제작하여 성능을 검증하였다. 표 1은 제안한 컨버터의 전기적 사양을 나타낸다.

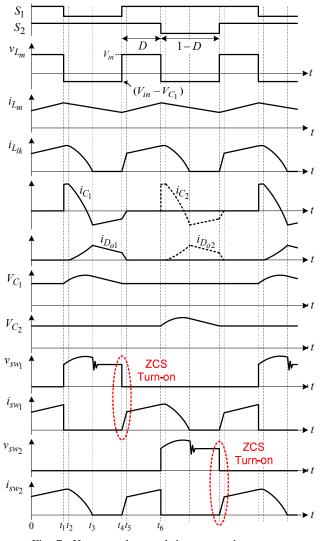

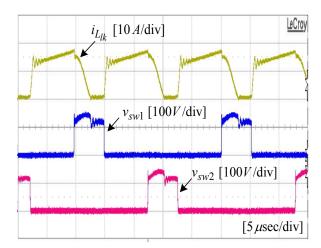

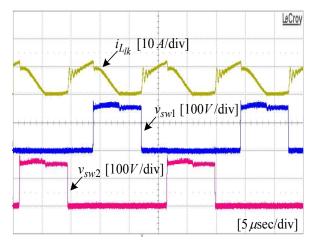

그림 8은  $V_{in}=50\,V$ ,  $V_o=500\,V$ ,  $P_o=500\,W$ 에서 흑정한 결합인덕터 누설인덕턴스 전류  $(i_{L_k})$ , 스위치  $S_1$ ,  $S_2$  전압파형  $(v_{sw_1},\ v_{sw_2})$ 을 나타낸다. 앞서 설명한 것처럼 결합인덕터에 걸리는 등가주파수가 스위칭 주파수의두 배가 됨을 알 수 있다. 또한 스위치 최대 전압이 클램프 커페시터 전압으로 잘 억제됨을 알 수 있다. 그림 9는  $V_{in}=100\,V$ ,  $V_o=500\,V$ ,  $P_o=500\,W$ 인 경우 그림 8과 동일한 파형을 측정한 것이다.

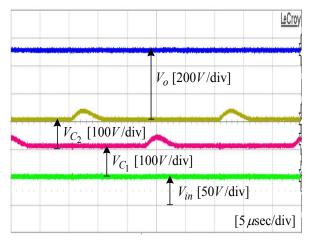

그림 10은  $V_{in}=50\,V$ ,  $V_o=500\,V$ ,  $P_o=500\,W$ 에서 측정한 입력전압  $(V_{in})$ , 클램프 커패시터 전압  $(V_{C_1},\ V_{C_2})$ , 그리고 출력전압  $(V_S)$  파형을 나타낸다.

그림 11은 스위치 전압과 누설 인덕턴스 전류 파형을 확대한 그림이다. 그림 7에서 보듯이 스위치 턴 온시 스 위치 전류는 결합인덕터의 누설 인덕턴스 전류와 동일 하므로 본 논문에서는 스위치 전류 대신 누설 인덕턴스 전류 파형을 스위치 전압과 비교하여 영 전류에서 턴 온 됨을 확인하였다.

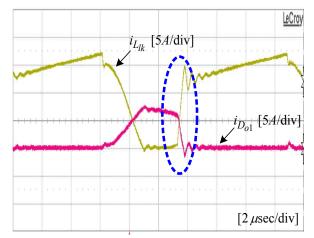

그림 12는 누설 인덕턴스 전류와 출력 다이오드 전류 를 측정한 파형이다. 결합인덕터의 누설 인덕턴스로 인

Table 1 Electrical specifications of the proposed converter

| Output power                             |          | 500 [W]    |

|------------------------------------------|----------|------------|

| Input voltage range                      |          | 50-100 [V] |

| Output voltage                           |          | 500 [V]    |

| Switching frequency                      |          | 40 [kHz]   |

| Switching device $(S_1, S_2)$            |          | IRFP260N   |

| Diode $(D_{c1}, D_{c2}, D_{o1}, D_{o2})$ |          | RHRG3060   |

| Clamp capacitor $(C_1, C_2)$             |          | 0.68 [uF]  |

| Output capacitor ( $C_{o1}, C_{o2}$ )    |          | 30 [uF]    |

| Coupled inductor                         | $L_m$    | 60 [uH]    |

|                                          | $L_{lk}$ | 2 [uH]     |

|                                          | n        | 1:2:2      |

해 출력 다이오드 전류가 일정한 기울기를 가지면서꺼 짐을 알 수 있다. 따라서 다이오드의 역방향 회복 전류 의 영향을 상당히 줄일 수 있다.

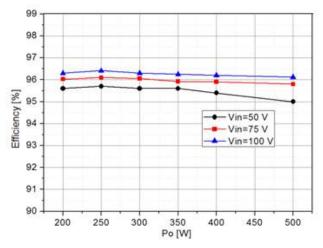

그림 13은 입력전압과 부하변동에 따른 제안한 컨버 터의 효율을 측정한 그래프이다.

Fig. 8 Experimental waveforms of leakage inductor current and switch voltages (Vin=50 V)

Fig. 9 Experimental waveforms of leakage inductor current and switch voltages (Vin=100 V)

Fig. 10 Experimental waveforms of input, clamp capacitor, and output voltage

Fig. 11 Experimental waveforms of switch voltage and leakage inductor current

Fig. 12 Experimental waveforms of leakage inductor and output diode current

#### 3. 결 론

본 논문에서는 기존의 결합인덕터를 이용한 전압 클 램프 승압형 컨버터를 3-레벨 컨버터에 적용하여 다음

Fig. 13 Efficiency of the proposed converter

과 같은 장점을 가진 개선된 3-레벨 고승압 컨버터를 제안하였다. 제안한 컨버터의 장점으로는 다음과 같다.

- 1. 기존 결합인덕터를 이용한 전압 클램프 방식보다 2 배 더 높은 승압비를 구현

- 2. 입력측 결합인덕터에 걸리는 등가 스위칭 주파수가 컨버터 스위칭 주파수의 두 배가 되므로 결합인덕 터의 권선수 (혹은 코어 사이즈)가 절반으로 감소.

- 3. 주 스위치  $S_1$ ,  $S_2$ 가 영 전류 턴 온 함으로써 스위 칭 손실 감소

- 4. 클램프 다이오드와 츨력 다이오드의 역방향 회복 전류 문제 상당히 감소

500 W의 시제품을 제작하여 제안한 회로의 성능을 실험적으로 검증하였다.

본 연구는 지식경제부 및 정보통신산업진흥원의 IT융합 고급인력과정 지원사업의 연구결과로 수행되었음(NIPA-2012-H0401-12-1006)

#### 참 고 문 헌

- [1] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed. Norwell, MA: Kluwer, 2001.

- [2] Q. Zhao and F. C. Lee, "High-Efficiency, High Step-Up DC-DC Converters," *IEEE Transactions on Power Electronics*, Vol. 18, No. 1, pp. 65–73, Jan. 2003.

- [3] M. Prudente, L. L. Pfitscher, G. Emmendoerfer, E. F. Romaneli, and R. Gules, "Voltage Multiplier Cells Applied to Non-Isolated DC-DC Converters," *IEEE Transactions on Power Electronics*, Vol. 23, No. 2, pp. 871–887, Mar. 2008.

- [4] W. Li and X. He, "A Family of Interleaved DC-DC

- Converters Deduced From a Basic Cell With Winding-Cross-Coupled Inductors (WCCIs) for High Step-Up or Step-Down Conversions," *IEEE Transactions on Power Electronics*, Vol. 23, No. 4, pp. 1791–1801, July 2008.

- [5] R. J. Wai, and R. Y. Duan, "High step-up converter with coupled-inductor," *IEEE Transactions on Power Electronics*, Vol. 20, No. 5, pp. 1025–1035, Sep. 2005.

- [6] W. Li and X. He, "Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications," IEEE Transactions on Industrial Electronics, Vol. 58, No. 4, pp. 1239–1250, Apr. 2011.

- [7] M. Shen, F. Z. Peng, and L. M. Tolbert, "Multilevel dc-dc power conversion with multiple dc sources," *IEEE Transactions on Power Electronics*, Vol. 23, No. 1, pp. 420-426, Jan. 2008.

- [8] F. Z. Peng, F. Zhang, and Z. Qian, "A magnetic-less dc-dc converter for dual voltage automotive systems," IEEE Transactions on Industrial Applications, Vol. 39, No. 2, pp. 511 - 518, Mar/Apr. 2003.

- [9] E. H. Ismail, M. A. Al-Saffar, and A. J. Sabzali, "High conversion ratio dc - dc converters with reduced switch stress," *IEEE Transactions on Circuits Syst. I, Reg. Papers*, Vol. 55, No. 7, pp. 2139 - 2151, Aug. 2008.

#### 김수한(金守漢)

1981년 8월 19일생. 2009년 한경대 전자공학과 졸업. 2012년 경북대 전자전기컴퓨터학부 졸업(석사). 현재 경북대 에너지공학부박사과정.

#### 차헌녕(車憲寧)

1972년 10월 17일생. 1999년 경북대 전자공학과 졸업. 2001년 동 대학원 전자공학과졸업(석사). 2001년~2003년 (주)피에스텍 근무. 2004년~2005년 한국전기연구원 근무. 2009년 미국 Michigan State University 전기

공학과 졸업(공박). 2010년~2011년 한국전기연구원 스마트그리 드연구본부 선임연구원. 현재 경북대 에너지공학부 조교수. 당학회 편집위원.

#### 김흥근(金興根)

1956년 4월 24일생. 1980년 서울대 전기공학과 졸업. 1982년 동 대학원 전기공학과 졸업(석사). 1988년 동 대학원 전기공학과 졸업(공박). 1990년~1991년 미국 Univ. of Wisconsin-Madison 방문교수. 2006년~2007년 미국 Michican State University 방문교수.

경북대 IT대학 전기공학과 교수. 당 학회 부회장.

#### 최병조(崔柄朝)

1957년 10월 12일생. 1980년 한양대 전자공학과 졸업. 1979년~1985년 국방과학연구소근무. 1988년 Virginia Polytechnic Institute & State University 전력전자공학 졸업(석사). 1992년 동 대학원 전력전자공학과 졸업(공

박). 1992년~1993년 동 대학 연구교수 역임. 1994년~1996년 삼성전자 수석연구원. 1996년~현재 경북대 IT대학 전자공학부 교수.