# 위성전원분배를 위한 LCL 동작 파라미터 설정분석

임성빈\*, 전현진\*\*, 김경수\*\*\*, 김태윤\*\*\*\*

# The Analysis of the LCL Set-up Parameters for Satellite Power Distribution

Seong-Bin Lim\*, Hyun-Jin Jeon\*\*, Kyung-Soo Kim\*\*\*, Tae-Youn Kim\*\*\*

#### **Abstract**

In this paper, the characteristics of LCL set-up parameters for the satellite load distribution are analyzed under the electrical system environment, implemented the LCL circuits and evaluated the performance and its behaviour.

Recently, it is implemented the load distribution circuit by latching current limiter(LCL) rather than conventional fuse and relay for the protection of the satellite power system from a fault load. The LCL circuit is composed of the electrical components, not mechanical parts with the fuse and relay. When detected the over current on a fault load, it is activated to maintain the trip-off level for set-up time and then cut-off the load power by the active control. It is more flexible and provided a chance to reuse of the load in case of temporarily event, but the fuse and relay can't be used again after activating due to the physical disconnection. However, for implementation of LCL circuit, it should be carefully considered the behavior of the LCL circuit under the worst electrical system environment and applied it to define the set-up parameters related with over-current inhibition.

### 초 록

최근 위성 시스템의 전력분배는 기존의 퓨즈와 릴레이로 구성된 것과는 달리 LCL (Latching Current Limiter) 회로로 구현되어, 각각의 부하전원을 단속한다. LCL은 부하에서 생기는 과전류를 제한함으로서 고장 의심이 있는 부하를 물리적으로 차단하는 기존 방법에 비하여 고장의 원인을 분석하고, 일시적인 고장인 경우 부하를 재사용할 수 있는 장점이 있다. 그러나 LCL 회로는 전자소자로 구현되는 만큼 주변회로(부하회로)와의 연동성과 회로 자체의 특성을 이해해야 하며, 무엇보다 과전류를 차단하기 위하여 설정하는 LCL 동작 파라미터의 정의를 위한 기술적인 접근이 요구된다. 따라서 본 논문에서는 전력분배 모듈의 LCL 동작 파라미터를 정의하기 위한 분석을 수행했고, 회로구현 및 특성 시험결과를 나타냈다.

키워드 : LCL(Latching Current Limiter), 퓨즈와 릴레이(Fuse and Relay), 동작 파라미터(Trip-off Parameters), 과도전류(In-rush Current), 과도특성(Transient), 전원분배모듈(Electrical Power Distribution Module)

접수일(2011년 1월 8일), 수정일(1차 : 2011년 4월 9일, 2차 : 2011년 6월 14일, 게재 확정일 : 2011년 11월 1일)

<sup>\*</sup> 다목적3A호 체계팀/sblim@kari.re.kr

<sup>\*\*</sup> 다목적3A호 체계팀/hjjeon@kari.re.kr

<sup>\*\*\*</sup> 한국항공우주산업/kskimrok@koreaaero.com

<sup>\*\*\*\*</sup> 우주환경시험팀/kity@kari.re.kr

## 1. 서 론

최근에는 위성 시스템을 구성하고 있는 부하에 전원을 공급하는 방법으로 기존의 퓨즈와 릴레이 회로로 구성된 것과는 달리 전기적으로 제어가 가능한 LCL(Latching Current Limiter)로 구현되어, 각각의 부하 전원을 단속한다. 기존의 방법에서 릴레이 스위치는 전원을 단속하고, 퓨즈는 연결되어 있는 부하에 문제가 발생했을 경우 개방되어 부하의 고장으로부터 위성의 전원버스를 보호하도록 한다.

LCL은 부하 전원을 단속하는 기능 외에도 과전류를 제한함으로서 고장의 원인을 분석하고, 고장이 일시적인 경우에 부하를 재사용할 수 있는 장점을 갖는다. 그러나 그러한 장점에도 불구하고 LCL은 전자회로로 구현되는 만큼 주변회로 (부하회로)와의 연동성과 회로 자체의 특성을 이해해야 하며, 무엇보다 과전류를 차단하기 위하여 설정하는 LCL의 동작 파라미터를 정의하기위한 기술적인 접근이 요구된다.

LCL의 동작 파라미터는 최대 허용 전류(Tripoff Current)의 크기와 지연시간(Trip-off Time)이 있다. 이 두 파라미터는 LCL의 과전류 감지와 동작시간으로 이는 초기에 생기는 과도특성의 상승 속도와 그 에너지에 의하여 LCL 회로 내의소자에 열적 스트레스(Thermal Stress)로 인한 손상을 주지 않도록 설정해야 한다.

따라서 본 논문에서는 전력분배를 위한 LCL의 주요 파라미터 값을 정의하기 위하여 부하 특성 분석 및 회로 구현을 통하여 동작 특성을 확인하였으며, 시스템 설계 중 고려해야 하는 전자파 양립성 규격[1]에 대하여 고찰을 수행하였다.

#### 2. 본 론

#### 2.1 전력분배

#### 2.1.1 퓨즈와 릴레이

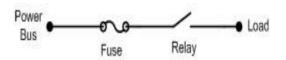

일반적으로 이용하고 있는 위성의 전원분배는 그림 1과 같이 퓨즈와 릴레이로 구성된다.

그림 1. 퓨즈와 릴레이

그림 1에서 릴레이는 부하에 전원을 인가하거나 차단하기 위한 스위치이며, 퓨즈는 부하의 오동작 또는 단락 등에 따른 과전류 발생 시 개방되면서 물리적으로 부하를 위성 버스로부터 분리한다. 그런데 퓨즈는 한 번 동작하면 개방되므로한번 동작하면 부하로의 전원 공급이 불가능하여부하는 재사용할 수 없다.

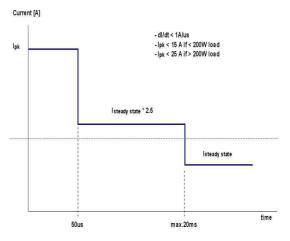

그림 2. 퓨즈와 릴레이의 과도전류 제한곡선

퓨즈와 릴레이를 이용한 전력분배 시 부하에서 생기는 과도(In-rush) 전류는 전자파 양립성 규격에서 그림 2와 같이 제한한다. 이 제한 곡선은 부하에서 단락이나 과도 전류 발생 시 위성 전원 시스템을 보호하기 위한 퓨즈의 정격 용량[2]과 부하에서 생기는 과도전류 특성 파형에 따라 정의한다.

#### 2.1.1 LCL

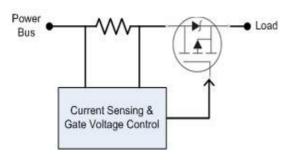

LCL은 그림 3과 같이 반도체 소자(FET)를 사용하여 부하에 전원을 공급하면서 부하에서 발생하는 과도 전류와 고장 전류로 부터 전원 시스템

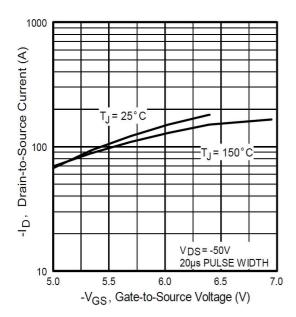

을 보호하는 기능을 수행하는 전자회로이다. FET는 그림4와 같이 게이트(G) 전압(VGS)에 따라소스(S)와 드레인(D) 사이의 전압과 전류를 조절할 수 있는 특성을 가지고 있는 전자 부품이다.

그림 3. LCL을 이용한 전력 분배

그림 4. FET 출력 특성

LCL은 위성 명령에 의하여 부하에 전원을 인가하거나 차단할 수 있으며, 부하 선로가 단락되거나 과전류 발생 시 출력 전류를 일정한 레벨로일정 시간 유지시킨다. 이렇게 전자회로로 구현되는 경우 물리적으로 차단하는 퓨즈와는 달리부하의 고장 여부를 점검하고 재사용할 수 있는 장점이 있다. 수신 장비와 같이 작은 전력을 요

구하며 임무에 중요한 부하는 항상 전류 제한 기능을 수행하는 FCL (Fold-back Current Limiter)로 이용되기도 한다.

그림 5는 LCL을 이용하여 전원을 분배하는 경우 부하에서 생기는 과도 전류를 제한하기 위한 전자파 양립성 규격의 제한 곡선을 보여준다.

그림 5. LCL의 과도전류 제한 곡선

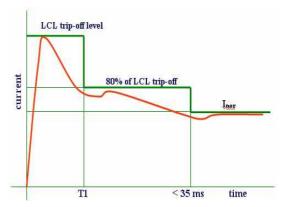

과도전류를 제한하는 가장 중요한 파라미터는 LCL의 동작 레벨(Trip-off Level)과 지연 시간 (T1)으로 이는 부하의 정상 전류(Inor) 에 의하여 결정[3]되며, 이를 정의하기 위한 기술적인 내용은 다음 절에서 설명한다.

# 2.2 LCL 파라미터 정의 2.2.1 LCL 파라미터 특성

본 절에서는 LCL의 동작 파라미터를 정의하기 위한 일반적인 특성에 대하여 고찰한다.

- LCL ON/OFF 스위칭 기능

- 위성 명령에 따라 부하에 전원을 인가하 거나 차단하는 기능

- 동작 및 전류 제한 레벨(그림 5 참조)

- LCL의 동작 점과 전류 제한레벨은 동일 하며 연결되어 있는 부하의 최대 동작전 류에 30% 이상 높은 레벨에서 설정. 일

상태 전류를 의미함

#### - LCL 동작 시간

- 과전류 발생으로부터 LCL이 전류 제한 을 시작하기 까지는 회로 특성에 따라 적어도 10us 정도의 지연시간이 있음

- 10us 이내에 전류 제한을 시작하도록 구 현하는 것은 현실적으로 어려우며, 전자 파 양립성 관점에서 동작 마진을 포함하 여 20us 이내 정도로 구현

- 전류 제한 지연 시간

- LCL이 고장 전류를 허용 할 수 있는 시 간으로 부하 고장 인식으로 부터 부하 전원 차단까지의 지연시간으로 정의

- 일반적으로 시스템에 따르지만 약 16 ms +/- 5 ms의 값으로 정의

- 실제 설계에서는 LCL을 구성하는 주요 소자인 FET 열적 충격 에너지에 따라 결정

- 모니터링

- ON/OFF 상태

- LCL 동작 상태

#### 2.2.2 LCL 동작 레벨 정의

본 절에서는 실제로 파라미터 값을 정의하기 위한 개념을 설명한다. LCL 동작 레벨은 식 (1) 과 같이 각 부하의 정상 상태 전류 값에 1.3을 곱한 후, 근접한 값으로 등급화 한다.

$$I(Trip-off) = 1.3 \times I(max. load)$$

(1)

예를 들면 2A 보다 작은 부하는 모두 2A로 등급화하고, 그 이상으로 큰 경우는 계산된 전류 에 근사한 전류 값으로 정의함으로서 실제 하드 웨어의 설정에 따른 편의성을 제공한다.

LCL이 동작하여 전원을 차단하기까지의 지연

반적으로 부하의 최대 동작 전류는 정상 시간은 다음과 같으며, 이 시간이 지나면 부하 전원은 차단된다.

- 전류 제한 지연 시간(Trip-off Time)

- LCL 지연 시간은 FET가 열적으로 견딜 수 있는 시간으로 결정하는데, 고장 전 류 발생시 FET 소모 전력을 이용하여 FET 내부 접점 온도가 허용된 온도 까 지 상승하는 시간으로 계산

- 각 채널의 최대 전류를 기준으로 500us, 1ms, 3ms, 5ms, etc…, 등으로 등급화

- 이 값은 FET가 열적 충격에 의해 파손 되지 않는 범위

표 1은 LCL 설정을 위하여 등급화한 예를 보 여준다.

표 1. LCL 등급 분류 (예)

| CLASS | Insu_nor | LCL Vers | Ling_off | AWG | No of cables | Imax per cable | Imax / Ling | 0.8* Į <sub>bij</sub> |

|-------|----------|----------|----------|-----|--------------|----------------|-------------|-----------------------|

| A     | 0.30     | 0.15     | 0.40     | 22  | 1            | 0.40           | 1,333       | 0.320                 |

| В     | 0.60     | 0.20     | 0.80     | 22  | 1            | 0.80           | 1,333       | 0.640                 |

| С     | 1.20     | 0.33     | 1.60     | 22  | 2            | 0.80           | 1,333       | 1,280                 |

| D     | 2,30     | 0.25     | 3.00     | 22  | 2            | 1.50           | 1,304       | 2,400                 |

| Е     | 3.10     | 0.25     | 4.00     | 20  | 2            | 2.00           | 1.290       | 3,200                 |

| F     | 3.80     | 0.25     | 5.00     | 20  | 2            | 2,50           | 1,316       | 4.000                 |

| G     | 4.60     | 0.30     | 6.00     | 20  | 2            | 3.00           | 1,304       | 4.800                 |

| FCL   | 0.95     | 0.15     | 1.30     | 22  | 2            | 0.65           | 1.368       | 1.040                 |

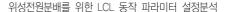

#### 2.2.3 FET 열적 스트레스 해석

본 절에서는 LCL 동작 특성을 결정하는데 가 장 중요한 고려 요소 중에 FET의 열적 스트레스 [4][5]를 계산하여, LCL 파라미터가 정상적으로 선정되었는지 검증하는 방법에 대하여 기술한다.

그림 6은 FET에 가해지는 열적 스트레스를 계 산하기 위하여 이용되는 열적 임피던스(Thermal Impedance) 곡선으로 FET 제작사에서 제공한다 [6][7]. 열적 스트레스는 FET가 견딜 수 있는 최 대 온도를 기준으로 계산되는데, 일반적으로 위

성에서 주로 사용하는 FET 내부의 접점 온도는 제작사에서 150℃를 보장 하지만 일반적으로 125℃를 기준으로 설계한다. 예로서 다음의 조건을 이용하였다.

그림 6. 트랜지언트 열 임피던스, Tc to Ti

- Tc (FET Case 온도): 80℃

- Pdm (FET 소모 전력): 100W

- FET ON 시간: 10ms

그림 6의 그래프로부터 열적 임피던스 0.313을 을 이용하여 계산한 FET의 접점 온도는 식(3)과 같다.

$$T_j = 100 \times 0.313 + 80 = 111.3^{\circ}C$$

(2)

계산 결과 FET 접점 온도는 125℃ 보다 낮으므로 FET는 위의 조건에서 열적 스트레스를 받지 않는 것으로 해석된다. 그런데, FET에서 소모하는 전력이 144W로 증가하면 식(3)과 같이 초기 설계온도를 초과한다.

$$Tj = 144 \times 0.313 + 80 = 125.1^{\circ}C$$

(3)

이러한 경우 FET의 접점 온도가 125℃ 보다 커져서 열적 스트레스를 받는 것으로 해석 되므 로 FET ON 시간을 짧게 조절하여 열적 임피던 스를 낮춤으로서 FET가 열적 스트레스를 받지 않도록 해야 한다. 표 2는 그림 6의 열적 임피던스 곡선에 FET ON 시간과 소모 전력을 이용하여, FET 접점의 온도 상승을 계산한 결과이다. 케이스 온도를 5 5℃로 가정하였을 경우 70℃까지만 온도 상승을 허용하므로 70℃ 초과하여 온도 상승이 계산되는 경우는 표시하지 않았다.

표 2. FET 접점 온도 상승 계산 (예)

| Delta T<br>(°C)     |      | Power (W) |      |      |      |      |      |      |      |  |  |

|---------------------|------|-----------|------|------|------|------|------|------|------|--|--|

|                     |      | 10        | 20   | 50   | 100  | 200  | 500  | 550  | 650  |  |  |

|                     | 0.1  | 0.3       | 0.6  | 1.6  | 3.1  | 6.3  | 15.7 | 17.2 | 20.3 |  |  |

| Pulse Duration (ms) | 0.2  | 0.4       | 0.9  | 2.2  | 4.4  | 8.8  | 22.0 | 24.1 | 28.5 |  |  |

|                     | 0.5  | 0.7       | 1.4  | 3.6  | 7.2  | 14.5 | 36.2 | 39.8 | 47.1 |  |  |

|                     | 1.0  | 1.1       | 2.2  | 5.6  | 11.2 | 22.4 | 56.0 | 61.6 |      |  |  |

|                     | 2.0  | 1.4       | 2.8  | 7.0  | 14.0 | 28.0 | 70.0 |      |      |  |  |

|                     | 5.0  | 2.2       | 4.5  | 11.2 | 22.4 | 44.8 |      |      |      |  |  |

|                     | 6.0  | 2.4       | 4.8  | 11.9 | 23.8 | 47.6 |      |      |      |  |  |

|                     | 7.0  | 2.6       | 5.1  | 12.8 | 25.5 | 51.0 |      |      |      |  |  |

|                     | 8.0  | 2.7       | 5.5  | 13.7 | 27.4 | 54.8 |      |      |      |  |  |

|                     | 9.0  | 3.0       | 5.9  | 14.9 | 29.7 | 59.4 |      |      |      |  |  |

|                     | 10.0 | 3.1       | 6.3  | 15.7 | 31.3 | 62.6 | 7    |      |      |  |  |

|                     | 20.0 | 3.9       | 7.8  | 19.4 | 38.8 |      |      |      |      |  |  |

|                     | 50.0 | 5.0       | 10.0 | 25.0 | 50.0 |      |      |      |      |  |  |

표에서 보면 일반적으로 많이 적용하는 10ms 의 전류 제한 시간을 확보하려면 FET에서는 최대 200W 까지만 허용할 수 있다. 100W 이하에 대해서는 제한 시간 선택이 자유로우나 500W가 넘어가게 되면 1ms 정도만 허용할 수 있기 때문에 사용하는데 주의해야 한다.

#### 2.3 LCL 회로 구성

#### 2.3.1 회로 특성 시험

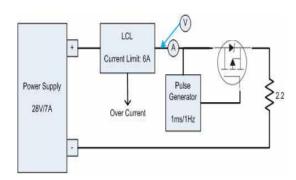

LCL 특성 시험을 위하여 그림 7과 같이 회로를 구현하였고, 펄스 형태로 부하를 구동하여 전류를 제한하는 기능을 검증하였다.

그림 7. 시험 블록 다이어그램

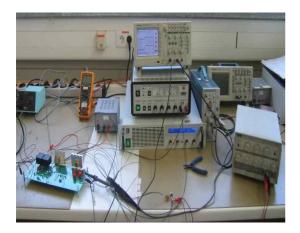

그림 8. 시험 시스템 구성 사진

그림 8은 시험 장비의 구성 사진을 보여주며, 펄스 형태의 부하는 FET에 저항을 연결하고 펄 스 발생장치를 이용하여 FET를 펄스 형태로 구 동하여 구현하였다. 이때 시험을 위한 설정 파라 미터 값은 다음과 같다.

- 입력 전압/전류: 28V/7A

- LCL 설정 전류: 6A

- 부하: FET with 2.2Ω 저항

FET ON Time: 1ms FET OFF Time: 999ms

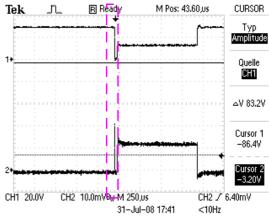

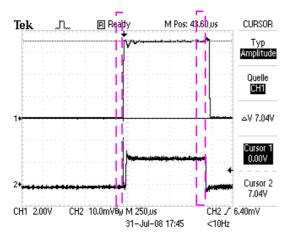

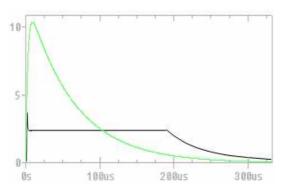

그림 9. 동작파형 측정결과

Ch#1: Output Voltage (20V/div) Ch#2: Load Current (5A/div)

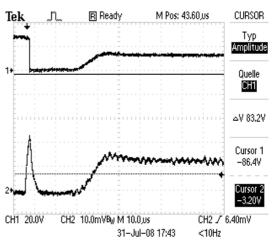

그림 9는 부하에서 과도한 펄스가 생겼을 때 LCL의 동작파형을 측정한 결과이며, 그림 10은 LCL이 동작하는 순간의 측정파형을 보여준다.

그림 10. 동작순간의 측정파형

측정 결과 그림 9 및 그림 10과 같이 부하에서 고장이 발생하면 우선 5us 이내에 출력을 OFF 시키고, 대략 20us 동안 OFF 상태를 유지한후 천천히 FET를 ON 시킴으로서 LCL에서 부하전류를 조절하는 것을 확인 할 수 있다.

그림 10에서 FET 전류가 아주 짧은 시간 (~10 us) 동안 12A에 도달 하지만, FET가 바로 꺼지기 때문에 열적인 영향은 무시 할 수 있다. 접점 온도를 계산하면 식(4)와 같으며, 이는 최대 10us라고 가정했을 때 약 3.0℃ 정도의 온도가 상승하는 것을 알 수 있다.

Trise =

$$(28 \times 12) \times 0.009 = 3.0^{\circ}$$

(4)

따라서 짧은 펄스전류에 의한 FET 접점 온도 상승은 무시할 수 있다. 추가로 FET가 전류를 제 한하고 있는 1ms 동안의 접점 온도를 예측해 보 면, 식(5)와 같이 8.0℃ 상승함을 알 수 있다.

Trise =

$$(12 \times 6) \times 0.112 = 8.0^{\circ}$$

(5)

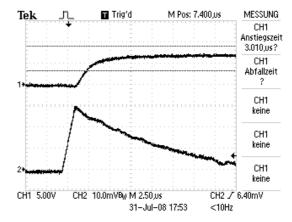

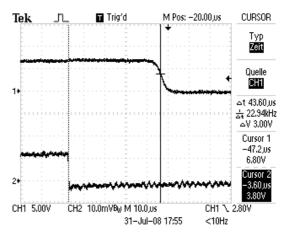

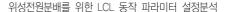

그림 11은 전류 제한 동작 중임을 표시하는 동작신호 측정 결과 이고, 그림 12는 동작신호 시작점의 파형이며, 그림 13은 동작신호 종료 시 점의 파형을 보여준다.

그림 11. 제한동작 신호 측정결과

Ch#1: Over Current Signal (2V/div) Ch#2: Load Current (5A/div)

그림 12. 제한동작 시작점의 파형

그림 13. 제한동작 끝점의 파형

Ch#1: Over Current Signal (5V/div) Ch#2: Load Current (5A/div)

#### 2.3.2 LCL 동작 특성

LCL을 이용한 전력분배 회로의 장점은 부하에서 발생하는 짧은 시간 동안의 과도전류를 LCL 값으로 제한하여 과도전류 발생에 따른 전원 시스템의 외란을 감소키기는 역할을 한다. 그림 14와 같이 약 10A 과도전류 특성을 가지는 부하가 2.5A LCL에 할당되어 있다면 과도전류는 2.5A로 제한되므로 LCL이 없는 경우 대비 긴 시간 동안 제한된 과도전류를 가져가게 된다. 따라

서 전원 시스템 입장에서는 2.5A 정도의 외란만 고려하면 되므로 부하 변동에 따른 전원 시스템 변동성을 상당 부분 완화시키는 효과를 얻을 수 있다.

그림 14. In-rush Current & LCL

#### 2.3.3 LCL 적용상의 주의 사항

이러한 장점과는 달리 LCL의 적용에는 몇 가 지 고려해야 할 것이 있다.

하나는 전력분배장치와 부하에 모두 LCL 회로가 구현되어 있는 경우이다. 두 개의 LCL이유사한 동작 파라미터로 설정된 경우 부하에서 과도전류가 생성되면, 이들은 동시에 전류를 제한하도록 동작할 것이며 이러한 과정에서 양쪽회로 간에 서로 영향을 줄 수 있기 때문에 오동작 할 수 있으므로, 어떤 경우든 한 번에 하나만동작하도록 구성해야한다.

이를 피하기 위하여 LCL의 파라미터를 서로 다르게 설정하면 된다. 이는 큰 전류로 설정된 LCL이 작은 전류로 설정된 LCL을 완전히 커버 하도록 해야 하며, 다른 방법으로 LCL을 하나만 장착하는 것이다. 이는 LCL 두 개가 동시에 동 작하는 경우 안정되게 동작하려면, 반드시 두 LCL의 동작 특성이 일치(과도 응답 특성 포함) 하여 과도 응답상태를 지나 안정화되어야 함을 의미한다.

두 LCL의 과도 응답특성이 다르면, 서로가 영향을 주어 과도 응답상태에서 벗어나지 못 할 수 있으며, 부하에 장착되어 있는 LCL 특성에 대한

정보가 전혀 없는 상태에서 두 LCL이 동작하는 경우, 문제없이 두 LCL이 잘 동작할 것이라고 예상할 수 없기 때문이다.

다른 하나는 부하에서 생기는 과도전류의 상 승 시간을 제한하는 것이다. LCL이 과도전류를 감지하여 동작하는 시간은 기술적으로 앞에서 논 의된 바 있다. 만약 과도전류의 상승시간이 동작시간보다 빠른 경우 전류를 제한하기 위하여 동작하는 동안에 이미 최대 전류 값이 FET에 열적스트레스를 줄 수 있기 때문이다.

이 외에도 LCL은 전자장치로 구현되는 만큼 안정성 있게 회로가 구현되어야 한다. 이는 LCL 이 부하의 과도응답에 대하여 전원 시스템을 보 호하기 위한 회로일지라도 그 자체 성능이 전자 파 양립성 관점에서 안정성을 가지고 있어야 전 체적인 전원 시스템의 안정성을 가져다 줄 수 있 기 때문이다.

#### 3. 결 론

다목적실용위성 급의 전원 시스템에 전력분배 는 LCL (Latching Current Limiter)로 구현되어 있으며, 이전 프로그램에서 사용되었던 퓨즈와 릴레이 회로와는 달리 전자회로를 통하여 전력을 부하로 전달하게 된다. 퓨즈와 릴레이는 부하에 서 단락이나 과전류가 발생하는 경우 물리적으로 시스템을 보호하는 기능을 갖게 되지만, LCL은 부하에서 생기는 과전류를 적정한 레벨로 제한하 고, 정의된 시간까지 과전류가 유지되는 경우 차 단하게 되는 보다 유연한 기능을 갖추고 있다. 그러나 LCL은 전자회로로 구현되는 만큼 주변 회로(부하)와의 연동성과 회로 자체의 특성을 이 해해야 하며, 무엇보다 과전류를 차단하기 위한 LCL trip-off 레벨을 정의하는 기술적인 접근이 요구된다. 따라서 본 문서에서는 LCL 구현과 그 와 관련한 파라미터를 정의할 수 있는 접근 방법 에 대하여 기술하였다.

항공우주기술 제10권 제2호

# 참 고 문 헌

- 1. K3A-SP-410-001, "BUS EMC Requirements Specification", June 2010.

- 2. K3A-D0-390-005, "Fuse Sizing Technical Document", March 2011.

- 3. 임성빈, "Background for definition of the LCL trip-off limit", IOC, Feb. 2009.

- 4. 서현석 et al., "과도 열 해석을 이용한 Power FET 열 특성 분석에 관한 연구", 항공우주학회, KSAS07-3238, pp.1733-1736, 2007.

- Muhammad H. Rashid, Power Electronics Circuits, Devices, and Application, Second Edition, John & Wiley Sons Ltd. 1982.

- 6. AN-949, "Current Rating of Power Semiconductors, Application Note", IR.

- 7. PD-94283C, IRHMS597160 Data Sheet, IR, 2005