# DDR2 SDRAM을 이용한 비메모리 검사장비에서 정시성을 보장하기 위한 메모리 컨트롤러 개발

# Development of Memory Controller for Punctuality Guarantee from Memory-Free Inspection Equipment using DDR2 SDRAM

전민호\*, 신현준\*, 강철규\*, 오창헌\*

Min-ho Jeon\*, Hyun-jun Shin\*, Seung-Heui Jeong\* and Chang-Heon Oh\*

#### 요 약

현재의 반도체 검사장비는 테스트 패턴 프로그램을 위한 메모리로 시스템 설계가 간단하고 리프레시가 필요 없는 SRAM(static random access memory) 모듈을 채용하고 있다. 그러나 SRAM 모듈을 이용한 시스템 구성은 용량이 커질수록 장비의 부피가 증가하기 때문에 메모리 대용량화 및 장비의 소형화에 걸림돌이 되고 있다. DRAM(dynamic random access memory)을 이용하여 반도체 검사 장비를 제작할 경우 SRAM 보다 비용과 장비의 면적이 줄어드는 장점이 있지만 DRAM의 특성 상 메모리 셀 리프레시가 필요하여 정시성을 보장해야 하는 문제가 있다. 따라서 본 논문에서는 이러한 문제를 해결하기 위해 DDR2 SDRAM(double data rate synchronous dynamic random access memory)을 이용한 비메모리 검사장비에서 정시성을 보장해 주는 알고리즘을 제안하고 알고리즘을 이용한 메모리 컨트롤러를 개발하였다. 그 결과, DDR2 SDRAM을 이용할 경우 SRAM을 이용할 때 보다 가격과 면적이 줄어들어 가격측면에서는 13.5배 그리고 면적측면에서는 5.3배 이득이 있음을 확인하였다.

#### **Abstract**

The conventional semiconductor equipment has adopted SRAM module as the test pattern memory, which has a simple design and does not require refreshing. However, SRAM has its disadvantages as it takes up more space as its capacity becomes larger, making it difficult to meet the requirements of large memories and compact size. if DRAM is adopted as the semiconductor inspection equipment, it takes up less space and costs less than SRAM. However, DRAM is also disadvantageous because it requires the memory cell refresh, which is not suitable for the semiconductor examination equipments that require correct timing. Therefore, In this paper, we will proposed an algorithm for punctuality guarantee of memory-free inspection equipment using DDR2 SDRAM. And we will Developed memory controller using punctuality guarantee algorithm. As the results, show that when we adopt the DDR2 SDRAM, we can get the benefits of saving 13.5 times and 5.3 times in cost and space, respectively, compared to the SRAM.

Key words: Controller module, Semiconductor inspection equipment, Memory-free, Test pattern memory, Punctuality guarantee algorithm

Ⅰ. 서 론

최근 반도체 개발 공정 미세화에 따른 집적도 증

<sup>\*</sup> 한국기술교육대학교

<sup>·</sup> 제1저자 (First Author) : 전민호 · 투고일자 : 2011년 10월 12일

<sup>·</sup> 심사(수정)일자 : 2011년 10월 12일 (수정일자 : 2011년 12월 26일)

<sup>·</sup> 게재일자 : 2011년 12월 30일

가와 이를 이용한 대용량 시스템 IC(integrated circuit) 의 출현으로 이를 테스트하기 위한 테스트 장비도 대용량화가 되고 있다. 여기서 대용량화란 주로 테스트 패턴 프로그램 메모리의 대용량화와 fail 메모리의 대용량화를 의미한다. 메모리 제품의 경우 그림 1과 같이 반복적인 테스트 패턴을 이용하기 때문에 ALPG (algorithm pattern generator)를 사용함으로써 프로그램 메모리 용량을 수십 [Kb]로 작게 사용할 수 있으나, 시스템 IC와 같은 비메모리 반도체 제품의 경우 그림 2와 같이 테스트 패턴이 반복적이지 않기 때문에 모든 테스트 패턴을 반복 명령어 없이 순차적으로 기술해 주어야 한다. 이러한 특성 때문에 시스템 IC의 용량이 증가함에 따라 비메모리 검사 장비의 테스트 패턴 메모리의 용량도 증가해야한다[1][2].

그림1. 메모리의 테스트 패턴 Fig. 1. test pattern of Memory

| 비메모리 로적     |            |            |            |         |     | 비메모리 테스트 패턴 |            |              |

|-------------|------------|------------|------------|---------|-----|-------------|------------|--------------|

| 기능<br>blk1  | 기능<br>blk2 | 기능<br>blk3 | 기능<br>blk4 | Line 1  | nop | IO0 format  | IO1 format | 102 format   |

| 기능          | 기능         | 기능         | 기능         | Line 2  | пор | 100 format  | 101 format | IO2 format   |

| blk5        | blk6       | blk7       | blk8       | Line 3  | nop | 100 format  | IO1 format | IO2 format   |

| 기능<br>blk9  | 기능<br>bk10 | 기능<br>bk11 | 기능<br>bk12 | Line 4  | nop | IO0 format  | IO1 format | IO2 format   |

| 기능<br>blk13 | 기능<br>bk14 | 기능<br>bk15 | 기능<br>bk16 | Line 16 | nop | IO0 format  | IO1 format | • 102 format |

그림2. 비메모리의 테스트 패턴 Fig. 2. test pattern of Memory-free

현재의 비메모리 검사장비는 프로그램 메모리로 모두 SRAM 모듈을 채용하고 있다. 그 이유는 SRAM 모듈은 플립플롭을 이용하여 개발되었기 때문에 메모리 셀 리프레시(memory cell refresh)가 필요하지 않기 때문에 타이밍 제어가 간단하여 시스템 설계가 간단해지기 때문이다. 그러나 SRAM 모듈을 이용한 시스템 구성은 용량이 커질수록 장비의 부피가 증가하기 때문에 메모리 대용량화 및 장비의 소형화에 걸림돌이 되고 있다. 이러한 문제로 반도체 검사장비들중 fail 메모리와 같은 정시성이 요구되지 않는 데이터 메모리에는 가격 및 점유면적을 고려하여 SRAM 대신에 DRAM을 사용하고 있으나, DRAM의 메모리셀 리프레시 때문에 정시성을 보장해야하는 테스트패턴 메모리에는 적합하지 못한 문제가 있다[3].

본 논문에서는 이러한 문제를 해결하기 위해 비메

모리 검사장비에서 테스트 패턴 프로그램 메모리로 DDR2 SDRAM을 사용하기 위한 정시성 보장 알고리 즘을 제안하고 알고리즘을 이용한 메모리 컨트롤러를 개발하였다.

본 논문의 구성은 2장에서는 관련기술의 현황을 설명하고 3장에서는 제안한 시스템의 알고리즘에 대해 설명하고 4장에서는 메모리 컨트롤러를 구현하고 5장에서는 개발한 메모리 컨트롤러를 실험을 통하여평가한다. 그리고 마지막 6장에서 결론을 맺는다.

#### Ⅱ. 기존 산업용 장비 시스템 구조

소프트웨 기술은 모듈화 된 장비 O/S 구조와 네트워크에 사용되는 프로그램, 유사한 유틸리티 프로그램으로 구성되어 대부분의 반도체 검사장비에 공용으로 적용될 수 있다. 또한 이들 장비를 구성하는 하드웨어 핵심 기술은 다음과 같다. 이들 개개의 기술들은 20MHz · 200MHz 로직 및 메모리 겸용장비에서도 하이스피드에 필요한 설계 변경과 용도에 따른 주변부 기능을 제외한 코어(Core)기능들은 대부분 그대로 사용이 가능하다.

# 2-1 ALPG(algorithmic pattern generator) 기술

메모리 테스트에 필요한 어드레스 및 데이터 신호 생성 전용으로 개발된 일종의 ALU이다. 이 기술은 메모리 테스터의 핵심 기술로서 복잡한 메모리 테스 트 패턴을 간편하게 만들어 주는 역할을 한다.

#### 2-2 Bit Pattern Generator 기술

비메모리 제품을 테스트 하는데 필요한 벡터 신호를 만들어주는 회로로 벡터 메모리 자원을 최대한 효율적으로 운용할 수 있다.

#### 2-3 Flexible Zone 기술

모든 슬롯이 하나의 존으로 사용될 수 있는 full zone 시스템에서 임의의 슬롯을 지정하여 하나의 존으로 설정할 수 있는 기능으로서, 하나 이상의 슬롯을 차지하는 제품 테스트 시 하나로 묶어 진행이 가능하므로 생산이 편리하고 관리가 쉽게 된다.

#### 2-4 Free Zone 기술

핵심 모듈인 신호 발생기와 서브 컨트롤러를 선택 사양화 하여, 단순히 신호 발생기나 서브 컨트롤러의 수에 따라 설비 모델이 달라지는 문제점을 없앰으로 써 제품관리가 획기적으로 단순화 된다. 또한 유저로 하여금 사후 제조 환경 변화에 따른 업그레이드가 가 능하게 하였다.

#### 2-5 파워보드 개발기술

대용량 전원 장치와 복잡한 배선에 의한 전원 공급 체계를 파워 보드라는 형태로 각 모듈에 분산 배치하여 전원 시스템을 획기적으로 단순화 하여, 설비내부 구조를 simple하게 할 수 있는 기술이다.

#### 2-6 Addressed IO 기술

기존에 어드레스로만 사용되던 회로를 데이터로 도 사용할 수 있도록 하여, 어드레스 신호를 사용하 지 않는 플래시 메모리 테스트 시 생산성을 두 배로 늘려주는 기술이다.

#### 2-7 200MHz(400MHz) 서브 컨트롤러 기술

리눅스 기반의 200MHz ARM CPU 보드이다.

#### 2-8 데이터 스왑 기술

차세대 고 부가가치 메모리 제품인 퓨전 메모리 (fusion 메모리)에 적합한 기능으로서, 신호를 쉽게 가공하면서 어드레스/데이터 신호의 순서를 원하는데로 바꾸어 주는 기술이다.

#### 2-9 테스트 시스템 O/S 프로그램 기술

하드웨어 기술을 가지고 있어도 이를 응용할 수 있는 프로그램 제작 기술이 없으면 한정된 용도로 사용할 수밖에 없다. 따라서 테스터를 컨트롤할 수 있고 용도에 맞추어 프로그램을 개발할 수 있는 기술과테스트 장비용으로 개발된 operating 시스템용 프로그램이 필요하며, 구체적으로는, 장비를 구동하는 BIT와 IBC, 고장 진단을 위한 diagnostic 프로그램, 테

스트 프로그램 작성을 용이하게 하는 debugger/simulator, on-line 고장 수리가 가능한 bug tracking 시스템 등이 있다.

#### Ⅲ. DDR2 SDRAM 컨트롤러 모듈 설계

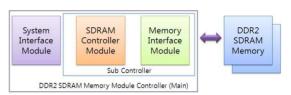

그림 3은 본 논문을 통해 개발하고자 하는 비메모리 반도체 검사장비 테스트 패턴 프로그램 메모리용 DDR2 SDRAM 컨트롤러 모듈의 구성도이다.

그림 3. DDR2 SDRAM 모듈 컨트롤러 구성도 Fig. 3. Schematic of DDR2 SDRAM module controller

그림 3의 시스템 인터페이스 모듈은 반도체 검사 장비와 DDR2 SDRAM 모듈 컨트롤러를 연결시켜주 는 역할을 하는 것으로 ISA(industry seabed architecture)와 유사한 방식을 취하며, Address(15), Data(16), IO(input/output), WR(write), RD(read), RES(remote entry service)를 사용한다.

메모리 인터페이스 모듈은 VHDL(VHSIC hardware description language)을 사용하여 기능을 구현할 예정이다. 이 모듈에서 DDR SDRAM 모듈에 공급되는 신호는 RAS(row address signal), CAS(column address signal), WE(write enable), CS(chip select)와 같은 제어신호와 멀티플렉스 된 Row, Column 어드레스 신호, 양방향의 데이터 신호이며, 고속으로 동작하도록 설계되었다[5][6].

마지막으로 SDRAM 컨트롤러 모듈은 4장에서 설명하는 정시성 보장알고리즘을 이용하여 설계된다.

#### Ⅳ. 정시성 보장 알고리즘

DRAM은 이 비트를 집적회로 안에 각기 분리된 축전지에 담긴 전하량에 의해 기록하며 시간이 지남에 따라 축전기의 전자가 누전됨으로써 기억된 정보를 잃게 된다. 이를 방지하기 위해 기억장치의 내용을 주기적으로 재생시켜야하는데 이를 리프레시라고

하며 리프레시를 위한 제어회로가 컴퓨터 시스템에 탑재되어 있어야 한다.

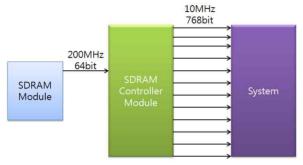

그림 4와 같이 SDRAM의 사용을 위해서는 필히 SDRAM 컨트롤러가 필요하다. 보통의 ARM 코어 내 장형 SoC(system on chip)에는 기본적으로 이런 SDRAM 컨트롤러가 존재한다. 컨트롤러의 가장 중요한 역할은 SDRAM의 데이터 보관과 리프레시이다.

그림 4. DRAM의 호스트 인터페이스 Fig. 4. Host interface of DRAM

SDRAM으로 전송되는 신호들 중 DQx 데이터 버스를 제외한 대부분은 SDRAM 컨트롤러에서 보내는 신호들이다. 표 1은 SDRAM 컨트롤러에서 보내는 신호들 중 주요 신호에 대해서 정리해 놓은 것이다.

리프레시 주기는 메모리칩에서 메모리의 내용을 읽거나 쓸 수 없는 특별한 구간이며 SDRAM 컨트롤러의 가장 중요한 임무는 시스템의 요구에 맞게 리프레시주기를 보장해 주는 것이다. 본 알고리즘에서는 정시성을 보장하기 위한 리프레시로 오토 리프레시를 사용하였다. 기본적으로 리프레시 명령은 SDRAM 컨트롤러에서 발생되며 오토 리프레시는 항상 'IDEL' 상태에서만 동작한다.

표 1. SDRAM의 신호와 기능 Table 1. signal and function of SDRAM

| 신호               | 기능                         |

|------------------|----------------------------|

| CLK              | Memory Clock               |

| CKE              | Clock Enable               |

| CS               | Chip Select                |

| RAS              | Row Address Select         |

| CAS              | Column Address Select      |

| WE               | Control Signal             |

| V(cc,ss,ccQ,ssQ) | Power                      |

| A0-Ax            | Address                    |

| DQM              | masking signal of data I/O |

| DQ0-DQx          | data I/O                   |

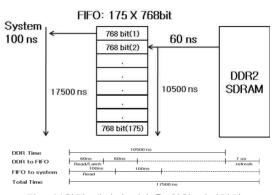

그림 2는 리프레시로 인한 오류를 제거하기 위한 계층별 데이터 전송 시간을 나타낸 그림이다. DDR2 SDRAM 모듈에서 DDR2 SDRAM 컨트롤러로 데이터가 들어오는 시간은 10,500 ns이며, DDR2 SDRAM 컨트롤러에서 시스템으로 데이터를 전송하는 시간은 17,500 ns로 7000 ns의 여유 시간을 가지게 되며, 이여유시간동안 DDR2 SDRAM은 리프레시를 수행하게 된다[4].

그림5. 분할된 데이터 전송을 위한 타이밍차트 Fig. 5. Timing chart for the divided data transmission

# V. 정시성을 보장하는 DDR2 SDRAM 컨트롤러 모듈 개발

위에서 언급한대로 DDR2 SDRAM 컨트롤러 모듈 은 VHDL을 사용하여 기능을 구현하였다.

그림 6. DDR2 SDRAM 컨트롤러 모듈 메인 Fig. 6. DDR2 SDRAM Controller module main

DDR2 SDRAM 컨트롤러 모듈은 그림 7와 같이 DDR2 SDRAM 모듈에서 받아온 데이터를 그림 5의 FIFO(first in first out)형식의 저장 공간에 데이터를 순차적으로 저장하고 먼저 받은 데이터부터 시스템으로 전송시키는 역할을 하며 각 모듈사이의 동작속도는 200MHz와 10MHz로 제어를 하였으며 DDR2 SDRAM 컨트롤 모듈에서 시스템으로 전송되는 패킷은 12개로 분할하여 전송하게 하였다.

그림 7. 더미 사이클 제거를 위한 데이터 분할 전송 알고리즘 Fig. 7. Algorithm of data divided transmission for the dummy cycle elimination

# Ⅴ. 시스템 구현 및 성능평가

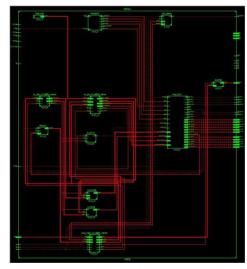

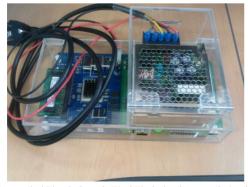

본 장에서는 정시성 보장 알고리즘으로 구현된 DDR2 SRAM 메모리 컨트롤러의 성능을 평가하기 위해 비메모리 검사장비의 테스트 패턴 메모리 보드를 구현하고 시스템과의 데이터 통신에서 발생하는 오류율을 측정하였다. 그림 8는 본 논문의 실험에 사용될 비메모리 검사장비의 테스트 패턴 메모리 보드의 모습이다.

그림 8. 개발된 비메모리 검사장비의 테스트 패턴 메모리 보드

Fig. 8. Developed test pattern memory board of memory-free inspection equipment

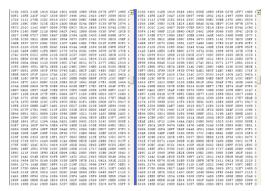

실험은 비메모리 검사장비 시스템을 대신하여 시뮬레이터에서 임의로 데이터를 생성한 후 생성한 데이터를 'write.txt' 파일에 저장시켜 놓은 후 DDR2 SDRAM 메모리에 저장을 하였다. 그런 다음 DDR2 SDRAM 메모리에 저장을 하였다. 그런 다음 DDR2 SDRAM 메모리로부터 현재 메모리에 저장된 주소공간의 데이터를 순차적으로 불러들여 'readl.txt' 파일로 저장시킨 후 'write.txt' 파일과 비교하였다. 실험결과 134,400 bit가 입력된 'write.txt'파일의 데이터와 'read.txt'파일을 비교한 결과 데이터가 오류 없이 성공적으로 출력되는 것을 확인 할 수 있었다.

그림 9. Read data text와 write data text의 비교 Fig. 9. Comparison between read data text and write data text

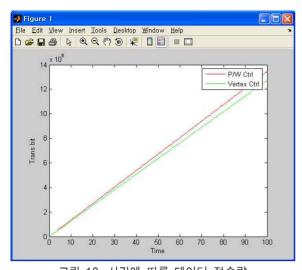

그림 10은 본 논문에서 제안한 정시성 보장알고리 즘을 사용한 메모리 컨트롤러와 Vectex-5에서 기본적으로 제공하는 오토 리프레시를 이용하여 제작한 메모리 컨트롤러와 비교한 그래프이다. 오토리프레시를 사용 할 경우 초반에는 아주 미세한 차이로 P/W ctrl(Punctuality Guarantee memory controller) 보다 데이터 전송량이 많지만 시간이 지남에 따라 P/W ctrl이 더욱 많은 데이터를 전송하는 것을 알 수 있다. 이는 vectex-5에서 제공하는 오토리프레시는 지속적으로 데이터를 전송하고 리프레시 주기가 돌아왔을 때데이터 전송을 잠시 멈추고 리프레시를 수행하고 난후 다시 데이터를 전송하는데 반해 본 논문에서 제안한 정시성 보장알고리즘을 사용할 경우 리프레시 구간에도 메모리 컨트롤러 내부에 저장된 데이터를 지속적으로 전송하기 때문이다.

그림 10. 시간에 따른 데이터 전송량

Fig. 10. Data transmission rate according to time

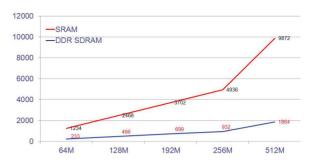

표 2는 SRAM 컨트롤러 모듈과 본 논문에서 개발 한 DDR2 SDRAM 컨트롤러 모듈로 변경하였을 경우 장비를 개발할 때 필요로 하는 기본재료 비용과 개발 된 장비의 크기를 비교한 표이다.

그 결과, DDR2 SDRAM을 이용할 경우 SRAM을 이용할 때 보다 가격과 면적이 줄어들어 가격측면에 서는 13.5배 그리고 면적측면에서는 5.3배 이득이 있음을 확인하였다.

표2. 장비개발 가격 및 면적 비교 Table 2. Comparison between inspection develop ment cost and space

| 7.11     | 필요 모듈 수         | 단위 가격       | - 합계                   |  |  |  |  |  |  |

|----------|-----------------|-------------|------------------------|--|--|--|--|--|--|

| 구분       | <b>夏</b> 亚 五五 上 | 단위 크기       |                        |  |  |  |  |  |  |

| 64M × 64 | 12 EA           | 19,000      | 228,000                |  |  |  |  |  |  |

| SDRAM    | 12 EA           | 6.7×2.9 Cm  | 233(Cm <sup>2</sup> )  |  |  |  |  |  |  |

| 8M × 192 | 22 EA           | 96,000      | 3,072,000              |  |  |  |  |  |  |

| SRAM     | 32 EA           | 13.3×2.9 Cm | 1234(Cm <sup>2</sup> ) |  |  |  |  |  |  |

| 효과       |                 | 가격          | 13.5时                  |  |  |  |  |  |  |

| 五叶       |                 | 면적          | 5.3배                   |  |  |  |  |  |  |

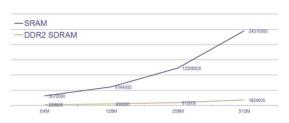

그림 11과 그림 12는 표 2의 결과를 이용하여 비메모리 검사장비의 테스트패턴 메모리의 증가에 따른 면적 및 가격을 비교한 그래프이다. 테스트 패턴 메모리의 용량이 증가함에 따라 SRAM을 이용할 경우장비의 면적 및 개발비용이 크게 상승하지만 DDR SDRAM을 이용할 경우 SRAM과 비교해서 장비의 면적과 개발비용이 상당히 낮은 것을 알 수 있다.

그림 11. 비메모리 검사장비의 테스트 패턴 메모리용량에 따른 면적 비교

Fig. 11. Space comparison according to the capacity of the test pattern memory in non-memory inspection equipment.

그림 12. 비메모리 검사장비의 테스트 패턴 메모리용량에 따른 가격 비교

Fig. 12. Cost comparison according to the capacity of the test pattern memory in non-memory inspection equipment.

#### Ⅴ. 결 론

최근 반도체 공정의 미세화에 따른 반도체 검사장비 프로그램 메모리의 대용량화에 대한 연구가 활발히 진행 중이다. 현재의 반도체 검사장비는 테스트패턴 프로그램을 위한 메모리로 시스템 설계가 간단하고 리프레시가 필요 없는 SRAM 모듈을 채용하고 있으나 SRAM은 DRAM에 비해 구조적으로 4배의 면적을 차지하기 때문에 메모리의 대용량화 및 장비의소형화가 어렵고 동일 용량을 구성하기 위한 비용이많이 요구된다. 이에 비해 DRAM은 저가이고 소형화가 가능하여 대용량 저장장치로 많이 사용되고 있으나, 정확한 타이밍 제어가 어렵기 때문에 정시성이요구되지 않는 장비에만 사용되고 있다.

따라서 본 논문에서는 이러한 문제를 해결하기 위해 DDR2 SDRAM을 이용한 비메모리 검사장비에서 정시성을 보장해 주는 알고리즘을 제안하고 알고리즘을 이용한 메모리 컨트롤러를 제작하였다.

그 결과, 정시성 보장알고리즘을 사용할 경우 기

존의 오토리프레시를 이용하는 SDRAM 메모리 컨트롤러 보다 메모리 셀 리프레시의 영향 없이 시스템으로 데이터를 전송하는 것을 확인하였으며, 본 논문에서 개발한 DDR2 SDRAM 메모리 컨트롤러를 이용하여 비메모리 검사 장비를 개발할 경우 개발비용은 약13.5배 그리고 장비가 차지하는 면적은 5.3배 줄어드는 것을 알 수 있었다.

#### 참 고 문 헌

- [1] 전자엔지니어. [Online]. Available: http://www.eetkore a.com/ART 8800324662 480703 NT 63eb10ba.HTM

- [2] 권오범, 한혜정, 김계영, "반도체 공정 실시간 자동 진단 시스템," *한국정보과학회 학술발표논문집*, 제 30권 제1호, pp. 241~243, 2003.

- [3] J. Han and M. Kamber, *DataMining : Concepts and Techniques*, 2nd Edition. Morgan Kaufmann, Nov. 2005.

- [4] O. A. S. Youssef,"An optimized fault classification technique based on Support- Vector-Machines," *Power Systems Conference and Exposition(PES)*, pp. 1~8, Mar. 2009.

- [5] 노웅기, 홍상진,"반도체공정 이상탐지 및 클러스터 링을 위한 심볼릭 표현법의 적용," *정보과학회 논문* 지: 컴퓨팅의 실제 및 레터, 제15권 제11호, pp. 806~818, 2009. 11.

- [6] 임신영, 허재두, 박광로, 김채규, "상황인식컴퓨팅기 술동향," *IITA 주간기술동향*, 제1142호, 2004. 04.

- [7] Mari Korkea-aho, "Context-Aware Applications Survey," Department of Computer Science, Helsinki university of Technology, 2000.

- [8] 정덕진, 송병철, 이승열, 조위덕, "상황인지 센서네 트워크 기술동향," *정보통신 기술*, 제18권, 제1호, pp. 1-109, 2004. 5.

#### 신 현 준 (愼炫俊)

2011년 2월 : 남서울대학교(공학사) 2011년 3월 ~현재 : 한국기술교육대학교 전기전자통신공학부 (석사과정) 관심분야 : LTE, MIMO, Channel Coding

# 강 철 규 (姜澈圭)

2004년 2월 : 한국기술교육대학교 정보기술공학부(공학사) 2006년 2월 : 한국기술교육대학교 대학원 전기전자공학과(공학석사) 2007년 9월 ~ 현재 : 한국기술교육대학교 대학원 전기전자공학과(박사과정)

20011년 10월 ~ 현재 : 한국전자부품연구원 RFID/USN 융합센터 연구원

관심분야: MIMO, Wireless Sensor N/W

## 전 민 호 (田旻浩)

2009년 2월 : 극동대학교 게임디지털컨텐츠학과 (공학사) 2009월 8월~현재 : 한국기술교육대학교 전기전자공학과 (석사과정) 관심분야 : 무선통신, 무선센서네트워크, RFID/USN

# 오 창 헌 (吳昌憲)

1988년 2월 : 한국항공대학교 항공통신공학과 (공학사) 1990년 2월 : 한국항공대학교 대학원항공통신정보공학과 (공학석사) 1996년 2월 : 한국항공대학교 대학원 항공전자공학과 (공학박사) 1990년 2월~1993년 8월: 한진전자(주)

기술연구소 전임연구원

1993년 10월~1999년 2월: 삼성전자(주) CDMA 개발팀 선임연구원

1999년 2월~현재: 한국기술교육대학교 정보기술공학부 교수 2006년 8월~2007년 7월: 방문교수(University of

Wisconsin-Madison)

관심분야: 이동통신, 무선통신, Wireless Sensor N/W, CR