# 전극 표면의 거칠기가 펜터신/전극 경계면의 전류-전압 특성에 주는 영향

김우영 · 전동렬\*

서울대학교 물리교육과, 서울 151-748

(2010년 9월 29일 받음, 2011년 2월 14일 수정, 2011년 2월 18일 확정)

금속 전극 위에 유기물 채널을 증착하여 만드는 바닥 전극 구조의 유기물 박막 트랜지스터에서 전극 표면이 거친 정도에 따라 전하 주입이 어떻게 달라지는지 조사했다. 금 전극을 실리콘 기판에 증착하고, 가열하여 금 전극 표면을 거칠게 만들었다. 그리고 펜터신과 상부 전극으로 사용할 금 전극을 차례대로 증착하여 금 전극/펜터신/금 전극 구조를 만들었다. 펜터신 증착 초기에는 거친 금 전극 위에서 펜터신 증착핵이 더 많이 보였지만, 막이 두꺼워지면 가열되지 않은 전극과 가열로 거칠어진 전극에서 펜터신 표면 모양에 차이가 거의 없었다. 온도를 바꾸면서 측정한 전류—전압 곡선은 바닥 전극의 표면이 거칠수록 바닥계면의 전위장벽이 높음을 보여주었다. 이 현상은 금속 표면이 거칠수록 일함수가 낮아지며 펜터신과 거친 전극 표면의 경계에 전하 트랩이 더 많기 때문으로 생각된다.

주제어: 펜터신, 계면의 전위장벽, 전극 표면의 거칠기, 전하 주입

#### I. 서 론

유기물 소자의 다양한 응용성과 높은 가능성은 많은 관심을 불러 일으켰으며 소자의 특성을 이해하고 성능을 개선하기 위한 연구가 끊임없이 이루어지고 있다. 무기물 전자 소자를 대체하기 위한 유기물 박막 트랜지스터 [1], 유기물 발광 다이오드 [2], 유기물 태양전지는 [3] 물론, 휘어지는 평판 디스플레이에는 무기물 박막 대신 유기물 박막을 사용할 수밖에 없다 [4,5]. 여러 유기물 재료 중에 펜타신이 가장 많은 주목을 받아왔는데 [6], 펜터신 다결정의모빌리티가 1 cm²/V·s로 다른 유기물 다결정 박막에 비해높고 on/off 비율도 높기 때문이다. 이 때문에 펜터신을 유연성, 저온공정, 비용 절감의 장점을 가진 유기물 전자 소자에 이용하기 위해 모빌리티와 전류 밀도를 개선하려는노력이 활발하다 [7,8].

실리콘/금속 전극의 경계면이 지난 수십 년간 연구되어 특성이 잘 파악되고 소자 성능 제어에 유용하게 이용되고 있는 반면에 반도체 유기물/금속 전극 경계면 연구의 기간 은 그리 오래 되지 않은데다, 유기물 박막이 다결정이고 성 장 제어가 어렵기 때문에 특성을 파악하기가 어렵다 [9]. 우수한 특성을 가진 유기물 재료의 개발도 중요하지만 우

수한 성능의 유기물 전자 소재의 제작을 위해 전극과의 경 계면 물성 파악도 매우 중요하다. 펜터신 소자의 특성에 영 향을 주는 물리적 요소로 펜터신과 금속 전극의 경계면에 서 금속 표면의 거칠기와 일함수 차이에 의한 전위장벽을 들 수 있다 [10]. 바닥 전극의 경우에는 펜터신 박막의 기판 이 되는 금속 바닥 전극의 표면 거칠기가 펜터신 그레인의 형태와 경계면에서 전하 이동에 큰 영향을 줄 수 있기 때문 이다. 그렇지만 지금까지의 경계면 연구는 주로 펜터신 박 막의 물성 차이에 의한 경계면 물성 변화에 초점을 맞추었 고, 바닥 전극의 거칠기에 의한 경계면의 특성 차이를 고려 한 연구 보고는 별로 없다. 이 연구에서는 표면 거칠기가 다른 금 박막을 만들어 그 위에 펜터신 박막을 만들고 전압 -전류 특성을 측정하여 금 전극의 표면 거칠기에 따라 경 계면에서 전하 주입의 활성도를 알아보았다. 열증착으로 만든 금 전극을 높은 온도에서 가열하여 거칠게 만들고 그 위에 펜터신 다결정 박막을 키워서 만든 시료에서 측정한 전류-전압 자료에 의하면 거칠기 계수가 작을수록 전위장 벽이 낮게 나타났다.

<sup>\*[</sup>전자우편] jeon@snu.ac.kr

#### Ⅱ. 실험 방법

이 실험에서 소자 제작을 위해 사용한 실리콘 웨이퍼는 500 nm 두께의 산화막이 형성된 기판으로, 펜터신/금 전 극 시료 제작을 위해 기판에서 1.8×1.8 cm 조각을 잘라내 었다. 세정 과정을 거친 뒤에 압력이 1.7×10<sup>-7</sup> Torr인 진 공 챔버에서 금 접착을 돕기 위해 5 nm 두께의 크롬을 증 착하고 나서 금을 가열하여 50 nm 두께의 박막을 증착했 다. 박막의 두께는 수정 결정을 이용하여 측정했다. 증착한 금 박막의 거칠기를 다르게 만들기 위해 공기 중에서 시료 를 가열판에 올려놓고 400°C로 30분 동안 가열하고 주사 프로브 현미경(atomic force microscope, AFM)으로 거칠 기를 측정했다. 거칠기를 결정하는 방법은 여러 가지가 있 는데, 이 연구에서는 시료 표면의 AFM 영상에서 여러 곳 의 선 윤곽을 얻고, 선 윤곽의 중간에 수평선을 그은 다음 각 지점의 높이가 중심선에서 얼마나 위 또는 아래로 벗어 나있는지를 합하여 평균을 내는 중심선 평균 거칠기 산출 방법을 이용했다 [11].

같은 조건으로 펜터신 박막을 키우기 위해 거칠기가 다 른 금 전극에 같은 조건으로 펜터신 박막을 키우기 위해 거 칠기가 다르게 조절된 금 전극 기판을 동시에 압력이  $2 \times 10^{-7}$  Torr인 진공 챔버에 넣고 펜터신 박막을 0.5 Å/ min의 속도로 500 nm가 되게 증착했다. 전류-전압을 측 정하기 위해 필요한 두 번째 금 전극을 펜터신 박막 위에 열증착 방법으로 만들었다. 바닥 금 전극의 거칠기는 달라 도 펜터신 위쪽의 금 전극은 같은 조건으로 만들기 위해 앞 에서 만든 펜터신/바닥 금 전극 시료를 동시에 진공 챔버에 넣고 열증착으로 위쪽 금 전극 박막을 올렸다. 펜터신에 금 전극을 입힐 때 펜터신 기판의 온도가 높으면 증착된 금 알 갱이가 펜터신 속으로 파고 들어가서 펜터신의 그레인이 심하게 파괴되거나 지나친 경우에는 위쪽 금 전극과 바닥 금 전극이 맞붙는다 [12,13]. 이를 방지하기 위해 펜터신이 증착된 기판을 액체 질소를 사용하여 -150°C로 냉각시킨 상태에서 0.2 Å/min의 속도로 200 nm가 되도록 금 박막 을 증착했다 [14.15]. 증착하는 동안 진공 챔버의 압력은 4×10<sup>-7</sup> Torr를 유지했다.

전류-전압 곡선 측정시 공기중 수분이 펜터신 소자에 미치는 영향을 없애기 위해  $2\times10^{-7}$  Torr 진공 챔버에서 실시했다. 위쪽 금 전극/펜터신/바닥 금 전극에서 바닥 전극은 접지시키고 위쪽 전극에 전압을 가하면서 펜터신을 통해 흐

르는 전류를 측정했다. 펜터신/바닥 금 전극 경계면의 전위 장벽이 전극 표면의 거칠기에 따라 어떻게 변하는지 조사하 기 위해 시료의 온도를 240 K에서 330 K까지 10 K 간격으 로 바꾸면서 전류-전압을 측정하여 쇼트키 방출(Schottky emission) 모델로 분석했다.

## III. 결과 및 고찰

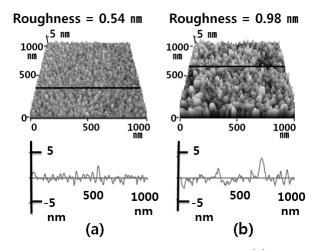

처음 열중착된 그대로의 금 전극 표면과 거칠기를 조절하기 위해 가열한 금 전극 표면의 AFM 영상과 대표적인 위치의 선 윤곽을 Fig. 1에 나타냈다. 가열하지 않은 경우에는 Fig. 1(a)에서 보듯 금 그레인의 크기가 일정하며, 임의로 선택한 (그림에 선으로 표시한) 횡단면에서 최고점과 최저점의 높이 차이가 4 nm 이내다. 중심선 평균 거칠기는 시료의 각 지점이 시료 전체의 평균 높이에서 벗어난 정도를 보여준다. 가열하기 전의 중심선 평균 거칠기는 0.54 nm인데, 금 전극을 공기 속에서 400°C로 30분 가열하고나니 Fig. 1(b)에서 보듯 중심선 거칠기는 0.98 nm로 증가했고 임의로 선택한 (그림에 선으로 표시한) 횡단면에서 최고점과 최저점의 차이도 6 nm로 증가했다. Fig. 1의 AFM 영상은 가열된 다음에 그레인의 크기는 커지고 수는 줄어드는 상태를 보여주는데, 이것은 높은 온도에서 작은 그레

Figure 1. AFM images and line profiles of (a) Au film as-deposited on the Si substrate and (b) the Au film annealed at 400°C for 30 min. The surface roughness increased upon annealing. Line profiles presented were taken along the horizontal lines in the images.

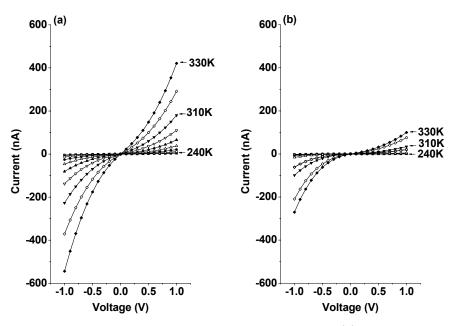

Figure 2. Current-voltage curves as a function of temperature obtained from (a) the Au/pentacene/as-deposited-Au-bottom-electrode and (b) the Au/pentacene/roughened-Au-bottom-electrode. The current has decreased for the roughened-Au-bottom-electrode. Temperature was varied from 240 K to 330 K with 10 K interval. The current increases with the rising temperature.

인의 금 입자들이 이동하면서 큰 그레인으로 합쳐지기 때문이다. 우리가 만든 여러 시료를 비교하면, 가열 온도가 높을수록 그레인의 크기에 편차가 많이 나고 그레인의 꼭 대기가 둥글게 변하여 종횡비가 작아짐을 알 수 있었다.

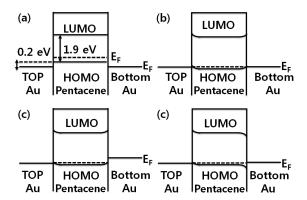

Fig. 2는 바닥 전극 표면의 거칠기가 다른 두 시료의 온 도에 따른 전류-전압 측정 결과를 보여준다. 두 시료 모두 온도가 높을수록 전류가 크지만 시료에 따라 전류-전압 곡 선의 모양에는 차이가 있다. 즉, 가열되지 않은 시료는 양 과 음전압에 대해 전류가 거의 대칭이지만 [Fig. 2(a)], 가 열된 시료는 바닥 전극에 음전압이 걸렸을 때가 순방향인 정류 현상이 증가했다 [Fig. 2(b)]. 정류 현상은 금속과 반 도체의 페르미 준위가 서로 다를 때 둘의 경계면에 형성되 는 쇼트키 장벽 때문에 일어난다. 펜터신/금 경계에서는 Fig. 3(a)에서 보듯 금의 페르미 준위가 펜터신의 highest occupied molecular level (HOMO)보다 조금 낮지만 [16] 차이가 작기 때문에 거의 오믹 접합으로 간주한다. 그러나 금(111) 단결정 표면에 펜터신을 증착했을 때 Fig. 3(b)에 서 보듯 금의 페르미 준위가 펜터신의 HOMO보다 높아져 서 경계면에 전위장벽이 생겼는데, 이것은 펜터신/금 경계 에 형성된 쌍극자 면 때문이다 [17]. 가열하지 않은 시료의 전류-전압 곡선인 Fig. 2(a)는 전류가 양, 음전압에 대해 대칭이고 전압에 지수함수로 증가하는데, 이것은 우리의

Figure 3. Energy diagrams of Au/pentacene/Au for different situation. (a) Energy diagram before Fermi levels align. (b) Energy diagram assuming that a dipole layer is formed at the two interfaces [17]. (c) Energy diagram in the case the work function of the bottom Au electrode is reduced by surface roughening. Fermi levels are not aligned. (d) Same as (c) but Fermi levels are aligned. Pentacene HOMO and LUMO bend down at the bottom interface. The HOMO and LUMO bending sketched at the interfaces is approximate.

금/펜터신/금 시료의 양쪽 경계에 쌍극자 면이 대칭으로 형성되었음을 시사한다.

그러나 바닥 금 전극을 가열한 뒤에 관찰된 전류의 감소

한국진공약회지 **20**[2], 2011 95

와 정류 현상은 위쪽 금 전극/펜터신과 펜터신/바닥 금 전 극에 차이가 생겼음을 의미한다. 위와 아래 전극의 대칭이 깨진 이유로 바닥 금 전극의 거칠기 증가에 의한 전위장벽 이 변했을 가능성을 들 수 있다. 일함수는 단결정의 표면 방향에 따라 다르며 표면의 거칠기에도 영향을 받는다. 구 리의 경우 거칠기가 30 nm 증가하면 일함수가 약 0.3 eV 감소한다고 보고되었다 [18]. 우리 실험의 경우 가열로 거 칠어진 금 표면의 일함수가 감소했다면 Fig. 3(c)에 그렸듯 이 바닥 전극 금의 페르미 준위가 Fig. 3(b)에 보인 가열하 기 전 위치보다 위로 올라간다. 이 상태에서 펜터신과 바닥 전극 금의 페르미 준위가 정렬하면 Fig. 3(d)와 같이 바닥 쪽 경계에서는 펜터신의 HOMO와 LUMO가 아래쪽으로 휘 므로 펜터신 위 전극과 바닥 전극 경계의 대칭이 깨진다. 만일 바닥 전극 경계에서 HOMO와 LUMO가 아래쪽으로 휜 정도가 위 전극 경계에서 HOMO와 LUMO가 위쪽으로 휜 정도보다 크면 바닥 전극에 음전압을 걸었을 때가 순방 향이 된다. HOMO와 LUMO가 많이 휠수록 경계면에서 전 위장벽이 높아지는데. 가열된 다음에 전류가 줄어드는 현 상은 이 때문으로 생각된다.

가열에 의한 거칠기 증가 때문에 펜터신/바닥 금 전극경계면의 전위장벽이 어떻게 변했는지 조사하기 위해 240 K에서 330 K까지 10 K 간격으로 온도를 올리면서 전류—전압을 측정한 결과를 수식 (1)의 금속/반도체 경계의 쇼트키 방출 모델과 [19] 비교했다.

$$J \propto T^2 \exp \left[ \frac{q}{kT} \left( a\sqrt{V} - \phi_B \right) \right] , \quad a \equiv \sqrt{\frac{q}{4\pi\varepsilon d}}$$

(1)

이 식에서 J는 전류밀도, T는 절대온도, k는 볼츠만 상수, q는 기본 전하량,  $\phi_{\mathcal{B}}$ 는 전위장벽의 높이, V는 외부에서 걸어준 인가전압, d는 펜터신 박막의 두께,  $\varepsilon$ 는 펜터신의 유전율이다. 펜터신의 유전율은 3으로 가정했다 [20]. 전위장벽을 구하기 위해 쇼트키 방출 수식을  $\frac{1}{T^2} = \frac{q}{kT}$   $(a\sqrt{V}-\phi_{\mathcal{B}})$ 로 바꾸어 V에 따라 그린  $\frac{1}{T^2}$  대  $\frac{1}{T}$  그래프에서  $\phi_{\mathcal{B}}$ 를 정했다. 그리고, 가열하지 않은 금 전극의 경우에는  $\phi_{\mathcal{B}}$ 를 양의 인가전압의 함수로, 정류 현상을 보이는 가열한금 전극의 경우에는  $\phi_{\mathcal{B}}$ 를 음의 인가전압의 함수로 그리고, 외삽으로 전위장벽을 구했다. 결과에 의하면, 장벽 높이는 펜터신/가열하지 않은 바닥 금 전극의 경우에는  $0.38~\mathrm{eV}$ , 펜터신/ $400^{\circ}$ C로 30분 가열한 바닥 금 전극의 경우에는

0.54 eV이었다. 금속/반도체 쇼트키 방출 모델로 장벽을 구하려면 샌드위치 구조의 우리 시료에서 위 쪽 금 전극/펜터신 경계에는 완전한 오믹 전극으로 장벽이 없어야 하지만 사실은 그렇지 않다. 또한 위의 쇼트키 방출 모델에서는 펜터신/금 전극의 경계에 생기는 전기 쌍극자에 의한 장벽은 고려하지 않았다. 그러므로 앞에서 구한 장벽의 높이에는 상당한 오차가 있으리라 예상하지만, 이 분석은 적어도표면이 거친 전극에 증착시킨 펜터신 소자에서 나타난 전류 감소와 정류 현상은 거칠어진 금 표면의 일함수 증가에의한 장벽의 변화 때문일 가능성을 정성적으로 보여준다.

전국이 거칠수록 전류가 감소하는 또 다른 이유로 전극 표면이 거칠수록 그 위에 성장시킨 펜터신 박막의 품질이 저하할 가능성이다. Fig. 4(a)와 (b)는 가열 전후의 바닥금 전극에 증착된 펜터신의 초기 모습을 찍은 AFM 영상이고 (c)와 (d)는 50 nm까지 두꺼워진 펜터신을 찍은 AFM

Figure 4. AFM image of the early stage of pentacene deposition (a) on the as-deposited Au electrode and (b) on the Au electrode annealed at 400°C to roughen the surface. There are more pentacene nucleation seeds on the roughened surface. AFM image of 50 nm thick pentacene grown on (c) the as-deposited Au electrode and (d) the Au electrode annealed at 400°C to roughen the surface. Although the roughnesses of the two Au electrode surface are different, morphologies of the two surfaces do not show much difference at this thickness.

영상이다. 50 nm 두께의 펜터신 표면 모양은 전극의 거칠기에 따른 차이를 거의 보여주지 않지만, 초기의 AFM 영상은 펜터신을 같은 시간 동안 증착했을 때 거친 전극 표면에 펜터신 증착핵이 더 많음을 보여준다. 금속 표면에서는 첫 번째 증착 층의 펜터신 분자는 누워서 붙으며 [21], 증착초기에는 수직 방향의 금속 면에 잘 붙지 않으므로 [22] 금속 기판의 거칠기는 증착된 펜터신의 그레인 구조에 영향을 줄 수 있다. 증착핵이 많으면 펜터신/전극 경계면에서그레인의 크기가 작아지고 그레인 사이의 경계면이 많아지므로 전기 전도에 불리하다 [23]. 전극 표면의 거친 정도와그레인의 구조에 따른 트랩 스테이트를 조사를 위해 열자극 전류(thermally stimulated current) 측정이 필요하다 [24].

#### IV. 결 론

금 전극/펜터신/금 전극 시료를 이용하여 바닥 금 전극 표면의 거칠기에 따라 전류 특성이 어떻게 변하는지 조사 했다. 금 전극을 가열하여 표면을 거칠게 만든 다음에 펜터 신을 열증착해서 만든 시료는 표면이 상대적으로 편평한 시료에 비해 전류가 감소했으며 약한 정류 현상을 보였다. 온도를 바꾸면서 측정한 전류-전압 곡선으로부터 쇼트키 방출 모델을 적용하여 구한 펜터신/바닥 금 전극 경계의 전 위장벽은 전극 표면이 거친 쪽이 약 0.144 eV 높았다. 이로 부터 전류 감소와 정류 현상은 표면 거칠기의 증가 때문에 바닥 금 전극의 일함수가 감소하고, 따라서 펜터신/바닥 금 전극 경계에서 펜터신의 HOMO와 LUMO가 아래쪽으로 휘 어졌기 때문이라는 결론을 내릴 수 있었다. 거친 전극에서 전류가 감소한 또 다른 이유로 거친 전극 표면에 자란 펜터 신은 그레인의 크기가 작고 결과적으로 그레인 사이의 경 계면이 많아서 전기전도 특성이 떨어진다는 점을 들 수 있 다. 이 연구의 결과는 유기물 박막을 전류 채널로 이용하는 전자 소자에서 유기물 박막의 품질 뿐 아니라 표면 거칠기 를 비롯한 전극의 품질에도 유의해야 함을 보여준다.

#### 감사의 글

실험과 데이터 분석에 김윤복 군이 많은 도움을 주었음

에 감사한다. 이 연구는 한국과학재단의 지원으로 수행되었음(과제 번호 No. 20090073307).

## 참고문헌

- [1] Y. Y. Lin, D. J. Gundlach, S. F. Nelson, and T. N. Jackson, IEEE Electron Device Lett. 18, 12 (1997).

- [2] Y. H. Tak, K. B. Kim, H. G. Park, K. H. Lee, and J. R. Lee, Thin Solid Films 411, 12 (2002).

- [3] D. Wohrle and D. Meissner, Adv. Mater. **3**, 3 (1991).

- [4] Y. J. Kim, J. H. Baek, S. I. Kang, and J. S. Choi, J. Korean Vacuum Soc. 13, 3 (2004).

- [5] L. Briseno, R. J. Tseng, and M. M. Ling, L. Adv. Mater. 18, 2320 (2006).

- [6] D. S. Kim, Y. S. Lee, J. H. Park, J. S. Choi, and D. Y. Kang, J. Korean Vacuum Soc. 9, 4 (2004).

- [7] H. Klauk, D. J. Gundlach, J. A. Nichols, and T. N. Jackson, IEEE Electron Device Lett. 46, 6 (1999).

- [8] S. C. Lim, S. H. Kim, J. H. Lee, M. K. Kim, D. J. Kim, and T. Zyung, Synthetic Metals 148, 75 (2005).

- [9] J. C. Scott, J. Vac. Sci. Technol. 3, A21, (2003).

- [10] C. H. Jonda, A. B. R. Mayer, U. Stolz, A. Elschner, and A. Karbach, J. Mater. Sci. 35, 5645 (2000).

- [11] I. M. Hutching, *Tribology* (Edward Arnold, London, 1992), pp.323-352

- [12] Y. Kim and D. Jeon, J. Appl. Phys. 108, 016101 (2010).

- [13] J. H. Cho, D. H. Kim, Y. Jang, W. H. Lee, K. Ihm, J. H. Han, S. Chung, and K. Cho, Appl. Phys. Lett. 89, 132101 (2006).

- [14] A. C. Durr, F. Schreiber, M. Kelsch, H. D. Carstanjen, and H. Dosch, Adv. Mater. 14, 13 (2002).

- [15] C. H. Kim and D. Jeon, Appl. Phys. Lett. 95, 153302 (2009).

한국진공약회자 **20**(2), 2011 **97**

- [16] Y. -J. Lin, F. -M. Yang, C. -Y. Huang, W. -Y. Chou, J. Chang, and Y. -C. Lien, Appl. Phys. Lett. 91, 092127 (2007).

- [17] P. G. Schroeder, C. B. France, J. B. Park, and B. A. Parkinson, J. Appl. Phys. 91, 3010 (2002).

- [18] W. Li and D. Y. Li, J. Chem. Phys. **122**, 064708 (2005).

- [19] S. M. Sze, Physics of Semiconductor Devices (John Wiley and Sons, New Jersey, 1981), pp.155-221

- [20] S. D. Ha, Y. Qi, and A. Kahn, Chem. Phys. Lett.

- 495, 212 (2010).

- [21] R. Schlaf, P. G. Schroeder, M. W. Nelson, B. A. Parkinson, P. A. Lee, K. W. Nebesny, and N. R. Armstrong, J. Appl. Phys. 86, 1499 (1999).

- [22] C. Kim and D. Jeon, J. Korean Phys. Soc. 53, 1464 (2008).

- [23] J. Cornil, J. Calbert, and J. L. Breadas, J. Am. Chem. Soc. 123, 1250 (2001).

- [24] W. Kim and D. Jeon, to be published.

# Effect of the Surface Roughness of Electrode on the Charge Injection at the Pentacene/Electrode Interface

Wooyoung Kim and D. Jeon\*

Department of Physics Education, Seoul National University, Seoul 151-748

(Received September 29, 2010, Revised February 14, 2011, Accepted February 18, 2011)

We investigated how the surface roughness of electrode affects the charge injection at the pentacene/Au interface. After depositing Au film on the Si substrate by sputtering, we annealed the sample to control the Au surface roughness. Pentacene and Au top electrode were subsequently deposited to complete the sample. The nucleation density of pentacene was slightly higher on the rougher Au electrode, but surface morphologies of thick pentacene films were similar on both the as-prepared and the roughened Au electrodes. The current-voltage curves obtained from the Au/pentacene/Au structure measured as a function of temperature indicated that the interface barrier was higher for the rougher Au bottom-electrode. We propose that the higher barrier was caused by the lower work function of rougher electrode surface and the higher trap density at the interface.

Keywords: Pentacene, Interface barrier height, Surface roughness, Charge injection

\* [E-mail] jeon@snu.ac.kr

한국진공약회지 **20**[2], 2011 99