# 마이크로미터 크기의 유기 전계 효과 트랜지스터 제작

박성찬<sup>a</sup>·허정환<sup>b</sup>·김규태<sup>b</sup>·하정숙<sup>a</sup>\*

<sup>a</sup>고려대학교 화공생명공학과, 서울 136-713 <sup>b</sup>고려대학교 전기공학과, 서울 136-713

(2010년 10월 11일 받음, 2010년 11월 26일 수정, 2010년 11월 28일 확정)

본 연구에서는 기존 실리콘 반도체 기술 기반의 포토 및 이빔 리소그래피 공정을 통하여 유기 반도체 소자를 패터닝하였다. P3HT나 PEDOT 등의 유기 반도체는 용매에 녹기 때문에 MIMIC (micro-molding in capillaries)이나 inkjet printing 기술을 이용하여 마이크로미터 크기의 소자 제작이 가능하였으나, 펜타신은 용매에 녹지 않기 때문에 매우 복잡한 방법으로 마이크로미터 크기의 소자를 제작하여왔다. 그러나, 본 연구에서는 원자층 증착 방법으로 증착한 산화 알루미늄막을 펜타신의 보호층으로 이용하여 기존의 포토 및 이빔 리소그래피 방법으로 마이크로미터크기의 펜타신 소자를 제작하였으며 그 전기 특성을 확인하였다.

주제어: 펜타신, 유기전계효과트랜지스터, 리소그래피, 원자층 증착 방법, 산화 알루미늄막

## I. 서 론

유기 전계 효과 트랜지스터(organic field-effect transistors, OFETs)는 대면적의 휘어짐이 가능한 소자를 저가 로 제작할 수 있으며, radio frequency identification tag, smart card, bendable display [1-3] 등과 같이 다양한 분 야에 응용이 가능하여 여러 그룹에서 활발한 연구가 진행되 고 있다. 여러 유기 반도체 중에서도 펜타신(pentacene)은 전기적 특성이 매우 우수하기 때문에 [2] 더욱 활발한 연구 가 이루어져 왔다. 그러나 펜타신을 이용한 전계 효과 소자 의 경우 대부분 쉐도우 마스크를 통해 만들어지는 전극 채 널 간의 간격이나 폭이 수십~수천 마이크로미터 정도로 매 우 크기 때문에 작은 영역에 소자를 집적하기에는 어려움이 있다. 또한, P3HT같은 유기 반도체는 용매에 잘 녹아서 소 프트 리소그래피 공정 [4,5]을 통해 수백나노미터에서 수 마이크로미터 정도의 전극 간격과 폭을 갖는 소자의 제작이 가능하지만 펜타신은 용매에 잘 녹지 않기 때문에 소프트 리소그래피 공정을 이용하기 어렵다. 최근 들어 유기 용매 에 녹는 펜타신을 이용한 연구 [6-8]가 진행되고 있지만 기 존의 열 증착 방식에 의해 제작된 펜타신 소자에 비해 아직 까지는 전기적 특성이 좋지 않은 편이다.

전극의 채널 길이를 줄이기 위해 미리 전극 간격을 수십 나노미터의 크기로 만든 후 소자를 제작 [9]하기도 하는데 일반적으로 bottom-contact 소자는 top-contact 소자에 비해 전기적 소자 특성이 떨어진다 [10]. 물론, bottom-contact의 소자의 경우에도 유기 반도체를 적절히 패터닝하게 되면 전기적 특성을 향상시킬 수 있다 [11]. 한편, 유기 전계 효과 소자의 전기적 특성은 게이트 절연막에 의해큰 영향을 받는다. 특히, 알루미늄 산화막은 유기 전계 효과 소자에서 게이트 절연막으로 사용되어 왔으나 [12,13], 최근 들어 이를 유기 반도체의 보호막으로 사용하여 주위환경에 영향을 많이 받는 유기 반도체 소자의 수명을 길게유지할 수 있다는 연구 결과가 보고되었다 [14]. 본 연구에서는 산화 알루미늄막을 저온에서 원자층 중착 방법을 이용하여 유기 반도체 위에 보호막으로 중착한 후 기존의 포토 혹은 이빔 리소그래피 공정을 이용하여 펜타신을 패터 닝하거나 전극의 접촉 위치를 조절하여 소자의 전기적 특성을 조사하였다.

### Ⅱ. 실험방법·결과 및 고찰

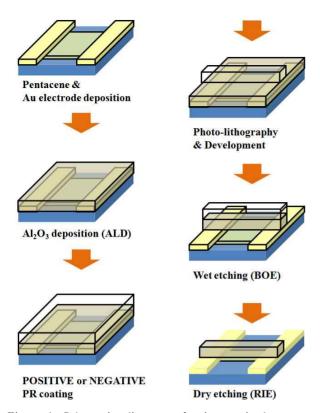

전체 실험과정을 Fig. 1에 도식화하여 나타내었다. P 타입의 실리콘 위에 성장된 300 nm 두께의 실리콘 옥사이드 막을 기판으로 이용하였다. 기판은 아세톤/메탄올/초순수 순으로 각각 5분 씩 초음파세척을 하였다. 세척한 기판에

<sup>\* [</sup>전자우편] jeongsha@korea.ac.kr

Figure 1. Schematic diagram of micron-sized pentacene FET fabrication procedure using conventional photolithography.

4×8 mm² 크기의 쉐도우 마스크를 부착한 후 펜타신을 증 착하였다. 펜타신은 Aldrich사 제품을 구입하였으며 후처리 는 하지 않았다. 펜타신 증착은 자체 제작한 유기용 열 증착 기를 이용하였다.  $2\times10^{-7}$  Torr 이하의 진공상태에서 기판 의 온도를 60°C로 유지하면서 0.1~0.2 Å/s의 속도로 두께 가 100 nm가 되도록 공정을 진행하였다. 펜타신 증착 후 이 빔 증착기를 이용하여 채널 길이가 50 μm가 되도록 쉐도우 마스크를 통과시켜 니켈과 금을 각각 10 nm와 100 nm 두께 가 되도록 증착하였다. 펜타신을 패터닝하기 위한 포토 리 소그래피 공정을 위해서는 용액 상태의 포토레지스트를 이 용해야 하는데 직접 펜타신 위에 포토레지스트를 코팅할 경 우 증착한 펜타신 유기반도체 층이 손상되므로 이를 위한 보 호막이 필요하다. 펜타신을 용액 코팅 공정에서 보호하기 위한 보호막으로 알루미늄 산화막(Al<sub>2</sub>O<sub>3</sub>)를 선택하였다. 알 루미늄 산화막 증착을 위해서 자체 제작한 원자층 증착기 (atomic layer depostion, ALD)를 이용하였다. 알루미늄 산화막 성장 시 펜타신이 증착된 기판의 온도는 펜타신이 손 상되지 않도록 100℃에서 진행하였으며, Al<sub>2</sub>O<sub>3</sub> 성장을 위한 알루미늄 전구체는 트리메틸알루미늄(trimetyhlaluminum,

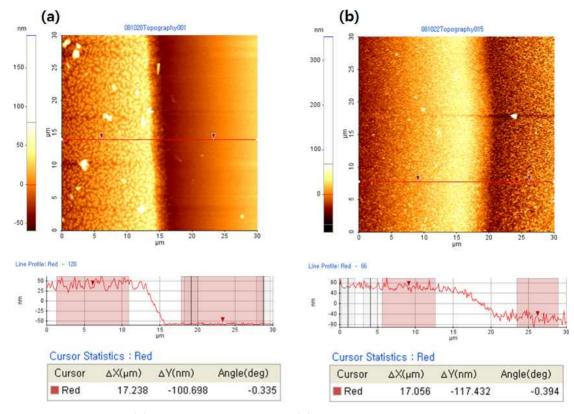

TMA, Al (CH<sub>3</sub>)<sub>3</sub>, Mechatronics, 99.99 %)를 산소 전구체 로는 초순수수(H₂O. Millipore Milli-Q. 18.2 MΩ)을 사용 하였다. ALD 공정에서 처음 초순수수를 0.5초, 질소노출 5 초 후 15초간 펌핑 상태를 유지하고 트리메틸알루미늄과 질 소를 섞어서 0.5초, 질소노출 5초 후 15초간 펌핑을 하였다. 이를 ALD 공정의 한 주기로 설정하였다. 초순수와 TMA/질 소 혼합의 증기압은 각각 200 및 300 mTorr로 유지하였다. 이와 같은 공정 주기 당 알루미늄 산화막은 약 0.9 Å의 두 께로 증착되며 이번 실험에서는 총 100 주기의 공정을 통해 약 17 nm의 알루미늄 산화막을 얻을 수 있었다. 이는 Fig. 2 의 AFM 이미지를 통하여 확인이 가능하다. Fig. 2(a)는 펜 타신 증착 후의 AFM 단차 이미지로 펜타신의 두께가 약 100 nm인 것을 보여준다. Fig. 2(b)는 모든 공정이 끝난 후의 AFM 단차 이미지로 약 117 nm의 두께를 갖는 것을 알 수 있 다. 이를 통해 증착된 알루미늄 산화막의 두께가 약 17 nm인 것이 확인 가능하다. 포토 리소그래피에 사용된 포토레지스 트로는 포지티브형은 AZ5214(Clariant)를 네거티브형은 SU8(Microchem)을 이용하였다. 포토레지스트 유형에 맞 는 포토마스크를 이용하여 356 nm 파장의 자외선을 10초간 노광한 후 현상하였다. 포토 리소그래피 공정 후 불필요한 펜타신을 제거하기 위하여 먼저 알루미늄 산화막을 제거하 여야 하는데 이를 위해 buffered oxide etchant (BOE 6:1, J. T. Baker)를 사용하였다. ALD 공정으로 증착 된 Al<sub>2</sub>O<sub>3</sub>막 이 매우 얇기 때문에 습식 식각 공정에서 온도와 시간이 매 우 중요한데 이를 위해 BOE의 온도를 25°C가 되도록 유지 하면서 2초간 식각하여 포토레지스트가 남아있는 부분은 제 외한 나머지 부분의 알루미늄 산화막을 제거하였다. 용매를 이용한 식각 후 펜타신을 제거하기 위하여 건식 식각 공정을 하였다. 건식 식각 공정은 반응성 이온 식각 공정(reactive ion etching, RIE)을 통해 진행하였으며 산소 가스를 이용 하였다. 산소를 50 sccm을 흘려주면서 식각기 내부의 압력 을 50 mTorr로 유지하여 라디오 주파수의 전력을 90 W로 가하여 90초간 식각하여 남아있는 포토레지스트와 주위의 펜타신 층을 제거하였다.

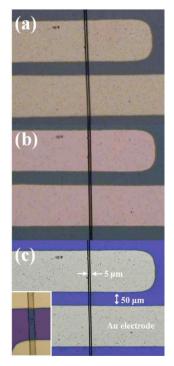

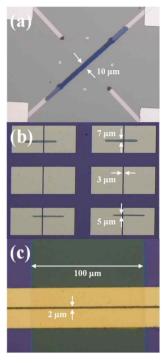

Fig. 3(a)는 5 μm의 채널 폭을 갖도록 포토 리소그래피 공정을 진행한 후 소자의 모습을 광학 현미경으로 관찰한 것이다. 이 때 채널 길이는 50 μm가 되도록 전극을 증착하였다. 이후 습식 공정 후(Fig. 3b), 건식 공정 후(Fig. 3c)의 모습도 광학 현미경으로 촬영하였다. 공정 과정을 통해 채널 폭은 5 μm로 잘 유지되고 있음을 확인할 수 있다. Fig. 3의

Figure 2. AFM images of after (a) pentacene deposition and (b) end of fabrication processes.

Figure 3. Optical microscope images of after (a) photolithography, (b) wet etching, and (c) dry etching process.

공정은 포지티브형 포토레지스트인 AZ5214를 이용한 것이다. Fig. 3(c)의 삽입도는 네거티브형의 포토레지스트인 SU8을 사용하여 채널 길이가  $100~\mu m$ , 채널 폭이  $10~\mu m$ 로 모든 공정을 진행 한 후의 광학현미경 그림이다. 이를 통해 포지티브형 혹은 네거티브형의 포토레지스트 둘 중 어느 것을 이용하여도 공정을 진행할 수 있음을 알 수 있었다. 본 연구를 통해 두 가지 포토레지스트를 이용하여 채널 폭이 2,5 그리고  $10~\mu m$ 의 펜타신 소자를 만들 수 있었다.

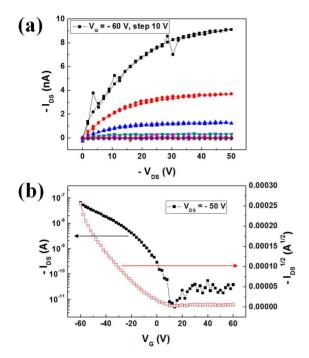

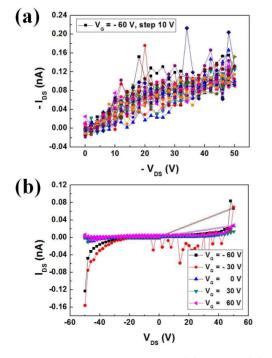

알루미늄 산화막을 펜타신 보호막으로 이용하여 기존의 포토 리소그래피 방법으로 제작된 펜타신 소자를 Agilent사의 4140B semiconductor paramter analyzer를 이용하여 전기 특성을 측정하였다. Fig. 4(a)는 Fig. 3(c)의 소자를 게이트 전압을 -60 V에서 60 V까지 10 V씩 증가시키면서 드레인-소스 전압을 0에서 -50 V까지 변화시키면서 측정한후 이를 도식화한 것이다. 이는 전형적인 포지티브형의 반도체 소자의  $I_{DS}$ - $V_{DS}$  전기적 거동을 보여주는 결과이다. Fig. 4(b)는 드레인-소스 전압을 -50 V로 고정한 수게이트 전압을 -60에서 60 V까지 증가시키면서 측정한 펜타신 소자의 전기 전이 곡선이다. 분석을 통해 채널 길이가 50  $\mu$ m 이고 채널 폭이 5  $\mu$ m인 마이크로 크기의 펜타신 소자에서

Figure 4. (a)  $I_{DS}-V_{DS}$  characteristics and (b) transfer curve of pentacene FET with 5  $\mu m$  channel width and 50  $\mu m$  channel length in figure 3(c).

홀의 이동도는 0.58 cm²/V·s, 문턱전압은 -45 V이고 전류의 on/off 비가 10<sup>4</sup>인 것을 확인하였다. 이는 알루미늄 산화막을 도입하여 포토 리소그래피 공정을 진행하여도 펜타신의 전기적 물성이 크게 영향을 받지 않음을 확인할 수 있는결과로, 포토 리소그래피 공정의 정밀화를 통하여 더욱 작은 크기의 펜타신 소자의 제작이 가능하다는 것을 보여준다.

포토 리소그래피를 이용한 공정은 이빔 리소그래피를 이용한 공정으로의 확장이 가능하다. 우선 비교적 쉬운 공정을 위하여 유기 반도체와 기판 사이에 전극을 접촉시키는 공정(bottom-contact)을 진행하였다. 이를 위해 포토 리소그래피 공정을 통해 원하는 크기의 전극 모양을 만들고 이빔 증착 공정을 이용하여 티타늄 10 nm와 금 100 nm의 전극을 만들었다. 이후 공정은 펜타신 증착, 알루미늄 산화막 증착, 이빔 리소그래피, 습식 및 건식 식각의 과정을 Fig. 1 및 3의설명과 동일하게 진행하였다. 포토 리소그래피를 이용할 경우 대면적 노광이 가능하기 때문에 포지티브형 및 네거티브형의 레지스트 이용 시 적절한 마스크를 이용하면 레지스트에 크게 영향을 받지 않는 것이 특징이나 이빔 리소그래피의 경우 원하는 부분만 펜타신을 남기기 위한 공정을 진행하기 위해서는 포지티브형의 레지스트 보다 네거티브형 레지스

Figure 5. Optical microscope images of (a), (b) bottom contact, and (c) top contact patterned pentacene FET using e-beam lithography technique.

트를 이용하여 이범의 노광 시간을 줄이는 것이 공정상 매우 유리하다. 따라서 본 연구에서는 이빔 리소그래피용 레지스 트로 아자이드 작용기(azide, R-N<sup>-</sup>=N<sup>+</sup>=N<sup>-</sup>)가 불규칙하게 달린 폴리스티렌(polystyrene)을 합성하여 사용하였다. 아 자이드 작용기는 자외선이나 이빔 등의 강한 에너지의 전달 을 통해 교차결합(crosslinking)이 일어나 네거티브형 레지 스트를 제작 [15,16]하는데 많이 이용된다. 합성된 폴리스티 렌-아자이드 고분자는 분자량이 21 kg/mol, 분산도는 1.15 이며 아자이드 작용기의 비율은 약 10 %이다. 합성된 폴리 스티렌-아자이드를 7 wt.% 농도로 톨루엔 용액으로 만든 후 알루미늄 산화막 위에 회전 코팅 공정으로 도포하여 준 다. 도포된 폴리스티렌-아자이드막은 110°C에서 약 15분간 열처리해 준다. 폴리스티렌-아자이드 레지스트는 원하는 곳에 원하는 크기로 이빔을 조사한 후 톨루엔 용액을 이용하 여 간단하게 현상할 수 있는 장점이 있다. 이후 습식 및 건식 식각 공정을 통하여 원하는 크기의 펜타신 소자의 제작이 가 능하다. Fig. 5(a)는 이빔 리소그래피 공정을 이용하여 만든 채널 길이가 125 um이며 채널 폭이 10 um인 펜타신 소자의 광학현미경 그림으로 비교적 길이가 길고 폭을 넓은 소자 제 작이 가능함을 보여주는 결과이다. Fig. 5(b)는 전극을 규칙

적으로 배치하고 채널 폭을 3 µm로 만든 후 전체 면적에 펜 타신을 증착한 후 Fig. 5(a)와 동일한 공정을 진행한 것이 다. 이 때 이빔 리소그래피 공정에서 규칙적인 반복 노광 공 정을 통하여 마이크로 크기의 펜타신 소자의 집적 제작이 가 능하다. Fig. 5(b)에서는 채널 폭이 7과 5 um가 되도록 이빔 리소그래피 프로그램을 설정 한 후 공정을 진행한 것으로 원 하는 위치에 원하는 크기의 펜타신 소자의 제작이 가능함을 보여준다. Fig. 5(a)와 (b)의 유기 반도체 전계 효과 트랜지 스터는 Fig. 3의 소자에 비해 전기적 특성이 좋지 않았는데 (Fig. 6(a)) 이는 미리 제작된 전극과 그 위에 올라간 유기 반 도체간의 접촉이 좋지 않은 탓으로 판단된다. 이를 개선하 기 위해서는 금 전극 위에 메틸기를 갖는 티올(CH3-··· -SH)의 단분자층 자기 조립박막을 형성하여 해결 가능할 것으로 생각된다. 또는 hexamethyldisilazane(HMDS)를 펜타신 증착 전에 실리콘 옥사이드 기판에 처리함으로써 [17-19] 가능할 것으로 생각된다. Fig. 5(c)는 이빔 리소그 래피 공정으로 펜타신 top-contact 소자를 만든 것이다. 본 연구에서는 채널 길이를 2 µm까지 만드는 것이 가능했으나 더욱 정밀한 이빔 리소그래피 공정을 이용하여 채널 길이를 줄이는 것이 가능하다고 판단된다. 그러나 이번 연구에서 제작된 Fig. 5(c)의 소자는 전기 특성을 제대로 측정하기가

Figure 6. Electrical characteristic of (a) figure 5(b) and (b) figure 5(c).

어려웠는데(Fig. 6(b)) 이는 이빔 리소그래피 공정 후 현상하는 과정에서 레지스트의 언더컷(under cut)이 발생하고 또한 습식 식각에서 등방성 식각으로 인해 노출된 펜타신이 최종적으로 전극 증착 후 lift-off 하는 과정에서 아세톤에 노출되며 이 때 아세톤이 펜타신에 영향을 끼쳐 전기 측정이 불가능해진 것으로 확인되었다. 향후 연구를 진행하는 과정에서 개선되어야 할 부분이다.

# Ⅲ. 결 론

우리는 본 연구에서 알루미늄 산화막을 펜타신의 보호층으로 도입하고 기존의 포토 및 이빔 리소그래피 공정을 통하여 마이크로미터 크기의 펜타신 소자를 제작하였다. 포토리소그래피 공정을 이용하여 만들어진 펜타신 소자는 채널길이가 50 μm, 폭을 5 μm로 만들었으며, 전기 특성이 0.58 cm²/V·s의 전기이동도 및 10⁴의 on/off 전류비를 보였다. 이를 통해 공정 중 펜타신의 전기 특성이 잘 유지되며 마이크로미터 크기로 소자제작이 가능함을 확인하였다. 이빔 리소그래피 공정을 이용하여 만들어진 유기 반도체 전계 효과트랜지스터는 bottom—contact 소자의 경우 전극과 반도체간의 접촉 문제로, 그리고 top—contact 소자의 경우 공정상 펜타신이 유기 용매에 노출되는 문제로 인하여 소자의 모양 제작은 가능하였으나 전기적 특성 확인에 문제가 있었으며, 향후 연구를 통해 이를 개선하여야 할 것이다.

# 감사의 글

본 연구는 한국과학재단의 나노원천기술개발사업(2010-0019180), 도약연구지원사업(2010-0018932), 및 핵심연구지원사업(2010-0010374) 연구비에 의하여 수행되었습니다.

### 참고문헌

- [1] R. A. Street, W. S. Wong, S. E. Ready, M. L. Chabinyc, A. C. Arias, S. Limb, A. Salleo, and R. Lujan, Mater. Today 9, 32 (2006).

- [2] C. D. Dimitrakopoulos and P. R. L. Malenfant,

- Adv. Mater. 14, 99 (2002).

- [3] S. R. Forrest, Nature 428, 911 (2004).

- [4] A. Blümel, A. Klug, S. Eder, U. Scherf, E. Moderegger, and E. J. W. List, Org. Electron. 8, 389 (2007).

- [5] D. A. Serban, P. Greco, S. Melinte, A. Vlad, C. A. Dutu, S. Zacchini, M. C. Iapalucci, F. Biscarini, and M. Cavallini, Small 5, 1117 (2009).

- [6] K. S. Kim, Y. H. Kim, J. In. Han, K. N. Choi, S. K. Kwak, D. S. Kim, and K. S. Chung, J. Kor. Vac. Soc. 17, 435 (2008)

- [7] J. -H. Kwon, S. -I. Shin, J. Choi, M. -H. Chung, H. Kang, and B. -K. Ju, Solid State Electron. 53, 266 (2009)

- [8] J. -W. Han, J. -Y. Chun, C. -H. Ok, and D. -S. Seo, Jpn. J. Appl. Phys. 48, 010205 (2009)

- [9] Y. Zhang, J. R. Petta, S. Ambily, Y. Shen, D. C. Ralph, and G. G. Milliaras, Adv. Mater. 15, 1632 (2003)

- [10] C. -C. Kuo and T. N. Jackson, Appl. Phys. Lett. 94, 053304 (2009).

- [11] C. Balocco, L. A. Majewski, and A. M. Song, Org. Electron. 7, 500 (2006).

- [12] X. -H. Zhang, B. Domercq, X. Wang, S. Yoo, T. Kondo, Z. L. Wang, and B. Kippelen, Org. Electron. 8, 718 (2007).

- [13] J. B. Koo, C. H. Ku, S. C. Lim, S. H. Kim, and J. H. Lee, Appl. Phys. Lett. 90, 133503 (2007).

- [14] H. Jeon, K. Shin, C. Yang, C. E. Park, and S. -H. K. Park, Appl. Phys. Lett. 93, 163304 (2008).

- [15] M. Endo, Y. Tani, M. Sasago, and N. Nomur, J. Electrochem. Soc. 136, 2615 (1989).

- [16] J. Yamamoto, S. -I. Uchino, T. Hattori, T. Yoshimura, and F. Murai, Jpn. J. Appl. Phys. 35, 6511 (1996).

- [17] I. Yagi, K. Tsukagoshi, and Y. Aoyagi, Appl. Phys. Lett. 86, 103502 (2005).

- [18] J. W. Kim, Y. M. Lee, and Y. Park, J. Korean Vac. Soc. 17, 394 (2008).

- [19] A. Papadimitratos, A. Amassian, A. S. Killampalli, J. L. Mack, G. G. Milliaras, and J. R. Engstrom, Appl. Phys. A 95, 29 (2009).

# Fabrication of Micron-sized Organic Field Effect Transistors

Sung Chan Parka, Jung Hwan Huhb, Gyu Tae Kimb, and Jeong Sook Haa\*

<sup>a</sup>Department of Chemical and Biological Engineering, Korea University, Seoul 136-713 <sup>b</sup>School of Electrical Engineering, Korea University, Seoul 136-713

(Received October 11, 2010, Revised November 26, 2010, Accepted November 28, 2010)

In this study, we report on the novel lithographic patterning method to fabricate organic thin film field effect transistors (OTFTs) based on photo and e-beam lithography with well-known silicon technology. The method is applied to fabricate pentacene-based organic field effect transistors. Owing to their solubility, sub-micron sized patterning of P3HT and PEDOT has been well established via micromolding in capillaries and inkjet printing techniques. Since the thermally deposited pentacene cannot be dissolved in solvents, other approach was done to fabricate pentacene FETs with a very short channel length (~30 nm), or in-plane orientation of pentacene molecules by using nanometer-scale periodic groove patterns as an alignment layer for high-performance pentacene devices. Here, we introduce Al<sub>2</sub>O<sub>3</sub> film grown via atomic layer deposition method onto pentacene as a passivation layer. Al<sub>2</sub>O<sub>3</sub> passivation layer on OTFTs has some advantages in preventing the penetration of water and oxygen and obtaining the long-term stability of electrical properties. AZ5214 and ma N-2402 were used as a photo and e-beam resist, respectively. A few micrometer sized lithography patterns were transferred by wet and dry etching processes. Finally, we fabricated micron sized pentacene FETs and measured their electrical characteristics.

Keywords: Pentacene, OFET, Lithography, Atomic layer deposition technique, Al<sub>2</sub>O<sub>3</sub> passivation layer

\* [E-mail] jeongsha@korea.ac.kr