### 論 文 15-2-10

## 계통전압 관측기를 이용한 계통연계형 인버터의 예측전류제어

李貴俊\*, 玄東石†

# Predictive Current Control of a Grid-Connected Inverter with Grid Voltage Observer

Kui-Jun Lee, and Dong-Seok Hyun

요 약

분산전원을 계통에 연계하기 위해서는 전류제어가 필수적이며, 최근에 고성능 DSP(Digital Signal Processors)를 기반으로 빠른 동특성을 만족시키는 예측전류제어에 대한 연구가 활발히 진행되고 있다. 하지만 예측전류제어는 디지털 구현 시 발생하는 시지연, 파라미터 및 입력값의 오차, 노이즈에 의한 간섭으로 인해 제어 성능이 감소할 뿐만 아니라 시스템을 불안정하게 하는 단점을 갖고 있다. 따라서 본 논문은 계통연계형 인버터 응용에 있어서 계통전압 관측기를 이용한 예측전류제어를 제안한다. 전압 관측기 이득 선정을 위해, 계통전압에 존재하는 저차 고조파에 의한 영향을 고려하며, 필터 파라미터 오차에 의한 영향을 분석한다. 제안된 방법은 빠른 전류응답특성 뿐만 아니라, 전압센서를 사용하지 않음으로 인해 노이즈에 강인하며 시스템 구현이 간단하고 계통의 저차 고조파에 강인한 전류제어성능을 갖는다. 제안된 방법의 타당성은 시뮬레이션과 실험을 통하여 검증한다.

#### **ABSTRACT**

For a grid-connected inverter in distributed generation systems, the current control is essential, and recently, the predictive current control based on a high performance digital signal processors (DSP) to satisfy a fast dynamic response has been widely investigated. However, the performance of predictive current control is degraded by the time delay due to digital implementation, the parameter and measured value errors and the interference of noise, and also theses make system even unstable. Therefore, this paper proposes the predictive current control using grid voltage observer for grid-connected inverter applications. To determine the relevant voltage observer gain, the low-order harmonics of grid voltage are considered, and the effect of filter parameter errors is analyzed. The proposed method has a fast current response capability, the robustness to noise and simple implementation due to voltage sensorless control and the robust current control performance to low-order grid harmonics. The feasibility of the proposed method is verified by simulation and experimental results.

Key Words: Predictive Current Control, Voltage Observer, Grid-Connected Inverter

#### 1. 서 론

<sup>†</sup>교신저자: 한양대 전기제어생체공학부 교수

E-mail: dshyun@hanyang.ac.kr

정회원, 한양대 대학원 전기공학과 박사과정

접수일자: 2009. 12. 15 1차 심사: 2010. 1. 8 2차 심사: 2010. 2. 25 심사완료: 2010. 3. 2 분산전원을 계통에 연계하기 위해서 일반적으로 3상전압형 인버터가 사용되며, 계통에 공급하는 전력의품질을 향상시키기 위해 고성능 전류제어와 계통 동기화 기법이 필수적이다<sup>[11]</sup>. 전류제어기로는 일반적으로동기좌표계 PI(Proportional Integral) 제어기와 정지좌표계 PR(Proportional Resonant) 제어기가 널리 사용

되고 있지만, 최근에는 고성능 DSP(Digital Signal Processors)를 기반으로 하는 예측제어에 대한 연구도 상당히 진행되어 왔다<sup>[2,3]</sup>. 예측제어는 시스템 모델을 통하여 제어 대상의 향후 변화를 예측하는 것으로써, PI 제어기의 직렬구조를 회피할 수 있어 빠른 동특성 을 만족시키므로 계통연계형 인버터에 적용하였을 경 우 추가적인 고조파 보상기 없이 계통전압의 왜곡에 더욱 강인한 전류제어기 구현이 가능함을 의미한다. 또한 예측제어는 시스템에 포함되어 있는 비선형성을 고려하여 설계할 수 있기 때문에, 동작점에서의 선형 화 과정이 불필요하다는 장점이 있다. 하지만 디지털 구현 시 발생하는 시스템 지연과 모델에 사용되는 파 라미터의 오차 및 입력값의 오차, 노이즈에 의한 간섭 으로 인해 제어 성능이 감소할 뿐만 아니라 심지어 불 안정 상태에 이른다는 단점을 갖는다. 이를 극복하기 위해 PMSM(Permanent Magnet Synchronous Motor) 구동에서는 각각 회전자 위치 오차와 데드타임 및 이 상적이지 않은 스위칭 특성으로 인한 출력전압 왜곡의 영향을 보상하여 정확한 입력값을 사용하고자 하였고 [4], 부하 인덕턴스 변화에 강인한 제어를 구현하기 위 해 목표 전류의 오차를 영이 아닌 이전 두 시점의 전 류 차가 되게 제어하였으며<sup>[5]</sup>, 계통연계형 인버터에서 는 고속의 ADC(Analog to Digital Converter)를 사용 하여 샘플링 주파수를 스위칭 주파수의 4배로 동작시 켰다<sup>[6]</sup>.

하지만 앞선 경우 모두 전압, 전류센서를 사용하여 변수값을 입력받기 때문에, 노이즈에 취약하다는 한계를 갖게 된다. 따라서 병렬 관측기 구조를 적용한 자기동조(self-tuning) 부하모델을 사용하여 부하 파라미터와 역기전력를 추정하여 이를 극복하려 하였고<sup>[7]</sup>, 기존의 예측 직접전력제어(direct power control)를 개선하고자 가상자속(virtual-flux) 개념을 도입하여 전압센서 없는 제어를 구현하고 실시간 파라미터 추정기를 적용하여 노이즈에 강인할 뿐만 아니라 계통의 저차고조파에도 강인한 성능을 보여주었다<sup>[8]</sup>.

따라서 본 논문은 분산전원용 계통연계형 인버터 응용에 적합한 새로운 계통전압 센서를 사용하지 않는 센서리스 예측전류제어를 제안한다. 이를 위해 기존의 예측전류제어<sup>[4]</sup>에 이산 시간 영역에서 새로운 계통전압 관측기를 구성하고, PLL(Phase Locked Loop)을 적용하여 위상각을 검출하게 된다. 제안된 센서리스 예측전류제어는 예측전류제어의 빠른 동특성과 센서리스 운전이 갖는 노이즈에 강인한 성능을 가지며, 전압센서 없이 간단히 구현할 수 있는 장점을 갖는다. 또한

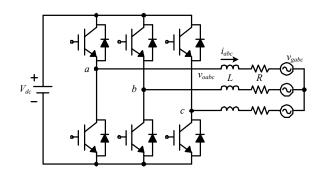

그림 1 3상 계통연계형 인버터

Fig. 1 Three-phase grid-connected inverter

전압 관측기 이득을 선정함에 있어 계통전압의 저차고조파에 대한 영향을 고려하여 전력품질을 향상시킬 수 있었고, 필터 파라미터 오차에 의한 영향을 분석하였다. 마지막으로 제안된 센서리스 예측전류제어의 타당성을 시뮬레이션과 실험을 통하여 검증하였다.

#### 2. 예측전류제어

#### 2.1 예측모델

그림 1은 등가 직렬 저항(R)을 포함하는 필터 인덕 터(L)를 통해 계통에 연계된 3상 계통연계형 인버터를 보여준다. 3상 정지좌표계에서 시스템에 대한 전압 방 정식을 구하면 식 (1)로 표현된다. 여기서  $v_{oabc}$  는 인 버터 출력전압,  $i_{abc}$  는 계통으로 흐르는 인버터 출력전류,  $v_{gabc}$  는 계통전압을 나타내며 각각  $v_{oabc} = \begin{bmatrix} v_{oa} & v_{ob} & v_{oc} \end{bmatrix}^T$ ,  $i_{abc} = \begin{bmatrix} i_a & i_b & i_c \end{bmatrix}^T$ ,  $v_{gabc} = \begin{bmatrix} v_{ga} & v_{gb} & v_{gc} \end{bmatrix}^T$ 로 표현된다.

$$v_{oabc} = R \cdot i_{abc} + L \frac{di_{abc}}{dt} + v_{gabc} \tag{1} \label{eq:voabc}$$

식 (1)을 2상 정지좌표계로 변환하면 식 (2)와 같다.

$$v_{o\alpha\beta} = R \cdot i_{\alpha\beta} + L \frac{di_{\alpha\beta}}{dt} + v_{g\alpha\beta} \eqno(2)$$

식 (2)를 회전변환 $(e^{-j\omega t})$ 를 이용하여 2상 동기좌표계로 변환하면 식 (3)과 같고,  $di_{dq}(t_k)/dt=(i_{dq}(t_{k+1})-i_{dq}(t_k))/T_s$  형태의 미분 근사화를 이용하여이산 형태로 표현하면 식 (4)를 구할 수 있다. 여기서 $\omega$ 는 계통전압의 각속도이며,  $T_s$ 는 샘플링 시간,  $t_k$

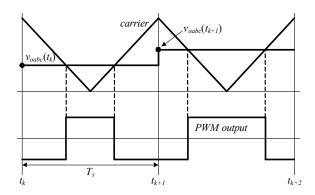

그림 2 예측전류제어의 타이밍도

Fig. 2 Timing sequence of the predictive current control

는 현재 시점,  $t_{k+1}$  은 한 샘플링 앞선 시점을 의미한다.

$$v_{odq} = R \cdot i_{dq} + L \left[ j\omega \cdot i_{dq} + \frac{di_{dq}}{dt} \right] + v_{gdq} \tag{3} \label{eq:3}$$

$$\begin{split} v_{odq}(t_k) &= R \cdot i_{dq}(t_k) + j\omega L \cdot i_{dq}(t_k) \\ &+ L \frac{i_{dq}(t_{k+1}) - i_{dq}(t_k)}{T_s} + v_{gdq}(t_k) \end{split} \tag{4}$$

그림 2와 같이 대칭 PWM(Pulse Width Modulation) 방식을 사용하는 시스템에서는  $t_k$  시점에서 현재의 값들을 샘플링 받고 한 샘플링 이내에 예측전류제어를 수행하여  $t_{k+1}$  시점에서 새롭게 계산된 전압 레퍼런스를 발생시킨다. 이는  $t_{k+2}$  시점에서 전류 지령치에 도달할 수 있음을 의미하며, 이로 인해 2 샘플링 지연이 발생하게 된다. 따라서  $t_{k+2}$  시점에서의 전류 지령치  $(i_{aq}^*(t_{k+2}))$ 를 예측하여,  $i_{aq}(t_{k+2})$  와의 오차가 최소화되는 전압 레퍼런스  $(v_{oabc}(t_{k+1}))$ 를 발생시키면 시지연의 영향을 감소시킬 수 있고, 전류 응답의 동특성을 향상시킬 수 있게 된다. 만약 인버터의 입력전압이 충분히 크다면, 2 샘플링 후에 인버터 전류는 정확히 전류 지령치를 추종하게 된다.

식 (4)로부터 시점을 한 샘플링 앞으로 이동시키면 전압 레퍼런스  $(v_{odq}(t_{k+1}))$  에 대한 식으로 전개할 수 있으며, 식 (5)와 같다. 여기서  $v_{gdq}(t_{k+1})$  는 보간법을 이용하여 예측할 수 있지만 계통전압이 3상 평형이라고 가정한다면 동기좌표계에서 계통전압은 직류값이므로  $v_{gdq}(t_{k+1})$  는 간단히  $v_{gdq}(t_k)$ 로 대체할 수 있으며, 마찬가지로 동기좌표계에서 전류 지령치는 일정한 직

류값이기 때문에,  $i_{dq}^*(t_{k+2})$ 에 대한 예측은 불필요하며 간단히  $i_{dr}^*(t_k)$ 로 대체할 수 있다.

$$\begin{aligned} v_{odq}(t_{k+1}) &= R \cdot i_{dq}(t_{k+1}) + j\omega L \cdot i_{dq}(t_{k+1}) \\ &+ L \frac{i_{dq}^*(t_{k+2}) - i_{dq}(t_{k+1})}{T_*} + v_{gdq}(t_{k+1}) \end{aligned} \tag{5}$$

따라서 파라미터 값을 정확히 안다고 가정한다면 식 (5)를 통해 전압 지령치를 계산할 수 있고, 이를 위해 필요한 값은  $i_{dq}(t_{k+1})$  이 되며, 이는 식 (4)를 재구성한 식 (6)으로부터 구할 수 있다.

$$\begin{split} i_{dq}(t_{k+1}) &= \frac{T_s}{L} \left( v_{odq}(t_k) - v_{gdq}(t_k) - j\omega L \cdot i_{dq}(t_k) \right) \\ &+ \left( 1 - \frac{RT_s}{L} \right) i_{dq}(t_k) \end{split} \tag{6}$$

#### 2.2 전압 제한

부하가변 시, 식 (5)로부터 계산된 전압 지령치가 인 버터 출력용량보다 크다면,  $t_{k+1}$  시점에서 실제 인버터 출력전압과 지령전압의 오차로 인해  $t_{k+2}$  시점의 전류 예측에 오차를 발생시키며 이는 결국  $t_{k+2}$  시점의 전압 지령치를 정확히 계산하지 못하게 되어, 전류 지령치를 빠르게 추종하지 못할 뿐 아니라 시스템을 불안정하게 하는 원인이 된다. 따라서 식 (5)로부터 계산된 전압 지령치가 인버터의 선형 출력영역을 넘어서게 되면 식 (7)과 같이 수정되어야 한다.

$$v_{odq}^{*}(t_{k+1}) = v_{odq}(t_{k+1}) \frac{V_{dc}}{\sqrt{3} \cdot \sqrt{(v_{od}(t_{k+1}))^{2} + (v_{oq}(t_{k+1}))^{2}}}$$

(7)

#### 3. 계통전압 관측기

식 (5)를 통해 예측전류제어가 정상적으로 동작하기 위해서는 정확한 파라미터 값들과 변수 값들을 알고 있어야 한다. 따라서 전압 관측기를 구성하여 계통전압의 센서를 대체하려면 동특성이 우수한 관측기가 설계되어야 하며, 이는 전체적인 시스템의 제어 성능에영향을 미치게 된다. 따라서 본 논문에서는 2상 동기좌표계에서 계통전압을 추정하고, 추정된 계통전압을 무LL을 통하여 위상각을 검출하는 계통전압 관측기를 구성하였다. 식 (4)와 계통전압이 3상 평형이라는 가정을 통해 식 (8)을 구할 수 있다.

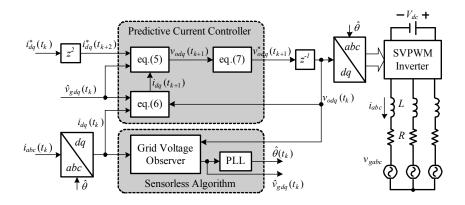

그림 5 전체적인 센서리스 예측전류제어의 블록도

Fig. 5 Block diagram of Overall Sensorless Predictive Current Control

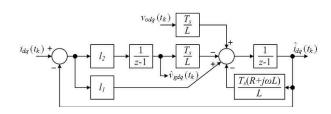

그림 3 이산시간 영역에서의 계통전압 관측기

Fig. 3 Grid voltage observer in discrete-time domain

PI +

$$\hat{\theta}(t_k)$$

$ZT_s$   $\hat{\theta}(t_k)$   $ZT_s$   $\hat{\theta}(t_k)$   $ZT_s$   $\hat{\theta}(t_k)$   $ZT_s$   $ZT$

$$\begin{bmatrix} i_{dq}(t_{k+1}) \\ v_{gdq}(t_{k+1}) \end{bmatrix} = \begin{bmatrix} 1 - \frac{T_s(R + j\omega L)}{L} & -\frac{T_s}{L} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} i_{dq}(t_k) \\ v_{gdq}(t_k) \end{bmatrix} + \begin{bmatrix} \frac{T_s}{L} \\ 0 \end{bmatrix} v_{odq}(t_k)$$

(8)

식 (8)로부터 전압 관측기를 식 (9)과 같이 구성할 수 있고, 극점배치기법을 통해 이득 $(l_1,\ l_2)$ 을 구할 수 있다.

그림 3은 식 (9)로 구성된 계통전압 관측기의 블록도이다. 인버터 출력전압과 전류를 입력으로 받아 계통전압을 추정하고, 그림 4의 PLL을 통해서 위상각을 검출하게 된다. PLL의 대역폭은 계통전압의 불평형 및 왜

$$\begin{bmatrix}

\hat{i}_{dq}(t_{k+1}) \\

\hat{v}_{gdq}(t_{k+1})

\end{bmatrix} = \begin{bmatrix}

1 - \frac{T_s(R + j\omega L)}{L} & -\frac{T_s}{L} \\

0 & 1

\end{bmatrix} \begin{bmatrix}

\hat{i}_{dq}(t_k) \\

\hat{v}_{gdq}(t_k)

\end{bmatrix} + \begin{bmatrix}

\frac{T_s}{L} \\

0

\end{bmatrix} v_{odq}(t_k) + \begin{bmatrix}

l_1 \\

l_2

\end{bmatrix} \begin{pmatrix}

i_{dq}(t_k) - \begin{bmatrix} 1 & 0 \end{bmatrix} \begin{pmatrix}

\hat{i}_{dq}(t_k) \\

\hat{v}_{odq}(t_k)

\end{pmatrix}$$

(9)

곡에 대한 강인한 성능을 보여주는 100 Hz로 선정하였다<sup>[9]</sup>. 관측기의 이득 선정 시, 계통전압에 5차와 7차의 저차 고조파가 존재할 경우, 동기좌표계 상에서는 기본파의 6배에 해당하는 주파수 성분이 되기 때문에, 계통전압의 왜곡 시에도 관측기가 정확하게 추정하기 위해서는 관측기의 대역폭이 그 이상이 되어야 하지만 외란 및 노이즈에 강인하기 위해서는 적절하게 제한되어야 한다.

그림 5는 앞선 계통전압 관측기를 포함하는 전체적인 센서리스 예측전류제어 블록도를 보여준다. 이미 언급했듯이  $i_{dq}^*(t_{k+2})$  는 예측하지 않으며 대신  $i_{dq}^*(t_k)$ 를 사용하였고, 그림 5에는 의미상 2 샘플링 앞선 시점의전류임을 강조하기 위해  $z^2$  변환 블록이 사용되었다.

표 1 시뮬레이션 조건 Table 1 Simulation condition

| 계통 선간전압                   | 110 [Vrms] |

|---------------------------|------------|

| 입력전압( $\mathit{V}_{dc}$ ) | 200 [V]    |

| 필터 인덕턴스( <i>L</i> )       | 3 [mH]     |

| 등가 직렬 저항( <i>R</i> )      | 0.1 [Ω]    |

| 샘플링 주파수                   | 10 [kHz]   |

| 스위칭 주파수                   | 10 [kHz]   |

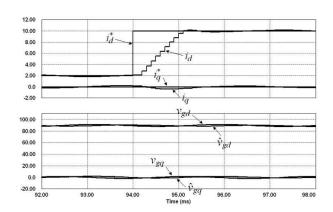

그림 6 전압 관측기의 대역폭이 300 Hz인 경우의 출력파형 Fig. 6 Output waveform at 300 Hz of voltage observer bandwidth

#### 4. 시뮬레이션

제안된 센서리스 예측전류제어의 파라미터 오차 및 관측기 이득에 의한 영향을 살펴보기 위해 시뮬레이션을 수행하였고, 시뮬레이션에 사용된 조건은 표 1과 같다. 계통전압은 실험환경과 유사한 2%의 5고조파 성분과 1%의 7고조파 성분을 포함하는 것으로 가정하였다. 전압 관측기의 이득은 감쇠비가 0.707이며 대역폭이 각각 300 Hz, 600 Hz일 경우에 대해 적용하여 시뮬레이션을 수행하였다.

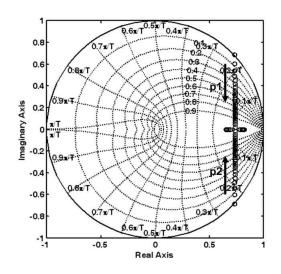

그림 6, 7에서 볼 수 있듯이 전류 지령치의 변화에 따른 예측전류제어의 빠른 동특성을 확인할 수 있고, 관측기의 대역폭이 300 Hz에서 600 Hz로 증가함에 따라 저차 고조파가 포함되어 있는 계통전압의 추정이잘 이루어져 전류의 정상상태 오차 또한 감소함을 확인할 수 있었다. 만약 관측기의 이득을 더욱 증가시키게 되면 노이즈에 민감해지기 때문에, 본 논문에서는 관측기의 대역폭을 600 Hz로 선정하였다. 또한 전압 관측기의 성능을 파라미터 오차에 의한 근궤적 변화를 통해 분석하였다. 그림 8은 인덕턴스 오차가 -80% 에서+80% 까지 0.15mH 씩 증가할 때, 전압 관측기의 근궤적도를 보여준다. 모델에 사용된 인덕턴스가 작을 때에는 감쇠비가 감소하며 시스템이 불안정하게 되지만, 클때에는 시스템이 비교적 안정상태를 유지함을 알 수 있다.

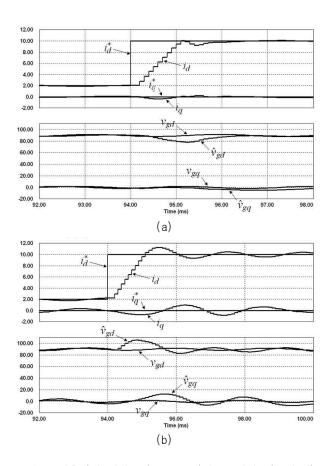

그림 9는 모델에 사용된 인덕턴스의 파라미터 오차가 각각 ±50% 인 경우에 대한 시뮬레이션 파형을 보여준다. 그림 9(a)는 인덕턴스의 오차가 +50%인 경우로 그림 7과 유사한 제어성능을 보여주지만, 그림 9(b)는 인

그림 7 전압 관측기의 대역폭이 600 Hz인 경우의 출력파형 Fig. 7 Output waveform at 600 Hz of voltage observer bandwidth

그림 8 인덕턴스 오차가 -80%에서 +80%까지 증가할 때, 전 압 관측기의 근궤적도

Fig. 8 Pole loci of voltage observer with L varying from -80% to 80%

덕턴스의 오차가 -50%인 경우로 과도상태와 정상상태특성이 모두 악화되는 것을 확인할 수 있다. 따라서 실제 사용된 인덕턴스의 값을 정확히 모를 경우에는 약간높게 추정된 인덕턴스 값을 사용하는 것이 바람직하다.

#### 5. 실험 결과

실험은 1.5 KVA급 프로토타입 계통연계형 인버터로 수행하였고, 제어기는 TMS320VC33 DSP를 이용하여 구현하였다. 9 KVA의 변압기를 통하여 인버터 출력필

그림 9 관측기의 대역폭이 600 Hz이며, 모델에 사용된 인 덕턴스가 오차를 갖는 경우의 출력파형 (a) +50% 오차 (b) -50% 오차

Fig. 9 Output waveform with +50% error in model inductance at 600 Hz of voltage observer bandwidth

터와 계통전압을 연계하였으며, 계통전압에는 약 2%의 5고조파와 약 1%의 7고조파가 포함되어 있음을 확인하였다. 실험에 사용된 다른 조건은 시뮬레이션에 사용된 것과 같다.

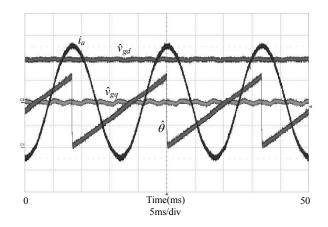

그림 10은 정상상태 파형을 보여준다. 계통전압 $(\hat{v}_{gd}, \hat{v}_{gq})$ 이 잘 추종되며 PLL을 통한 위상각 $(\hat{\theta})$  검출이 잘 수행됨을 알 수 있다. 또한 예측전류제어를 통해 출력 전류가 거의 단위 역류를 만족시킴을 알 수 있다.

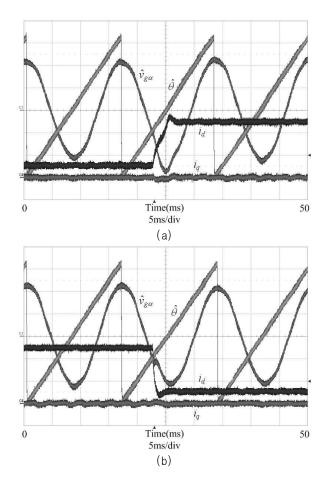

그림 11은 전류 지령치 변화에 따른 추종된 계통전압과 위상각, 인버터 출력전류의 파형을 보여준다. 그림 11(a)는 전류 지령치를 2A에서 10A로 증가시켰을 경우이고, 그림 11(b)는 전류 지령치를 10A에서 2A로 감소시켰을 경우의 파형이다. 전류가 잘 분리 (decoupling)되어 있으며 빠른 동특성을 확인할 수 있다. 전류변화 시 발

그림 10 정상상태 파형( $i_a$ : 4A/div,  $\hat{v}_{gd}$ ,  $\hat{v}_{gq}$ : 50V/div,  $\hat{\theta}$ : 2rad/div)

Fig. 10 Steady state waveform

생하는 계통전압의 변동은 전압관측기의 성능 및 실험에 사용된 변압기의 누설 인덕턴스와 누설 저항의 영향 때문인 것으로 생각되며, 추가적으로 이는 모델파라미터에 사용된 값이 약간 작게 추종된 효과에 의하여제어 성능이 감소한 것으로 생각된다. 또한 2A 부하보다 10A 부하에서 계통전압의 유효성분이 약간 증가하는 것도 같은 이유로 생각되며, 부하증가 시에는 약4ms, 부하감소 시에는 약2ms 이내 정상상태로 들어감을 확인할 수 있었다.

그림 12는 모델 인덕턴스의 파라미터 오차가 각각 ±50% 인 경우에 대한 출력 파형을 보여준다. 그림 12(a)의 +50% 인덕턴스 오차에 대해서는 그림 11(a)와 유사한 동작 특성을 확인할 수 있었고, 그림 12(b)의 -50% 인덕턴스 오차에 대해서는 오버슈트와 정상상태전류 리플이 증가함을 확인할 수 있었다. 이는 앞선 시뮬레이션 결과와 일치하는 동작 특성을 보여준다.

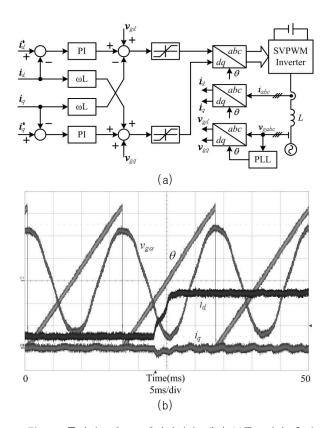

마지막으로 제안된 센서리스 예측전류제어의 성능을 비교하기 위하여 동기좌표계 PI 제어기를 동일한 계통 연계형 인버터에 적용하여 실험을 수행하였다. 그림 13 (a)는 동기좌표계 PI 제어기를 적용한 전제적인 제어 블록도를 보여주며, PI 제어기( $k_p+k_p/s$ )의 이득 값은 대 역폭이 1 kHz 를 갖도록  $k_p=18.84$ ,  $k_r=628.31$  로 선정하였고, 추가적인 분리(decoupling) 제어와 피드포워드 제어를 포함시켰다. 그림 13(b)는 과도응답특성을 보여주며, 그림 11(a)의 제안된 센서리스 예측전류제어의 성능과 유사함을 확인할 수 있다. 따라서 제안된 센서리스 예측전류제어는 별도의 이득 선정 절차 없이 우수한 동특성을 갖는 전류제어기 구현이 가능함을 보여준다.

그림 11 전류 지령치 변화에 따른 출력파형 $(i_d,i_q)$ : 4A/div,  $\hat{v}_{g\alpha}$ : 40V/div,  $\hat{\theta}$ : 1rad/div) (a) 2A 에 서 10A 로 증가 (b) 10A 에서 2A 로 감소

Fig. 11 Output waveform at load variation between 2A and 10A

#### 6. 결 론

본 논문은 계통연계형 인버터에서 기존의 예측전류 제어에 계통전압 관측기를 추가한 센서리스 예측전류 제어를 제안하였다. 인버터 출력전압과 전류로부터 간단하게 계통전압 관측기를 구현하였고, 기존의 PLL을 통하여 위상각을 검출하였다. 전압 관측기를 통하여 전압센서 없는 저가 구현이 가능하며, 관측기에 내장되어 있는 저역통과필터 기능으로 인해 노이즈에 강인한 시스템 구현이 가능하다. 또한 실제 계통전압에 저차 고조파가 존재하는 경우에도 잘 추종할 수 있는 적절한 전압 관측기의 대역폭을 선정하였다. 제안된 방법은 예측전류제어가 갖는 우수한 전류응답특성을 보였으며.

그림 12 모델에 사용된 인덕턴스가 오차를 갖는 경우의 출 력파형 (a) +50% 오차 (b) -50% 오차

Fig. 12 Output waveform with +50% error in model inductance

모델에 사용된 필터 인덕턴스가 실제 값보다 작을 경우에는 제어 성능이 약간 감소하였지만, 실제 값보다 큰 경우에는 제어 성능에 큰 영향을 미치지 않는 것으로 확인되었다. 이는 사용된 파라미터의 정확한 값을 알지 못하는 경우에 약간 큰 모델 파라미터 값을 사용하는 것이 바람직함을 보여준다.

제안된 센서리스 예측전류제어는 DSP 기반의 계통 연계형 인버터 시스템 구현에 적합할 것으로 생각된다.

본 연구는 전력IT사업단을 통해 지식경제부의 전력산업기술개발사업으로부터 지원받아 수행되었습니다.

그림 13 동기좌표계 PI 제어기 (a) 제어 블록도 (b) 출력 파형

Fig. 13 Synchronous reference frame PI controller (a) control block diagram (b) output waveform

#### 참 고 문 헌

- [1] F. Blaabjerg, R. Teodorescu, M. Liserre, and A. V. Timbus, "Overview of control and grid synchronization for distributed power generation systems", *IEEE Trans. Ind. Electron.*, Vol. 53, No. 5, pp. 1398 1409, Oct. 2006.

- [2] P. Cortés, M. P. Kazmierkowski, R. M. Kennel, D. E. Quevedo, and J. Rodríguez, "Predictive control in power electronics and drives", *IEEE Trans. Ind. Electron.*, Vol. 55, No. 12, pp. 4312 4324, Dec. 2008.

- [3] 이진우, "제어 시지연이 있는 고성능 PI 전류제어기에 대한 예측전류의 적용방법", 전력전자학회논문지, 제11권, 제5호, pp. 426-430, 2006.

- [4] H.-T. Moon, H.-S. Kim, and M.-J. Youn, "A discrete-time predictive current control for PMSM", IEEE Trans. Power Electron., Vol. 18, No. 1, pp. 464 - 472, Jan. 2003.

- [5] G. Bode, P. C. Loh, M. J. Newman, and D. G. Holmes,

- "An improved robust predictive current regulation algorithm", *IEEE Trans. Ind. Appl.*, Vol. 41, No. 6, pp. 1720 1733, Nov./Dec. 2005.

- [6] Q. Zeng and L. Chang, "An advanced SVPWM-based predictive current controller for three-phase inverters in distributed generation systems", *IEEE Trans. Ind. Electron.*, Vol. 55, No. 3, pp. 1235 - 1246, Mar. 2008.

- [7] Y. A. R. I. Mohamed and E. F. El-Saadany, "An improved deadbeat current control scheme with a novel adaptive self-tuning load model for a three-phase PWM voltage-source inverter", IEEE Trans. Ind. Electron., Vol. 54, No. 2, pp. 747 759, Apr. 2007.

- [8] P. Antoniewicz and M. P. Kazmierkowski, "Virtual-flux-based predictive direct power control of ac/dc converters with online inductance estimation", IEEE Trans. Ind. Electron., Vol. 55, No. 12, pp. 4381 - 4390, Dec. 2008.

- [9] S.-K. Chung, "A phase tracking system for three phase utility interface inverters", *IEEE Trans. Power Electron.*, Vol. 15, No. 3, pp. 431 - 438, May 2000.

#### 저 자 소 개

#### 이귀준(李貴俊)

1979년 7월 19일생. 2005년 한양대 전자전기컴퓨터공학부 졸업. 2005년~현재 한양대대학원 전기공학과 석박사통합과정.

#### 현동석(玄東石)

1950년 4월 8일생. 1973년 한양대 전기공학과 졸업. 1978년 동 대학원 전기공학과 졸업(석사). 1986년 서울대 대학원 전기공학과졸업(공박). 1984년~1985년 미국 토레도대학 교환교수. 1988년~1989년 뮌헨공과대학

교환교수. 2003년 IEEE, Fellow Member. 1979년 ~ 현재 한양대 전기제어생체공학부 교수. 2000년 당 학회 회장 역임.