## 2009 전력전자학술대회 우수추천논문

# 0 ~ 100 % 시비율을 갖는 새로운 모드 가변형 비대칭 풀 브리지 DC/DC 컨버터

慎龍生<sup>\*</sup>, 盧政煜<sup>\*\*</sup>, 洪成洙<sup>\*\*</sup>, 韓翔圭<sup>†</sup>

A New Mode Changable Asymmetric Full Bridge DC/DC Converter having 0 ~ 100 % Duty Ratio

Yong-Saeng Shin, Chung-Wook Roh, Sung-Soo Hong, and Sang-Kyoo Han

요 약

본 논문에서는 대용량급 전력변환회로를 대상으로, 기존 위상천이 풀 브리지 컨버터의 환류 전류 문제를 해결하기 위하여 새로운 모드 가변형 비대칭 풀 브리지 컨버터를 제안한다. 제안된 회로는 구동시비율 D에 따라 50% 이하에서는 비대칭 풀 브리지 컨버터로 동작하며, 50% 이상에서는 능동 클램프 풀 브리지 컨버터로 동작하게 된다. 따라서 제안된 회로는 정상상태시 약 50% 시비율로 동작되므로 기존 위상천이 풀 브리지 컨버터의 문제점인 환류 전류를 제거 할 수 있으며, 이를 통하여 도통 손실을 줄일 수 있다. 또한, 넓은 부하범위에서 영전압 스위칭 동작이가능하며, 출력 전류 리플도 매우 작은 장점이 있다. 특히 순간정전시 능동 클램프 컨버터로 동작 모드가 변하여 50~100% 시비율로 동작되므로 넓은 입력전압범위에 대해 대응이 가능하다. 본 논문에서는 제안된 회로의 동작원리 및 PSIM simulation을 수행하였으며, 1.2kW급 시작품을 제작하여 제안된 회로의 타당성을 검증하였다.

#### **ABSTRACT**

In this paper, a new mode changeable asymmetric full bridge dc/dc converter is proposed to solve the freewheeling current problem of the conventional zero voltage switching(ZVS) phase shift full bridge(PSFB) dc/dc converter of low output voltage and high output current applications. The proposed converter is operated as an asymmetric full bridge converter when the duty cycle is less than 50% and active clamp full bridge converter when the duty cycle is greater than 50%. As a result, since its freewheeling current is eliminated, the conduction loss is lower than that of the conventional ZVS PSFB dc/dc converter. Moreover, ZVS of all power switches can be ensured along a wide load ranges and output current ripple is very small. Therefore, high efficiency of the proposed converter can be achieved. Especially since its operation mode is changed to the active clamp full bridge converter during hold up time and can be operated with 50~100% duty ratio, it can produce the stable output voltage along wide input voltage range. The operational principles, theoretical analysis and design considerations are presented. To confirm the operation, validity and features of the proposed converter, experimental results from a 1.2kW(400V<sub>dc</sub>/12V<sub>dc</sub>) prototype are presented.

Key Words: Asymmetric Full Bridge, Active Clamp Full Bridge, Mode Changable, Server Power Supply

<sup>†</sup>교신저자 : 정회원, 국민대 전자정보통신공학부 조교수

E-mail : djhan@kookmin.ac.kr

\*학생회원, 국민대 전자공학과 박사과정 \*\*정회원. 국민대 전자정보통신공학부 부교수

접수일자: 2010. 2. 23 1차 심사: 2010. 2. 24

심사완료 : 2010. 3. 8

1. 서 론

최근 산업화의 발전과 더불어 온실가스 배출 및 지구 온난화와 같은 환경문제에 대한 관심이 증폭되면서 전자기기들의 전력변환효율이 중요한 이슈사항이 되고

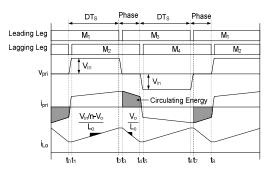

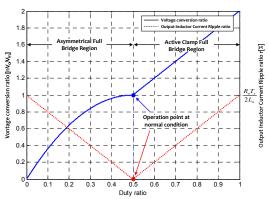

있다. 특히 최근에는 대용량급 전력변환회로의 고효율 화에 대해서 많은 연구가 이루어지고 있는 실정이다. 일반적으로 대용량급 전력변환회로로는 고전력밀도, 고효율, EMI 특성이 좋은 ZVS PSFB (Zero Voltage Switching Phase Shift Full Bridge) 컨버터가 많이 사 용되고 있다<sup>[1]~[5]</sup>. 기존 ZVS PSFB 컨버터의 입출력 전압변환비 및 출력 인덕터 전류의 리플률은 식 (1)~ (4)와 같으며, 구동시비율에 따라 50% 이상에서는 양 의 기울기-50% 이하에서는 음의 기울기를 갖는다. 따 라서 출력전압을 제어하기 위한 구동시비율의 가변범 위는 0~50%로 설정하는 것이 일반적이다. 또한 넓은 입력 전압 범위(hold up time)에 대한 동작을 보장하 기 위해서는 최대부하시 구동시비율을 약 30%로 사용 하므로, 그림 2에서와 같이 환류구간이 존재하고, 출력 인덕터 전류의 리플이 증가하게 된다. 이는 도통손실 및 스위칭손실을 증가시켜 효율을 떨어뜨릴 뿐만 아니 라, 출력 필터의 부피도 증가하는 문제점을 야기한다.

본 논문에서는 이러한 문제점을 해결하기 위하여 새 로운 모드 가변형 비대칭 풀 브리지 컨버터를 제안한 다. 제안된 회로는 구동시비율의 이용범위가 0~100 % 로 넓기 때문에, 입력 전압의 범위가 넓어지더라도 정상상태 구동시비율을 50%로 설정할 수 있는 특징이 있다. 따라서 환류구간이 존재하지 않아 효율 및 발열 특성이 우수하고, 출력 인덕터 전류 리플이 작아 소형 및 경량화에 매우 적합하다.

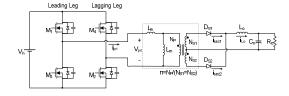

그림 1 영전압 스위칭 위상천이 풀 브리지 컨버터 Fig. 1 ZVS PSFB Converter

그림 2 영전압 스위칭 위상천이 풀브리지 컨버터의 주요동작파형 Fig. 2 Key operation waveforms of ZVS PSFB Converter

그림 3 위상천이 풀 브리지 컨버터의 입출력 전압 변환 비 및 출력 인덕터 전류의 리플률

Fig. 3 The Voltage conversion ratio and Output inductor current ripple ratio of ZVS PSFB converter

$$i) D \le 50\% \; \; ; \quad \frac{V_o}{V_{in}} = \frac{2D}{n}$$

(1)

$$r = \frac{\Delta i_{Lo}}{I_{Lo}} = \frac{(1 - 2D) R_o T_s}{2L_o}$$

(2)

$$ii) \ D \geq 50\% \quad ; \quad \frac{V_o}{V_{in}} = \frac{2(1-D)}{n} \tag{3}$$

$$r = \frac{\Delta i_{Lo}}{I_{Lo}} = \frac{-\left(1-2D\right)R_o \ T_s}{2L_o} \tag{4}$$

$$r = \frac{\Delta i_{Lo}}{I_{Lo}} = \frac{-(1-2D)R_oT_s}{2L_o} \tag{4}$$

## 2. 새로운 모드 가변형(Mode Changable) 비대칭 풀 브리지(Asymmetric Full Bridge) DC/DC 컨버터

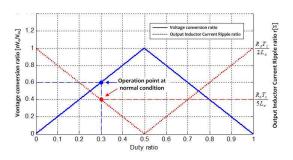

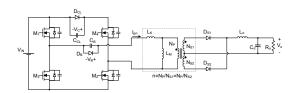

그림 4는 본 논문에서 제안하는 모드 가변형 비대칭 풀 브리지 컨버터를 나타내고 있다. 기존 ZVS PSFB 컨버터와 동일하게 4개의 스위치가 사용되며, Blocking 캐패시터(C<sub>B</sub>), Blocking 다이오드(D<sub>B</sub>), 클램 핑 캐패시터(C<sub>CL</sub>), 클램핑 다이오드(D<sub>CL</sub>)가 추가된 구 조이다. 제안된 회로는 DTs 구간동안 스위치 M<sub>1</sub>과 M<sub>2</sub>가 턴 온 되며, (1-D)Ts 구간동안 스위치 M<sub>3</sub>와 M<sub>4</sub> 가 턴 온 되어 구동한다. 제안회로는 구동시비율에 따 라 2개의 동작모드(normal mode/hold up time mode) 를 가지며, normal mode 시에는 비대칭 풀 브리지 컨 버터로 동작하고 hold up time mode 시에는 능동 클 램프 풀 브리지 컨버터로 동작한다[6]~[8]. 이는 클램핑 캐패시터( $C_{CL}$ ) 및 Blocking 캐패시터( $C_B$ ) 양단전압을 통하여 설명할 수 있으며, 이는 트랜스포머 양단전압 및 시간의 곱을 이용하여 다음과 같이 구할 수 있다.

$$V_{CL} = \frac{(2D-1)}{(1-D)} V_{in} \tag{5}$$

$$V_B = (1 - 2D) V_{in} (6)$$

즉, 구동시비율이 50% 이하일 경우에는 클램핑 캐패시터( $C_{CL}$ ) 양단전압이 0V 이하가 되어 클램핑 다이오드( $D_{CL}$ )가 도통하고, 그림 4(b)와 같은 비대칭 풀 브리지 컨버터로 동작하게 된다. 반대로 구동시비율이 50% 이상일 경우에는 Blocking 캐패시터( $C_B$ ) 양단전입이 0V 이하가 되어 Blocking 다이오드( $D_B$ )가 도통하고, 그림 4(c)와 같은 능동 클램프 풀 브리지 컨버터로 동작하게 된다. 따라서 제안회로는 구동시비율의 이용범위가  $0\sim100\%$ 로 넓으며, 약 50%의 정상상태 구동시비율을 가질 수 있는 특징이 있다.

(a) 제안된 모드 가변형 비대칭 풀 브리지 컨버터

(b) Normal mode시 등가회로(비대칭 풀 브리지 컨버터 동작)

(c) Hold-up time mode시 등가회로(능동 클램프 풀 브리지 동작)

그림 4 모드 가변형 비대칭 풀 브리지 컨버터 Fig. 4 Mode Changable Asymmetric Full Bridge Converter

#### 2.1 동작모드해석

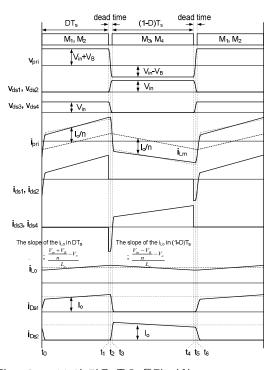

제안회로의 주요 동작 파형은 그림 5, 그림 6과 같 으며, 해석의 편의를 위하여 다음과 같은 가정을 한다.

- 입력 및 출력전압은  $V_{in}$  및  $V_{o}$ 로 일정하다.

- 비대칭 풀브리지 컨버터 동작시, 클램핑 캐패시터  $(C_{CL})$  양단전압은 0V,  $Blocking 캐패시터(C_B)$  양단전 압은  $V_B$ 로 일정하다.

- 능동 클램프 풀브리지 컨버터 동작시, 클램핑 캐패 시터( $C_{CL}$ ) 양단전압은  $V_{CL}$ , Blocking 캐패시터( $C_B$ ) 양단전압은 0V로 일정하다.

- $C_{eq}$ 는 1차측 스위치 출력 캐패시터 4개의  $\dot{a}(C_{M1}+C_{M2}+C_{M3}+C_{M4})$ 이다.

#### 2.1.1 비대칭 풀브리지 컨버터

모드  $1(t_0 \sim t_1)$  : 스위치  $M_1$ 과  $M_2$ 가 도통하고 있는 구간으로서,  $V_{in}+V_B$  전압이 트랜스포머 1차 측에 인가되어 정류다이오드  $D_{S1}$ 을 통하여 출력으로 에너지가전달되고 있는 구간이다. 따라서 자화인덕터  $L_m$ 의 전류는  $(V_{in}+V_B)/L_m$ 의 기울기로 선형적으로 증가한다.

$$i_{L_m}(t) = \frac{V_{in} + V_B}{L_m} t + i_{L_m}(t_0)$$

(7)

$$i_{pri}(t) = i_{Lm}(t) + \frac{i_{Lo}(t)}{n}$$

(8)

모드  $2(t_1 \sim t_2)$  :  $t_1$  시점에서 스위치  $M_1$ 과  $M_2$ 가 턴 오프 되면, 트랜스포머 1차 측으로 변환된 출력 인덕터 전류에 의하여 스위치  $M_3$ 와  $M_4$ 의 출력 캐패시터가방전하므로, 트랜스포머 1차 측 전압  $V_{pri}$ 는  $(V_{in}+V_B)$ 에서 0V까지 선형적으로 감소한다. 모드 2가 종료되는 1 시점에서 스위치 10 양단전압은 11 (12 이며, 스위치 13 14 양단전압은 15 이다.

모드  $3(t_2 \sim t_3)$  :  $t_2$  시점에서부터 정류다이오드  $D_{s1}$ ,  $D_{s2}$ 는 모두 도통하며, 1차측  $M_1 \sim M_4$  스위치의 출력 캐 패시터는 누설 인덕터  $L_k$ 와 공진을 한다. 이때 스위치  $M_3$ ,  $M_4$ 의 영전압 스위칭 동작을 위해서는 스위치  $M_3$ ,  $M_4$  양단전압을 0V까지 감소시킬 수 있을 만큼,  $t_2$ 시점에서  $L_k$ 에 저장된 에너지가 충분히 커야한다.

$$\begin{split} i_{pri}(t) &= i_{pri}(t_2) \cos \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_2 \right) \right\} \\ &- \frac{V_{in} + V_B}{2} \sqrt{\frac{C_{eq}}{L_k}} \sin \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_2 \right) \right\} \end{split} \tag{9}$$

$$\begin{split} V_{ds.M3,M4} &= \frac{V_{i\,n} - V_B}{2} \cos \biggl\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_2 \right) \biggr\} \\ &- i_{pri}(t_2) \sqrt{\frac{L_k}{C_{eq}}} \sin \biggl\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_2 \right) \biggr\} \end{split} \tag{10}$$

모드  $4(t_3 \sim t_4)$ :  $t_3$ 인 시점에서 스위치  $M_3$ 와 스위치  $M_4$ 의 양단전압은 0V가 되어 스위치의 바디다이오드가 도통하게 되며, 이후 스위치  $M_3$ 와  $M_4$ 는 영전압 스위칭 동작을 한다. 모드 4구간동안에는  $(-V_{in}+V_B)$  전압이 트랜스포머 1차측에 인가되어 정류다이오드  $D_{S2}$ 를 통하여 출력으로 에너지를 전달하며, 이때 자화인덕터  $L_m$ 의 전류는  $(-V_{in}+V_B)/L_m$ 의 기울기로 선형적으로 감소한다.

$$i_{Lm}(t) = \frac{-V_{in} + V_B}{L_m}(t - t_3) + i_{Lm}(t_3)$$

(11)

$$i_{pri}(t) = i_{Lm}(t) - \frac{i_{Lo}(t)}{n}$$

(12)

모드  $5(t_4 \sim t_5)$ :  $t_4$  시점에서 스위치  $M_3$ 와  $M_4$ 가 턴 오프 되면, 트랜스포머 1차 측으로 변환된 출력 인덕터 전류에 의하여 스위치  $M_1$ 과  $M_2$ 의 출력 캐패시터가 방전하므로, 트랜스포머 1차 측 전압  $V_{pri}$ 는  $(-V_{in}+V_B)$ 에서부터 0V까지 선형적으로 증가한다. 모드 5가 종료되는  $t_5$  시점에서 스위치  $M_1$ ,  $M_2$ 의 양단전압은  $(V_{in}+V_B)/2$ 이며, 스위치  $M_3$ ,  $M_4$ 의 양단전압은  $(V_{in}-V_B)/2$ 이다.

모드  $6(t_5 \sim t_6)$ :  $t_5$  시점에서부터 정류다이오드  $D_{s1}$ ,  $D_{s2}$ 는 모두 도통상태가 되며, 이 구간동안 1차측  $M_1$   $\sim M_4$  스위치의 출력 캐패시터는 누설 인덕터  $L_k$ 와 공진을 한다. 이때 스위치  $M_1$ ,  $M_2$ 의 영전압 스위칭 동작을 위해서는 스위치  $M_1$ ,  $M_2$ 의 양단전압을 0V까지 감소시킬 수 있을 만큼,  $t_5$ 시점에서  $L_k$ 에 저장된 에너지가 충분히 커야한다. 모드 6은 스위치  $M_1$ ,  $M_2$ 의 양단전압이 0V가 되는 시점인  $t_6$ 에서 종료되며, 이후 스위치  $M_1$ ,  $M_2$ 는 영전압 스위칭 동작을 하게 된다. 여기서  $t_6$  시점은 한주기 앞의  $t_0$  시점과 동일하며, 이후 모드  $1\sim$ 모드  $t_0$  까지의 동작이 반복적으로 이루어진다.

그림 5 D ≤ 50% 의 경우 주요 동작 파형

Fig. 5 Key waveforms when the duty ratio is less than 50%

$$\begin{split} i_{pri}(t) &= i_{pri}(t_5) \cos \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_5 \right) \right\} \\ &- \frac{V_{in} + V_B}{2} \sqrt{\frac{C_{eq}}{L_k}} \sin \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_5 \right) \right\} \end{split} \tag{13}$$

$$\begin{split} V_{ds.M1,M2} &= \frac{V_{in} + V_B}{2} \cos \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_5 \right) \right\} \\ &+ i_{pri}(t_5) \sqrt{\frac{L_k}{C_{eq}}} \sin \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_5 \right) \right\} \end{split} \tag{14}$$

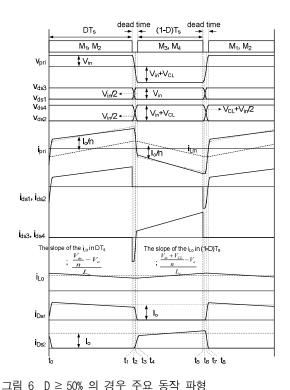

#### 2.1.2 능동클램프 풀브리지 컨버터

모드  $1(t_0 \sim t_1)$  : 스위치  $M_1$ 과  $M_2$ 가 도통하고 있는 구간으로서,  $V_{in}$  전압이 트랜스포머 1차 측에 인가되어 정류다이오드  $D_{S1}$ 을 통하여 출력으로 에너지가 전달되고 있는 구간이다. 따라서 자화인덕터  $L_m$ 의 전류는  $V_{in}/L_m$ 의 기울기로 선형적으로 증가한다.

$$i_{Lm}(t) = \frac{V_{in}}{L_m} t + i_{Lm}(t_0) \tag{15}$$

$$i_{pri}(t) = i_{Lm}(t) + \frac{i_{Lo}(t)}{n}$$

(16)

모드  $2(t_1 \sim t_2)$  :  $t_1$  시점에서 스위치  $M_1$ 과  $M_2$ 는 턴 오프 되면, 트랜스포머 1차 측으로 변환된 출력 인덕터 전류에 의하여 스위치  $M_3$ 와  $M_4$ 의 출력 캐패시터가 방전하므로, 트랜스포머 1차 측 전압  $V_{pri}$ 는  $V_{in}$ 에서부터 0V까지 선형적으로 감소한다. 모드 2가 종료되는  $t_2$  시점에서 스위치  $M_1$ ,  $M_2$ ,  $M_3$ 의 양단전압은  $V_{in}/2$  이 며, 스위치  $M_4$ 의 양단전압은  $(V_{in}/2+V_{CL})$  이다.

모드  $3(t_2 \sim t_3)$  :  $t_2$  시점에서부터 정류다이오드  $D_{sl}$ ,  $D_{s2}$ 는 모두 도통하며, 이 구간동안 1차측  $M_1 \sim M_4$  스위치의 출력 캐패시터는 누설 인덕터  $L_k$ 와 공진을 한다. 이때 스위치  $M_3$ ,  $M_4$ 의 영전압 스위칭 동작을 위해서는 스위치  $M_3$ ,  $M_4$  양단전압을 0V까지 감소시킬 수있을 만큼,  $t_2$ 시점에서  $L_k$ 에 저장된 에너지가 충분히커야한다. 아래 식  $(17) \sim (19)$ 은 1차측 전류와 스위치  $M_3$ ,  $M_4$ 의 양단전압을 나타내고 있다.

$$i_{pri}(t) = i_{pri}(t_2) \cos \left\{ \sqrt{\frac{1}{L_k C_{eq}}} (t - t_2) \right\}$$

$$- \frac{V_{in}}{2} \sqrt{\frac{C_{eq}}{L_k}} \sin \left\{ \sqrt{\frac{1}{L_k C_{eq}}} (t - t_2) \right\}$$

(17)

$$\begin{split} V_{ds.M3} &= \frac{V_{in}}{2} \cos \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_2 \right) \right\} \\ &- i_{pri}(t_2) \sqrt{\frac{L_k}{C_{eq}}} \sin \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_2 \right) \right\} \end{split} \tag{18}$$

$$V_{ds.M4} = \left(V_{CL} + \frac{V_{in}}{2}\right) \cos\left\{\sqrt{\frac{1}{L_k C_{eq}}} (t - t_2)\right\}$$

$$-i_{pri}(t_2) \sqrt{\frac{L_k}{C_{eq}}} \sin\left\{\sqrt{\frac{1}{L_k C_{eq}}} (t - t_2)\right\}$$

(19)

모드  $4(t_3 \sim t_4)$ :  $t_3$  시점에서 스위치  $M_3$ 의 양단전압은 0V가 되어, 스위치의 바디다이오드가 도통한다. 따라서 모드 4에서는 스위치  $M_2$ ,  $M_4$ 의 출력 캐패시터와 누설 인덕터  $L_k$ 가 공진을 하게 된다.

$$\begin{split} i_{pri}(t) &= i_{pri}(t_3) \cos \left\{ \sqrt{\frac{2}{L_k C_{eq}}} \left( t - t_3 \right) \right\} \\ &- V_{in} \sqrt{\frac{C_{eq}}{2L_k}} \sin \left\{ \sqrt{\frac{2}{L_k C_{eq}}} \left( t - t_3 \right) \right\} \\ V_{ds.M4} &= \left( V_{CL} \right) \cos \left\{ \sqrt{\frac{2}{L_k C_{eq}}} \left( t - t_3 \right) \right\} \\ &- i_{pri}(t_3) \sqrt{\frac{2L_k}{C_{eq}}} \sin \left\{ \sqrt{\frac{2}{L_k C_{eq}}} \left( t - t_3 \right) \right\} \end{split} \tag{21}$$

모드  $5(t_4 \sim t_5)$ :  $t_4$ 인 시점에서 스위치  $M_4$ 의 양단전 압은 0V가 되어 스위치의 바디다이오드가 도통하게 되며, 이후 스위치  $M_3$ 와  $M_4$ 는 영전압 스위칭 동작을 한다. 모드 5구간동안에는  $(-V_{in}-V_{CL})$  전압이 트랜스포머 1차측에 인가되어 정류다이오드  $D_{S2}$ 를 통하여 출력으로에너지를 전달하며, 이때 자화인덕터  $L_m$ 의 전류는 선형적으로 감소하며  $(-V_{in}-V_{CL})/L_m$ 의 기울기를 갖는다.

$$i_{Lm}(t) = \frac{-V_{in} - V_{CL}}{L_{...}}(t - t_4) + i_{Lm}(t_4)$$

(22)

$$i_{pri}(t) = i_{Lm}(t) - \frac{i_{Lo}(t)}{n}$$

(23)

모드  $6(t_5 \sim t_6)$  :  $t_5$  시점에서 스위치  $M_3$ 와  $M_4$ 가 턴 오프 되면, 트랜스포머 1차 측으로 변환된 출력 인덕터 전류에 의하여 스위치  $M_1$ 과  $M_2$ 의 출력 캐패시터가방전하므로, 트랜스포머 1차 측 전압  $V_{pri}$ 는  $(-V_{in}-V_{CL})$ 에서부터 0V까지 선형적으로 증가한다. 모드 6이 종료되는  $t_6$  시점에서 스위치  $M_1$ ,  $M_2$ ,  $M_4$ 의 양단전압은  $V_{in}/2$  이며, 스위치  $M_3$ 의 양단전압은  $(V_{in}/2+V_{CL})$ 이다.

모드  $7(t_6 \sim t_7)$ :  $t_6$  시점에서부터 정류다이오드  $D_{s1}$ ,  $D_{s2}$ 는 모두 도통상태가 되며, 이 구간동안 1차측  $M_1 \sim M_4$  스위치의 출력 캐패시터는 누설 인덕터  $L_k$ 와 공진을 한다. 이때 스위치  $M_1$ ,  $M_2$ 의 영전압 스위칭 동작을 위해서는 스위치  $M_1$ ,  $M_2$  양단전압을 OV까지 감소시킬수 있을 만큼.  $t_6$ 시점에서  $L_k$ 에 저장된 에너지가 충분

기급 6 비존 30% 의 경구 구표 공의 파영

Fig. 6 Key waveforms when the duty ratio is greater

than 50%

히 커야한다. 아래 식 (24)~(26)은 1차측 전류와 스위 치 M<sub>1</sub>, M<sub>2</sub>의 양단전압을 나타내고 있다.

$$i_{pri}(t) = i_{pri}(t_6) \cos \left\{ \sqrt{\frac{1}{L_k C_{eq}}} (t - t_6) \right\}$$

$$- \frac{V_{in}}{2} \sqrt{\frac{C_{eq}}{L_k}} \sin \left\{ \sqrt{\frac{1}{L_k C_{eq}}} (t - t_6) \right\}$$

(24)

$$\begin{split} V_{ds.M1} &= \frac{V_{in}}{2} \cos \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_6 \right) \right\} \\ &+ i_{pri}(t_6) \sqrt{\frac{L_k}{C_{eq}}} \sin \left\{ \sqrt{\frac{1}{L_k C_{eq}}} \left( t - t_6 \right) \right\} \end{split} \tag{25}$$

$$\begin{split} V_{ds.M2} &= \left(V_{CL} + \frac{V_{in}}{2}\right) \cos \left\{\sqrt{\frac{1}{L_k C_{eq}}} \left(t - t_6\right)\right\} \\ &+ i_{pri}(t_6) \sqrt{\frac{L_k}{C_{eq}}} \sin \left\{\sqrt{\frac{1}{L_k C_{eq}}} \left(t - t_6\right)\right\} \end{split} \tag{26}$$

모드  $8(t_7 \sim t_8)$  :  $t_7$  시점에서 스위치  $M_1$ 의 양단전압은 0V가 되어, 스위치의 바디다이오드가 도통한다. 따라서 모드 8에서는 스위치  $M_1$ ,  $M_3$ 의 출력 캐패시터와 누설 인덕터  $L_k$ 가 공진을 하게 된다. 모드 8은 스위치  $M_2$ 의 양단전압이 0V가 되는 시점인  $t_8$ 에서 종료되며, 이후 스위치  $M_1$ ,  $M_2$ 는 영전압 스위칭 동작을 하게 된다. 여기서  $t_8$  시점은 한주기 앞의  $t_0$  시점과 동일하며,

이후 모드 1~8 까지의 동작이 반복적으로 이루어진다.

$$\begin{split} i_{pri}(t) &= i_{pri}(t_7) \cos \left\{ \sqrt{\frac{2}{L_k C_{eq}}} \left( t - t_7 \right) \right\} \\ &- V_{in} \sqrt{\frac{C_{eq}}{2L_k}} \sin \left\{ \sqrt{\frac{2}{L_k C_{eq}}} \left( t - t_7 \right) \right\} \end{split} \tag{27}$$

$$\begin{split} V_{ds.M2} &= \left(V_{CL}\right) \cos \left\{\sqrt{\frac{2}{L_k C_{eq}}} \left(t - t_7\right)\right\} \\ &+ i_{pri}(t_7) \sqrt{\frac{2L_k}{C_{eq}}} \sin \left\{\sqrt{\frac{2}{L_k C_{eq}}} \left(t - t_7\right)\right\} \end{split} \tag{28}$$

## 3. 설계고려사항

## 3.1 입출력 전압변환비(M) 및 출력 인덕터 전류 리플율(r)

제안된 회로는 구동시비율에 따라 비대칭 풀브리지 컨버터 또는 능동클램프 풀브리지 컨버터로 동작하게 된다. 각각의 경우 입출력 전압변한비(M)와 출력 인덕 터 전류의 리플률(r)은 다음과 같다.

$$i) D \le 50\%$$

;  $M = \frac{V_o}{V_{in}} = \frac{4D(1-D)}{n}$  (29)

$$r = \frac{\Delta i_{Lo}}{I_{Lo}} = \frac{(1 - 2D) R_o T_s}{2L_o}$$

(30)

$$ii) D \ge 50\%$$

;  $M = \frac{V_o}{V_{in}} = \frac{2D}{n}$  (31)

$$r = \frac{\triangle i_{Lo}}{I_{Lo}} = \frac{-\left(1 - 2D\right)R_{o}T_{s}}{2L_{o}} \tag{32}$$

상기 입출력 전압변환비와 출력 인덕터 전류의 리플율을 그래프로 도시하면 그림 7과 같다. 입출력 전압 변환비는 구동시비율에 상관없이 양의 기울기를 가지

그림 7 제안회로의 입출력 전압변환비 및 출력 인덕터 전류의 리플율

Fig. 7 The Voltage conversion ratio and Output inductor current ripple ratio of proposed converter

며, 출력 인덕터 전류 리플율은 기존 위상천이 풀 브리지 컨버터와 동일하다. 입출력 전압이득곡선에서 알수 있듯이 제안회로는 구동시비율을 0~100%까지 전구간에서 이용할 수 있으므로, 넓은 입력 전압 범위(Hold-up time)를 고려하더라도 정상상태 구동시비율을 약 50%로 할 수 있는 장점을 갖는다. 이는 기존환류구간으로 인해 발생하게 되는 도통손실을 줄일 수 있으며, 출력 인덕터 전류 리플을 최소화키실 수 있다.

#### 3.2 영전압 스위칭

제안회로는 정상상태 동작일 경우 비대칭 풀 브리지 컨버터로 동작하기 때문에, 비대칭 풀 브리지 컨버터 동작일 경우의 영전압 스위칭 동작이 우선적으로 고려되어야 한다. 또한 보조 스위치( $M_3$ ,  $M_4$ )보다는 주스위치( $M_1$ ,  $M_2$ )가 영전압 스위칭 동작에 불리하므로, 주스위치의 영전압 스위칭 조건을 고려하여 누설 인덕터를설계하여야 한다.

상기 비대칭 풀 브리지 컨버터의  $t_5$  시점에서 누설 인덕터에 저장된 에너지는 식 (33)와 같이 나타낼 수 있으며, 영전압스위칭 동작을 위하여 필요한 에너지는 식 (34)과 같다. (여기서 PL은 최대부하에 대한 영전압 스위칭이 보장되는 최소부하의 퍼센트(%) 비율을 의미한다)

$$E_{stored} = \frac{1}{2} L_{k} I^{2} = \frac{1}{2} L_{k} \left( i_{Lm}(t_{5}) + \frac{PL \times I_{o}}{n} \right)^{2} \tag{33}$$

$$E_{required} = \frac{1}{2}CV^2 = \frac{1}{2}C_{eq}\left(\frac{V_{in} + V_B}{2}\right)^2$$

(34)

따라서 영전압 스위칭 동작을 위한 최소 누설 인덕 턴스는 다음과 같다.

$$L_{k,\min} \ge C_{eq} \left( \frac{\frac{V_{in} + V_B}{2}}{i_{Lm}(t_5) + \frac{PL \times I_o}{n}} \right)^2$$

(35)

## 4. 모의실험 및 실험결과

## 4.1 모의 실험

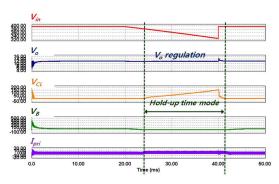

그림 8은 본 논문에서 제안된 모드가변형 비대칭 풀 브리지 컨버터의 모의실험을 나타내고 있다. 모의실험은 PSIM tool을 사용하였으며, 모의실험조건은 표2과 같다. 초기  $V_{in}$  전압을 인가한 후 20msec 지점에서부터 입력전압을 선형적으로 감소시켰으며, 이때 자연스러운 모드전환을 통하여 출력전압의 제어가 잘 이루어짐을 확인할 수 있다(그림 8(a)). 최대부하시 구동시비율은 46.3%이며, 출력 인덕터 전류 리플의 크기는 약

표 2 제안회로의 주요 정격 및 파라미터 Table 2 The specifications and parameters of the proposed converter

| 항 목                  | Value      | 항 목                    | Value          |

|----------------------|------------|------------------------|----------------|

| Vin                  | 400 V      | turn ratio of trans.   | 30 :1:1        |

| Vo                   | 12 V       | Magnetizing Inductance | 1.2 mH         |

| switching frequency  | 65kHz      | Leakage Inductance     | 22 uH          |

| Clamping capacitor   | 2.2uF      | Output Inductor        | 1.8 uH         |

| Blocking capacitor   | 2.2uF      | Output Capacitor       | 330 uF *5      |

| MOSFET               | SPP20N60C3 | Blocking Diode         | Cree CSD 06060 |

| Syncronous Rectifier | IRFB3077   | Clamping Diode         | Cree CSD 06060 |

5.6A 이다(그림 8(b)). 이는 동일한 조건(스위칭 주파수, 자화 인덕턴스, 출력 인덕턴스)하에서 ZVS PSFB 컨버 터(약 25A)에 비해 매우 작은 값으로, 출력 필터의 사 이즈 및 고효율 측면에서 유리하다.

(a) 입력전압변동에 따른 출력전압제어

(b) 최대부하시 주요 동작파형 그림 8 PSIM 모의실험 결과 Fig. 8 PSIM simulation result

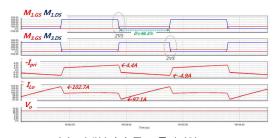

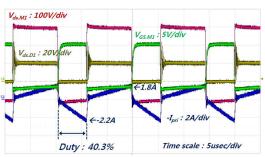

#### 4.2 실험 결과

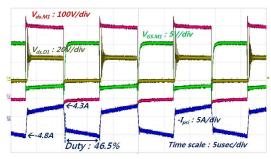

다음은 1.2kW급 서버용 컴퓨터 전원장치 시작품 제 작 및 실험에 대한 내용이다. 누설인덕터에 의한 duty cvcle loss를 고려하여 턴 비를 30:1로 사용하였을 경 우, 최대부하에서 제안회로의 구동시비율은 약 46.5% 이다. 이때 1차측 전류는 -4.8 ~ 4.3 A 로, 앞의 모의

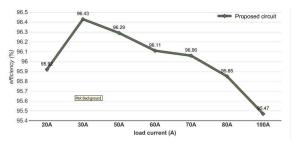

실험파형과 잘 부합하며, 영전압 스위칭 동작이 잘 이 루어짐을 확인할 수 있다(그림 9). 주요 동작 파형에서 알 수 있듯이 제안회로는 환류구간이 존재하지 않으 며, 넓은 범위에서 영전압스위칭 동작이 이루어지고, 또한 부하의 크기가 클 수록 1차측 전류의 offset성분 이 작으므로 효율 특성이 우수하다. 그림 10는 부하전 류크기에 따른 효율 측정치를 나타내고 있다. 20%이 상의 모든 부하조건에서 95% 이상의 효율 특성을 나 타내고 있으며, 30% 부하조건에서 최고 96.43%의 효 율이 측정되었다. 특히 최대부하시(100A)에도 95.47% 의 고효율이 측정됨으로써, 제안회로가 대용량에 매우 적합함을 확인할 수 있다.

(a) 20% 부하에서의 각 부 주요파형

(b) 100% 부하에서의 각 부 주요파형

그림 9 부하전류에 따른 각 부 주요파형 Fig. 9 Measured waveforms vs.load current

그림 10 효율 측정 결과 Fig. 10 Measured efficiency

#### 5. 결 론

본 논문에서는 대용량 DC/DC 컨버터의 고효율화를 위한 새로운 모드 가변형 비대칭 풀 브리지 컨버터를 제안하였다. 제안된 회로는 구동 시비율 D를 0~100%까지 폭넓게 이용할 수 있으며, 50% 이하에서는 비대칭 풀 브리지 컨버터로 50% 이상에서는 능동 클램프풀 브리지 컨버터로 동작한다. 따라서, 기존 ZVS PSFB 컨버터의 문제점인 환류구간이 존재하지 않아효율 및 발열 특성이 우수하며, 출력 인덕터 전류의리플이 작다. 제안회로의 타당성을 검증하기 위하여, 1.2kW (12V/100A)급을 대상으로 시작품을 제작하여실험을 수행하였다. 실험결과 제안된 회로는 20% 이상의 모든 부하조건에서 95% 이상의 고효율을 얻을수 있었으며, 특히 최대부하(100A) 조건에서도 95.47%의 고효율을 보임으로써 제안된 회로가 대용량에 매우적합함을 확인하였다.

본 연구는 2009년도 국민대학교 교내 연구비지원과 지식경제부 및 정보통신연구진흥원의 대학 IT연구센터 지원사업의 연구결과로 수행되었음 (IITA - 2009 - C1090 - 0904 - 0002)

## 참 고 문 헌

- [1] J. A. Sabate, V. Vlatkovic, R. B. Redley, F. C. Lee and B. H. Cho, "Design considerations for high-voltage high- power full bridge zero voltage-switched PWM converter", in Proc. IEEE APEC'90, pp. 275-284, 1990.

- [2] L. H. Mweene, C. A. Wright, and M. F. Schlecht, "A 1kW 500kHz front-end converter for a distributed power supply system", *IEEE Trans. Power Electron.*, Vol. 6, No. 3, pp. 398-407, 1991, July.

- [3] Richard Redl, "A Novel Soft-Switching Full-Bridge DC/DC Converter: Analysis, Design Considerations, and Experimental Results at 1.5kW, 100kHz", Proceedings of the IEEE, Vol. 6, Issue 3, pp. 408-418, 1991, July.

- [4] Dong Li, "Comparison of Three Front-end DC-DC Converters for 1200W Server Power Supply", Proceedings of the IEEE, PESC 2005, pp. 394-398, 2005, Sept.

- [5] J.M. Zhang, X.G Xie, X.K. Wu, Zhaoming Qian, " Comparison study of phase-shifted full bridge ZVS converters", Proceedings of the IEEE, PESC 04, pp. 533–539, 2004, June.

- [6] Guan-Chyun Hsieh, Chi-Yeh Kuo, "Modeling and Design Considerations for ZVS Asymmetrical Half-Bridge Converter", TENCON 2005 2005 IEEE Region 10, pp. 1-6, 2005, Nov.

- [7] Alpha J. Zhang, Guisong Huang, Yilei Gu, "Asymmetrical Full Bridge DC-to-DC Converter", US Patent, US6466458 B2, 2002, Oct.

- [8] J. Feng, Y. Hu, W. Chen and C. C. Wen, "ZVS analysis of asymmetrical half-bridge converter", IEEE PESC, Vol. 1, pp. 243–247, 2001.

## 저 자 소 개

## 신용생(愼龍生)

1982년 8월 31일생. 2007년 국민대 공과 대학 전자공학부 졸업. 2009년 동대학원 전자공학과 졸업(석사). 2009년~현재 동 대학원 전자공학과 박사과정.

#### 노정욱(盧政煜)

1971년 9월 10일생. 1993년 한국과학기술 원 전기 및 전자공학과 졸업. 1995년 동 대학원 전기 및 전자공학과 졸업(석사). 2000년 동 대학원 전기 및 전자공학과 졸업(공박). 2000년~2004년 삼성전자(주)

영상 디스플레이 사업부 책임연구원. 2004년~현재 국민대 전자정보통신공학부 부교수. 당 학회 국문지 편집위원.

## 홍성수(洪成洙)

1961년 1월 25일생. 1984년 서울대 전기 공학과 졸업. 1986년 한국과학기술원 전 기 및 전자공학과 졸업(석사). 1992년 동 대학원 전기 및 전자공학과 졸업(공박). 1984년~1999년 현대전자(주) 정보통신

연구소 책임연구원. 1999년~현재 국민대 전자정보통신공학 부 부교수.

#### 한상규(韓翔圭)

1973년 12월 13일생. 1999년 2월 부산대 전기공학과 졸업. 2001년 2월 한국과학기 술원 전자전산학과 졸업(석사). 2005년 2 월 동 대학원 전자전산학과 졸업(공박). 2005년 3월~2005년 8월 한국과학기술원

\_\_\_\_\_ 정보전자연구소 박사후연구원. 2005년 9월~현재 국민대 전 자정보통신공학부 조교수.