# ZnO Power FET 모델링에 관한 연구 Study on Modeling of ZnO Power FET

강 이 구\*, 정 헌 석\*\* Ey Goo Kang\*, Hunsuk Chung\*\*

#### Abstract

In this paper, we proposed ZnO trench Static Induction Transistor(SIT). Because The compound semiconductor had superior thermal characteristics, ZnO and SiC power devices is next generation power semiconductor devices. We carried out modeling of ZnO SIT with 2-D device and process simulator. As a result of modeling, we obtained 340V breakdown voltage. The channel thickness was 3um and the channel doping concentration is 1e17cm-3. And we carried out thermal characteristics, too.

#### 요 약

본 논문에서는 차세대 전력반도체인 화합물 반도체 소자중 ZnO 전력소자에 대하여 모델링을 수행하였다. 화합물 전력 반도체 소자는 와이드 밴드 갭 소자로서 열 특성이 우수해 자동차 및 계통연계형 인버터의 차세대 핵심소자로 인정받고 있다. 모델링 결과 에피 두께가 3um, 도핑농도는  $1e17cm^{-3}$ 일때 내압 340V 정도 얻을 수 있었으며, 관련 I-V특성 등을 평가하였다. 실제 소자로 제작된다면 300V이내의 산업 응용에 충분히 활용할 수 있을 것으로 판단된다.

Key words: Static Induction Transistor, ZnO, Epi layer, High Voltage, Power Devices

## I . 서론

최근 전기전자 산업중 가장 주목받는 분야의하나로 부상하고 있는 고전압 대용량 전력전자 산업에 있어서 전력 변환 장치 및 제어 장치의 핵심부품으로 활용되고 있는 전력용 반도체 소자는 전력용 바이폴라 트랜지스터의 개발과 더불어 급진적인 발전의 계기를 맞이하였으며, 그후 전력용

MOSFET, IGBT(Insulated Gate Bipolar Transisto), MCT(MOS Controlled Thyristor), SIT(Static Induction Thyristor)등이 개발되어 기존에 있던 사이리스터, GTO등과 함께 널리 사용되고 있는 중이다.[1-2]

이러한 전력용 반도체 소자는 산업 시스템의 신뢰성을 높이고 다기능화 하면서 대용량화 및 고내압화를 실현시키기 위한 핵심부품으로 기존의 가전 및 산업용 뿐 만 아니라 교통 분야에서 고속전철, 전기자동차, 전력분야의 FACTS(Flexible AC Transmission System, 가변성 교류 송전), HVDC(High Voltage DC, 초고압 직류) 송전 및미사일 관련 장비 계통의 시스템화와 군사정보 시스템인 Micro-Airplane의 설계 제작 등에도 크게이용될 것으로 기대되고 있다.[3-5]

한편, 전력반도체의 응용이 대용량으로 진행되면 서 Si 전력반도체 칩의 크기와 내구성이 문제되면

<sup>\*</sup> 極東大學校 太陽光工學科

<sup>(</sup>Department of Photovoltaic Engineering, Far East University)

<sup>★</sup> 교신저자 (Corresponding author)

<sup>※</sup> 감사의 글 (Acknowledgment)

본 연구는 한국연구재단 기초연구사업에 의해 수행되었음.

接受日:2010年 12月 3日, 修正完了日: 2010年 12月 28日

서 최근에는 ZnO 및 SiC와 같은 화합물 전력반도체의 요구가 증가되고 있다. 화합물 전력반도체는 와이드 갭 반도체로서 열 특성 및 온 저항 특성이 기존의 Si에 비해 월등히 우수해 차세대 전력반도체로 인정받고 있는 실정이다. 하지만 접합의 형성이 어려워 전력 반도체 소자로서의 제작은 어려운 문제점이 있다.

본 연구에서는 이러한 화합물 전력반도체 소자의 형성에 있어서 설계에 기초가 되는 소자의 설계 및 공정파라미터를 최적화하기 위해 소자의 모델 링을 수행하였으며, 모델링한 소자는 정전유도트랜 지스터(Static Induction Transistor, SIT)이며, 해 당소자의 항복특성 및 열 특성을 고찰하였다.

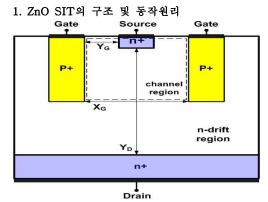

그림 1. 일반적인 전력 SIT 구조

Fig. 1 The structure of conventional Power SIT

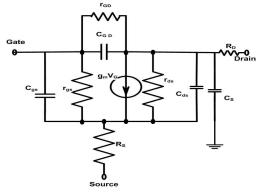

그림 2. 전력 SIT의 등가회로

Fig.2 The equivalent circuit of Power SIT

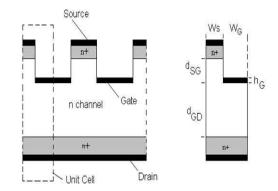

그림 3. 제안한 트렌치 전력 SIT 구조 Fig. 3 The structure of Trench Power SIT

그림 1은 일반적인 전력 SIT를 나타낸 구조이며, 그림 2는 전력 SIT 소자의 등가회로를 보여주고 있다. 그림 3은 본 연구에서 수행한 ZnO 트렌치 SIT구조를 나타내고 있다.

Si 기반 혹은 ZnO 기반의 SIT의 동작원리는 소자의 구조에서 결정되는 것이기 때문에 그 원리는 같다

대전류를 수반하는 고내압 전력용 반도체 소자는 수 직형 전류전도경로를 가지고 만들어진다. 수직형 전 류전도경로는 전계집중현상을 최소화하고, 이를 통해 이상적인 항복전압 특성을 얻을 수 있게 된다. 또한 대전류를 수반하는 터미널이 수직구조로 소자 윗부분 과 아랫부분의 전극이 설정되어 소자의 면적을 감소 시키는 이점을 가지고 있다. 전력용 파워 SIT의 구조 또한 수직형 구조를 가지고 있는데, 그림 1에서 보는 것처럼 기판에 드레인 전극과 n+층으로 구성되어 있 고, 소자 위쪽 가운데 n+ 소오스 영역이 존재하며, 소 오스 영역을 기준으로 양쪽으로 게이트 영역이 존재 한다. 게이트와 게이트와의 간격, 소오스와 게이트간 의 거리는 편히상 게이트 확산길이와 소오스 확산길 이의 중간에 위치하고,  $X_G$ 의 값은 게이트와 게이트 간격을 척도로 파라미터 u에서 온 식에서 구체적으로  $\mu$ 인  $(Y_D - Y_G)/X_G$  에 일치하게 정한다.

SIT는 채널이 완전히 공핍화되어 있기 때문에 다수캐리어가 소오스에서 드레인내에 주입되어 고전류내를 포화속도로 주행하는 소자이다. 그래서 캐리어주행시간이 짧고, 주행속도가 빠르기 때문에 드레인영역 길이를 길게 할 수 있으므로 블로킹 전압을 높일 수 있어 고압용으로 사용될 수 있는 전력용 반도

체 소자이다. 또한, 채널영역의 길이를 기존에 비해 길게 설계함으로써 보다 높은 블로킹 전압을 얻을 수 있지만, 순방향 전도특성 모드에서 전류가 흐르지 않 을 수 있으므로 순방향 전도특성과 블로킹 특성을 고 려하여 설계를 하여야 한다.

그림 2.2는 기존의 수직형 파워 SIT의 등가회로 이다. JFET과 비교해서 같은 등가회로를 가지며,  $r_{qs}$ 와  $C_{as}$  파라미터는 각각 게이트-소오스간 확산 저항 과 접합 커패시턴스이다. 정상적으로  $r_{as}$ 가 크도록, 게이트-소오스간 접합은 공핍모드 소자에 대해 역방 향으로 바이어스되고 증가모드 소자에 대해 오직 낮 은 순방향 바이어스 전압을 가진다. 파라미터  $r_{ad}$ 와  $C_{od}$ 는 각각 게이트와 소오스간 저항과 커패시턴스이 다. 저항  $r_{ad}$ 는 채널길이 변조효과의 함수인 한정된 드레인 저항이고,  $R_D$ 는 드리프트 영역의 저항이다. 커팬시턴스  $C_{od}$ 는 주로 드레인-소오스간 기생 커패시 턴스이고, 게이트 역방향 전압이 증가할수록 게이트 접합 공핍영역은 확대되면서  $C_{gd}$ 는 감소를 하게 된 다. 반대로  $R_{S}$ 는 게이트 역방향 전압이 증가할수록 증가하게 된다. 이것은 공핍영역의 확장으로 인한 채 널영역의 감소 때문이다.  $C_s$ 는 드레인-기판간 커패시 턴스이다.  $g_m$ 는 트랜스컨덕턴스를 나타내며, 드레인 과 게이트 전압에 종속적인 관계를 갖는다.

SIT의 가장 중요한 파라미터로서 게이트 영역들과의 거리와 채널 영역의 도핑레벨이고, 공핍모드 (nomally-on)소자를 만들기 위해서 두 파라미터를 이용하여 게이트에 바이어스를 인가하지 않은 상태에서 공핍영역들이 서로 병합되지 않도록 조절을 하여야한다.

게이트에 바이어스를 걸어주지 않았을 때, 드레인과 소오스 사이에의 전류의 흐름은 n-층에서의 저항에 의해 제한을 받는다. n-층의 영역은 2가지 영역으로 나눌 수 있는데, 하나는 채널 영역이고, 나머지는 드리프트 영역이다. 게이트 접합사이의 부분을 채널 영역, 게이트 접합 아래의 부분을 드리프트 영역이라 하며 두 영역에 해당하는 저항들을 포함한 전체 저항은 전류의 흐름에 크게 영향을 주게 된다.

게이트에 역바이어스를 걸어주면 게이트 접합의 공핍 영역이 점점 채널 영역으로 확장을 하게 된다. 공핍영역은 자유캐리어가 결여된 부분이기 때문에 게 이트에 역바이어스를 더욱 증가를 시키게 되면 채널 영역의 저항은 증가를 하게 된다. 결국, 게이트 역바 이어스를 통하여 게이트 접합 공핍영역을 변화시키고, 이를 통해 SIT의 저항을 변화시킨다. 채널 영역의 저항의 변화로 인해 SIT의 채널 전도성도 또한 변화를 하게 되는데, 저전압 신호처리에 SIT를 응용할 때에는 기생저항을 최소화하기 위해서 드리프트 영역을 작게 디자인하고, 고내압 소자에 응용을 하기위해서는 넓은 드리프트 영역을 가져야 한다.

순방향 블로킹 모드에서 드레인 전압을 계속 증가 를 시키게 되면, 게이트 접합 공핍 영역까지도 영향 을 주게 되어 공핍 영역이 게이트 접합에서 드레인 방향으로 확장되어 진다. 그래서 드리프트 영역의 도 핑농도와 두께는 반드시 드레인-게이트 전압에 의한 영향을 고려하여 설계되어져야 한다. 그 이유는 드레 인-게이트 전압은 게이트 pn 접합을 지나는 총 역바 이어스를 결정하기 때문이다. 공핍 영역의 계속적인 확장으로 인해 핀치-오프에 도달하게 되고, 핀치-오 프 이후에도 공핍영역이 확장되어, 결국 공핍영역이 겹쳐지면서 그 부분에 전위장벽이 형성된다. 전위장 벽의 형성으로 인해 드레인과 소오스 사이에서 흐르 는 전자들은 이 장벽을 따고 오르는 현상이 발생하게 되고, 이 상태에서 드레인 전압을 증가시키면 전위장 벽의 높이가 낮아지는 SI(Static Induction)현상이 발 생하여 전자들은 보다 쉽게 통과를 할 수 있게 된다. 이때의 드레인 전압은 전위장벽을 통과하면서 흐르는 전류를 만들고, 결국 SIT의 최대 블로킹 전압 능력을 결정짓는다. 이를 통해서 블로킹 특성을 개선시키는 방안은 드리프트 영역의 너비, 길이, 도핑레벨과 채널 영역의 길이, 너비의 변화를 통한 전위장벽의 높이를 높이는 방법을 통해 개선 할 수 있다. 드리프트 영역 이 길수록, 또는 넓을수록 보다 높은 블로킹 특성을 얻을 수 있고, 드리프트 영역의 도핑농도를 낮출수록 개선된 블로킹 특성을 얻을 수 있다. 또한, 채널 영역 의 길이가 길수록, 그리고 너비가 넒을수록 보다 향 상된 블로킹 특성을 얻을 수 있다.

#### 2 ZnO SIT의 파라미터 및 전기적 특성

#### 표1. 모델링을 위한 설계 및 공정 파라미터

Table 1. Design and process parameter for Modeling

| Parameter | Channel<br>thickness | Channel<br>doping    | N+ layer<br>thickness | N+ layer<br>doping   |

|-----------|----------------------|----------------------|-----------------------|----------------------|

| Value     | 3um                  | 1e17cm <sup>-3</sup> | 0.2um                 | 1e19cm <sup>-3</sup> |

| Parameter | Source half<br>width | 2.10  | Distance<br>Source-gate | Distance<br>Drain-gate |

|-----------|----------------------|-------|-------------------------|------------------------|

| Value     | 0.3um                | 1,5um | 0,6um                   | 2.4                    |

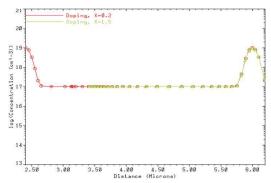

그림1. 소자의 도핑 프로파일

Fig. 1 The doping profiel of ZnO SIT

표1은 소자의 설계 및 공정파라미터를 나타내고 있다. 제안한 구조는 트렌치 구조를 갖고 있고, 게이트 전극은 쇼트키 접촉으로 모델링을 했다. 내압에 중요한 영향을 미치는 채널의 두께는 3um이고, 도핑농도는 1e17cm<sup>-3</sup>으로 모델링을 수행했다. 나머지 설계파라미터는 표에서 나타낸바와 같다.

그리고 그림 5는 게이트전압을 인가할 때 공핍층의 변화를 보여주고 있다. SIT는 normally on 소자이므로 게이트전압을 0V를 인가해도 턴 온이 된다. 점차적으로 게이트에 음의 전압을 인가하면 공핍증이 증가하면서 핀치오프가 일어나게 되어 전류가 포화되어진다. 모델링한 소자에 있어서, 게이트전압을 0V에서 -40를 인가하여 공핍층이 점진적으로 늘어나는 것을 볼 수 있다.

그림5. 게이트전압에 따른 공핍층의 변화

(a) Vg = -10V (b) Vg = -40V

Fig. 5 Variation of depletion layer according to gate voltage

# (a) Vg=-10V (b) Vg=-40V

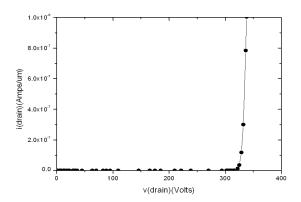

그림 6은 항복전압 시뮬레이션 결과를 보여주고 있다. 에피층의 두께가 3um임에도 불구하고 340V의 내압특성을 보여주고 있다. 게이트 전압은 -30V를 가해주어 턴 오프상태에서 드레인과 소오스 전압을 점진적으로 증가시켜 특성을 평가하였다. 에피층의 두께가 10um정도 증가한다면 내압은 1000V이상의 높은

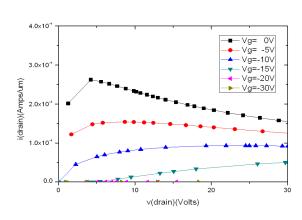

내압을 유지할 수 있을 것으로 판단된다. 그리고 그림 7은 제안한 ZnO SIT 소자의 I-V 특성을 보여주고 있는데, 정상적으로 트랜지스터 특성을 나타내고 있음을 알 수 있다.

## 그림 6. ZnO 전력 SIT의 항복특성

Fig. 6 Breakdown characteristic of ZnO Power SIT

그림 7. ZnO 전력 SIT의 항복특성

Fig. 7 I-V characteristic of ZnO Power SIT

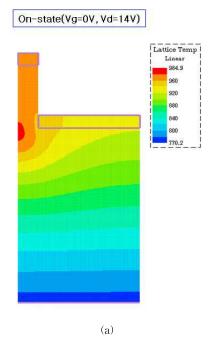

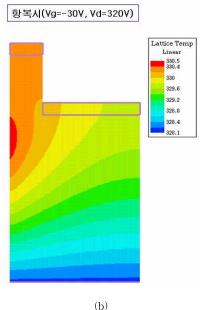

그림 8은 온 상태와 항복시 소자의 열특성을 나타내고 있다. 그림에서 나타낸 것 처럼 온 상태에서는 소오스 바로 밑에 부근에서 높은 열특성을 보이고 있는 반면에 항복시 높은 온도를 갖는 영역이 크게 늘어난 것을 볼 수 있어, ZnO Power SIT 소자도 격자온도가 중가함에 따른 Impact Ionization에 의해 항복이일어남을 알 수 있다.

그림 8. ZnO 전력 SIT 소자의 열 특성 (a) 온상태(b) 항복시

Fig. 8 Thermal Characteristics of ZnO Power SIT (a) on-state (b) breakdown

# Ⅲ 결론

본 논문에서는 차세대 전력반도체인 화합물 반도체소자중 ZnO 전력소자에 대하여 모델링을 수행하였다. 화합물 전력 반도체 소자는 와이드 밴드 갭 소자로서열 특성이 우수해 자동차 및 계통연계형 인버터의 차세대 핵심소자로 인정받고 있다. 모델링 결과 에피두께가 3um, 도핑농도는 1e17cm<sup>-3</sup>일때 내압 340V 정도 얻을 수 있었으며, 관련 I-V특성 등을 평가하였다. 실제 소자로 제작된다면 300V이내의 산업 응용에 충분히 활용할 수 있을 것으로 판단된다.

# 참고문헌

- [1] Y. M, J. I. Nishizawa, T. Ohmi, R. K. Gupta, " Characteristics of Static Induction Transistors: Effects of Series Resistance", IEEE, transactions on electron devices, Vol. ED-25, No. 7, July, 1978

- [2] T. Tamama, M. Sakaue, Y. Mizushima, "Bipolar-Mode Transistors on a Voltage-Controlled Scheme", IEEE, Transactions on electron devices, Vol. ED-28, No. 7, July, 1981

- [3] J. Wang, B. W. Williams, "A New Static Induction Thyristor(SITh) Analytical Model", IEEE Trans. on power Electronics, Vol. 14, No. 5, September, 1999

- [4] H. Tadano, M. Ishiko, S. Kawaji and Y. Taga, " Low Loss Static Induction Devices (Transistors and Thyristors)", Microelectron. Reliab., Vol. 37, No. 9, pp. 1389–1396, 1997

- [5] R. Signh, B. J. Baliga, "Cryogenic Operation of Static Induction (SIT/SITh) devices",

Proceedings of 1995 International Symposium on Power Semiconductor Devices & ICs. Yokohama

## 저 자 소 개

### **강 이 구** (정회원)

1993년 : 고려대학교 전기공학과 졸업 (공학사)

1995년 : 고려대학교 대학원 전기 공학과 (공학석사)

2002년 : 고려대학교 대학원 전기 공학과 (공학박사)

2003년 3월~현재 : 극동대학교

태양광공학과 부교수 <주관심분야> Power Device 및 ICs 분야, 반도체 소자 설계분야

# 정 **헌 석** (비회원)

1991년 : 서울산업대학교 전자계 산학과 졸업 (공학사)

1993년 : 홍익대학교 대학원 전자 계산학과 (이학석사)

1999년 : 홍익대학교 대학원 전자

계산학과 (이학박사)

2003년 3월~현재 : 극동대학교

대양광공학과 부교수 〈주관심분야〉 반도체 및 회로 설계 S/W, 스마트그 리드, 전력 계통 시스템