# 클록 타이밍 조정에 의한 개선된 구조를 가지는 DWA 설계

논 문 59P-4-10

## The DWA Design with Improved Structure by Clock Timing Control

김 동 균\*・신 홍 규\*\*・조 성 익<sup>†</sup> (Dong-Gyun Kim·Hong-Gyu Shin·Seong-Ik Cho)

**Abstract** - In multibit Sigma-Delta Modulator, DWA(Data Weighted Averaging) among the DEM(Dynamic Element Matching) techniques was widely used to get rid of non-linearity that caused by mismatching of unit capacitor in feedback DAC path. this paper proposed the improved DWA architecture by adjusting clock timing of the existing DWA architecture. 2n Register block used for output was replaced with 2n S-R latch block. As a result of this, MOS Tr. can be reduced and extra clock can also be removed. Moreover, two n-bit Register block used to delay n-bit data code is decreased to one n-bit Register. In order to confirm characteristics, DWA for the 3-bit output with the proposed DWA architecture was designed on 0.18um process under 1.8V supply. Compared with the existing architecture, .It was able to reduce the number of 222 MOS Tr.

Key Words: DWA, Dynamic Element Matching, Sigma-Delta Modulator, Multibit

### 1. 서 론

멀티비트 Sigma-Delta Modulator 구조는 DAC 단위요소 커패시터의 부정합에 기인한 비선형성으로 성능을 저하시킨 다. 이를 개선하기 위한 방법으로써 공정에서의 연마 (Trimming) 방법, 제어전압에 의한 전류원 보정방법, 추가 적인 스위칭 커패시터 제어방법, PROM을 이용한 보정방법 등이 있지만 실제 Sigma-Delta Modulator에서 사용하기 위 해서는 추가적인 보정을 하여야 하고 이로 인해 추가적인 비용이 소요되는 문제점이 있다. 그 이외의 방법으로 회로 구현이 쉽고 에러보정과 추가비용이 필요치 않는 DEM (Dynamic Element Matching)이 있다. DEM 기법은 공정상 에서 발생하는 오차 성분에 대하여 DAC의 단위요소 커패시 터들을 재배열함으로써 비선형 잡음을 평균화할 수가 있다 [3]. 이러한 DEM기술은 CLA(Clock Level Averaging), ILA(Individual Level Averaging), DWA(Data Weighted Averaging) 알고리즘 등이 있다.[2,3] 특히 DWA 알고리즘은 피드백 DAC에서 기인된 비이상성을 제거하는 매우 효과적 이고 단순한 방법으로 멀티비트 Sigma-Delta Modulator에 널리 이용되고 있다.[4,5]

본 논문에서는 DEM 기법중 하나인 DWA 을 이용한 멀티비트 Sigma-Delta Modulator 설계 시 DWA 구조를 간략화 할 수 있는 방법을 제안한다. 3-비트 기존구조는 양자화기의 온도계 데이터 코드 출력 값을 저장하기 위해서는 2<sup>n</sup>개의 Resister 블록과 여분의 클록 그리고 지연을 위한 n-

비트 2개의 Register가 요구되어진다. 그러나 제안한 구조는 클록 타이밍을 조정하여 2<sup>n</sup> 개의 S-R Latch 블록을 이용함으로써 여분의 클록을 제거하였고, 또한 2개의 n-비트 Resister 블록으로 감소시켜 구성하는 MOS Tr.를 감소시켰다. 제안한 구조를 이용하여 멀티비트 SC Sigma-Delta Modulator를 구현 시 DWA의 면적 및 전력소모가 감소된다.

본 논문은 구성은 다음과 같다. 2장에서 멀티비트 SC Sigma-Delta Modulator설계 시 기존 DWA 구조에 비하여 개선된 DWA 구조를 제안하였다. 3장에서는 제안된 클록 타이밍 조정에 의한 새로운 구조를 갖는 3-비트 9-레벨 DWA를 Tr. 레벨에서 설계 하였다. 그리고 4장에서는 기존구조와 제안된 구조로 설계된 DWA의 Tr. 개수 및 동작특성에 대하여 시뮬레이션 결과 및 고찰을 하였고, 5장에 결론을 제시하였다.

#### 2. 개선된 DWA 구조

## 2.1 기존의 DWA 구조

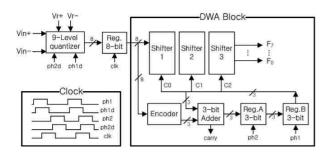

기존의 3-비트 DWA 구조는 그림 1과 같고, DAC의 단위요소 커패시터 값을 재배열 시키는 DWA의 동작원리는다음과 같은 순서로 이루어진다. 모든 데이터 코드는 클록의 상승에지에 동기 된다.

ph1d 신호에 9-레벨 양자화기 블록에서 출력된 데이터 코드는 Shifter 블록에서 DAC 단위요소를 선택하는 DWA의 기능을 수행하기 위하여 clk 신호에 8-비트 Register 블록에서 저장되어 대기하고 있다. 또한 저장된 데이터 코드는 3-비트 덧셈을 위하여 Encoder 블록에서 인코딩되어 있다. 이와 같은 데이터는 이전 ph1 신호에 의하여 3-비트 Register B에 저장되어 있던 데이터 코드 값인 C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>가 출력되어 덧셈이 이루어지며, 동시에 출력된 C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>데이터 코드는 Shifter 블록의 조정신호로 보내져 0~7번의

E-mail: sicho@jbnu.ac.kr

\* 비회원 : 전북대학교 전자정보공학부 석사과정

\*\* 비회원 : 원광대학교 전자 및 제어공학부 교수ㆍ공박

접수일자 : 2010년 10월 14일 최종완료 : 2010년 11월 9일

<sup>↑</sup> 교신저자, 정회원 : 전북대학교 전자공학부 부교수ㆍ공박

그림 1 기존 구조의 DWA 블록 다이어그램

Fig. 1 Conventional DWA bolck diagram

쉬프트 동작을 수행할 수 있게 한다. 그리고 현재 인코딩된데이터 코드와 이전 3-비트 Register B에서 출력된 데이터코드와 덧셈을 수행하기 위하여 ph2 신호에 3-비트Register A에 저장된다. 그러므로 이와 같은 절차에 의하여DWA가 가지는 기능인 DAC의 커패시터 단위요소들을 재배열할 수 있어 DAC 비선형 잡음을 평균화할 수가 있다.

### 2.2 제안한 DWA 구조

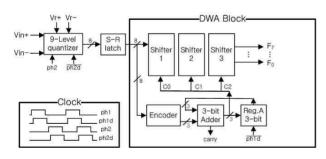

그림 2는 제안한 3-비트 DWA 구조이다. 제안한 구조는 기존구조에서 8-비트 Register 블록에 사용되는 여분의 clk 신호를 제거하기 위하여 8-비트 Register 블록 대신 8-비트 S-R 래치블록을 사용하였다. 이에 따라 9-레벨 양자화기 블록의 clk 신호는 ph2d와 ph2로 변경하였다. 8-비트 Register 블록대신 8-비트 S-R latch 블록으로 변경하면 설계 시 사용되는 MOS Tr.의 개수가 줄게 되어, 집적화 시 면적 감소와 소비전력 감소의 효과가 있다. 또한 기존 구조에서 8-비트 Register 블록에 사용되었던 clk가 제거되면서 DWA 블록의 전체적인 클록 타이밍이 조정된다. 조정된 클록 타이밍으로 부터 2개의 3-비트 Register 블록으로 줄일 수 있으며, 그로 인해 사용되는 MOS Tr.의 개수가 더욱 줄어든다.

그림 2 제안한 구조의 DWA 블록 다이어그램

Fig. 2 Proposed DWA block diagram

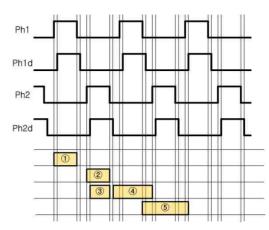

그림 3는 제안된 DWA 구조의 클록 타이밍도 이며, 동작 원리는 다음과 같다.

먼저 구간 ①에서 입력 신호를 샘플링하고 구간 ②에서 적분을 하며, 여기에서 나온 적분기의 출력은 구간③에 양자화기 블록에서 비교되고, 8개의 온도계 코드로 변환되어 출력된다. 출력된 신호는 구간 ④에서 S-R latch 블록을 거쳐 Shifter 블록으로 이동하고, 동시에 8개의 데이터 코드는 Encoder 블록을 거쳐 인코딩 된다. 인코딩된 신호는 이전신호와

그림 3 제안한 구조의 클록 타이밍도

Fig. 3 Proposed DWA clock timing diagram

더해져 Shifter 조정전압인  $C_0$ ,  $C_1$ ,  $C_2$  신호를 만들어 Shifter를 동작시켜 DWA 동작을 수행한다. 만들어진 조정 전압은 구간 ⑤에서 다음 신호와 덧셈을 위해  $\overline{ph1d}$ 에 3-비트 Register A 블록에 저장되어진다.

이렇게 제안한 구조로 설계를 하면 기존의 구조에서 필요했던 여분의 clk를 제거할 수 있으며, 회로와 동작원리를 간략화 할 수 있다.

## 3. 3-비트 DWA 회로설계

그림 2와 같이 3-비트 9-레벨을 가지는 제안된 DWA 구조의 각 블록은 8-비트 S-R Latch, 8×3 Encoder, 3-비트 Adder, 3-비트 Register로 구성된다.

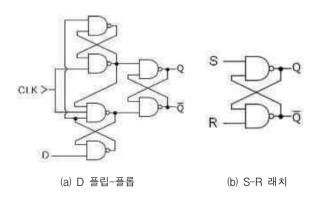

제안된 DWA 구조에서 3-비트 Register 블록으로 사용된 D 플립-플롭은 그림 4(a)와 8-비트 S-R latch 블록에서 사용된 S-R latch는 그림 4(b)와 같다.

그림 4 Register (a) D 플립플롭 (b) S-R 래치 Fig. 4 Register (a) D Flip-Flop (b) S-R latch

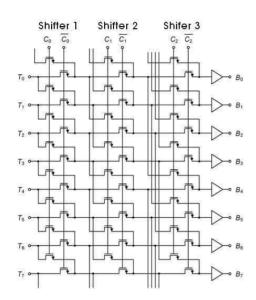

Shifter 블록의 회로는 그림 5와 같으며, 쉬프트 되는 횟수에 따라서 Shifter1, Shifter2, Shfiter3 부분으로 나뉜다. Shifter 설계 시 스위치는 NMOS가 PMOS보다 동작속도가 빠르기 때문에 NMOS로 설계하였고, Shifter 조정신호 데이터인  $C_0$ ,  $C_1$ ,  $C_2$  에 의해  $0\sim7$ 번의 쉬프트를 수행하도록 하였다

**그림 5** 쉬프터

Fig. 5 Shifter

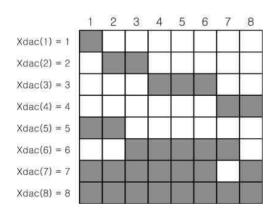

쉬프터의 동작 방법은 다음과 같다. 그림 6과 같이 쉬프 터의 출력은 이전신호의 입력과 더해져 출력의 위치가 결정 되는데 예를 들어 Xdac(3)의 시작 위치인 4와 Xdac(3)의 값 3이 더해져 Xdac(4)의 출력의 시작위치는 7부터 시작된다.

그림 6 시프터 동작

Fig. 6 Shifter operation

DWA 구성요소인 인코더는 입력 8개와 3개의 출력을 갖도록 기본 OR 게이트를 이용하여 설계하였고, Adder는 AND, OR, EX-OR 게이트로 구성된 1-비트 반가산기 및 전가산기를 이용하여 3-비트 Adder를 설계하였다.

#### 4. 시뮬레이션 및 고찰

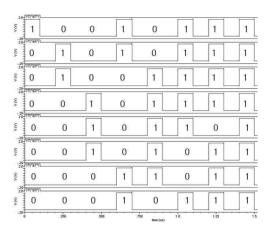

앞 절에서 기술된 DWA 블록들을 적용하여 그림 1의 클록 타이밍을 갖는 기존 DWA를 그림 2와 같은 클록 타이밍을 갖도록 조정하여 3-비트 DWA를 설계하였다. 그림 7은 3-bit DWA의 출력이다. 그림에서와 같이 온도계 코드가 "00000001"에서 "111111111"까지 1씩 증가하는 경우 출력은 이전 코드출력의 다음 위치부터 시작되어 클록 타이밍에 따라

그림 7 분산된 온도계 코드

Fig. 7 The scramble thermometer code

온도계 코드가 분산 출력되는 것을 볼 수 있다. 이와 같이 클록 타이밍을 조정하여 DWA 구조를 단순화하여도 DAC 의 커패시터 단위요소들을 재배열하여 DAC 비선형 잡음을 평균화 시킬 수 있는 기능을 동일하게 할 수 있다.

표 1는 설계된 3-비트 Sigma-Delta Modulator에서 양자화기 온도계 데이터 코드를 처리하는 기존 DWA 구조와 제안한 DWA 구조에 사용된 MOS Tr. 개수를 비교한 결과이다.

표 1 기존 구조와 제안한 구조의 MOS Tr. 개수 비교

Table 1 MOS Tr. number comparison of conventional and proposed architecture.

| proposition and an armonian ar |                   |                   |                   |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 기존 DWA 구조         |                   | 제안한 DWA 구조        |                   |

| bit 수                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-bit             | 4-bit             | 3-bit             | 4-bit             |

| Register A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26 ×<br>8(bit)개   | 26 ×<br>16(bit)개  | X                 | X                 |

| S-R latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X                 | X                 | 8 ×<br>8(bit)개    | 8 ×<br>16(bit)개   |

| Register B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26×3(bit)<br>×2 개 | 26×4(bit)<br>×2 개 | 26×3(bit)<br>×1 개 | 26×4(bit)<br>×1 개 |

| 총 MOS<br>Tr. 개수                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 364 개             | 624 개             | 142 개             | 232 개             |

3-비트를 온도계 데이터 코드를 처리하는 기존 DWA 구조에서 그림4(a)의 8-비트 Register 대신에 그림4(b)의 8-비트 S-R latch로 대체하게 되면 표 1에서와 같이 1-비트 Register당 26개의 MOS Tr.를 필요로 하지만, 1-비트 S-R latch당 8개의 MOS Tr.로 구현이 가능하다. 그러므로 8개의 Register가 8개의 S-R latch로 대체됨으로 144개의 gate가 감소됨을 알 수 있다. 또한 2개로 구성된 3-비트 Resister가 1개의 Register로 감소됨으로써 78개의 MOS Tr.를 줄일 수 있다. 그러므로 기존 구조에서 제안한 구조로 3-비트 DWA회로를 구현할 경우 222개의 MOS Tr. 가 줄어든다

## 5. 결 론

본 논문는 멀티비트 Sigma-Delta Modulator에서 DAC 비선형을 제거하기 위하여 널리 적용되는 DEM 기법중의하나인 DWA 구조를 클릭 타이밍을 변경하여 개선된 DWA

구조를 제안하였다. 그림 2의 3-비트 출력을 가지는 개선된 DWA 구조와 그림 1의 기존 구조를 이용하여 3장에서 기술한 방법으로 Tr. 레벨에서 설계하여 Tr. 개수를 표 1와 같이 비교 분석하였다. 또한 출력 비트수의 증가에 따른 Tr. 개수의 감소됨을 예측하기 위하여 4-비트인 경우도 설계하여 비교한 결과 출력 비트수가 증가할 수록 Tr. 개수가 감소됨을 알 수 있었다.

그러므로 본 논문에서 제시한 개선된 DWA 구조를 이용하여 멀티비트 Sigma-Delta Modulator 설계할 경우 회로의 단순성, 면적, 전력감소에도 크게 기여할 것으로 사료된다.

## 감사의 글

"이 논문은 2009년 원광대학교 교비지원에 의해 수행됨"

#### 참 고 문 헌

- [1] R. K. O. J. A. P. Nys, "Dynamic Element Matching Techniques with Arbitrary Noise Shaping Function," in Proc. ISCAS 96, Atlanta, vol. 1. pp. 293–296, May 1996.

- [2] Fogleman and Ian Galton, "A Dynamic Element Matching Technique for Reduced- Distortion Multibit Quantization in Delta- Sigma ADCs," IEEE Tr.ansactions on Circuit and Systems, vol. 48, no. 2, pp.158-170, Feb. 2001.

- [3] E. Radke, A. Eshraghi, and T. S. Feiz, "A 14-bit current-mode  $\Delta\Sigma DAC$  based upon rotated dat weighted averaging," IEEE J. Solid-State Circuits, vol. 35, pp.1074-1084, Aug. 2000.

- [4] A. A. Hamoui and K. Martin, "Linearity enhancement of multibit  $\Sigma$ - $\Delta$  modulator using pseudo data-weighted averaging," in Proc. IEEE ISCAS, pp. III 285-288, May 2002.

- [5] Y. Greets, M. Steyaert, and W. Sansen, "A High-Performance Multibit ΔΣ CMOS ADC, " IEEE J. Solid-Stata Circuits, vol. SC-35, pp. 1829-1840, Dec. 2000.

- [6] M. Miller et al., "A Multibit Sigma-Delta AD for Multimode Receivers," IEEE J. Solid-State Circuits, vol. 38, pp.475-482, Mar. 2003.

- [7] 김선홍, 최석우, 조성익, 김동용, "Data Weighted Averaging 을 이용한 3차 멀티비트 Sigma-Delta 변조기," 전자공학회논문지, 제41권, 제9호, 107-114쪽, 2004.

- [8] A. A. Hamoui and K. Martin, "High-order multi-bit modulators and pseudo data-weighted averaging in low-oversampling  $\Delta\Sigma$  ADCs for broad-band application," IEEE T. Circuits and Systems, vol.51, pp. 72–85, Jan. 2004.

## 저 자 소 개

## 김 동 균 (金 洞 均)

2009년 원광대학교 전기전자및정보공학 부 졸업. 2009년~현재 전북대학교 전자 정보공학부 석사과정.

주관심분야: 저전력/고성능 A/D Converter E-mail: daum@jbnu.ac.kr

## 신 홍 규 (辛 烘 圭)

1975년 전북대학교 전기공학과 학사 졸업. 1989년 전북대학교 전기공학과 석사졸업. 1982년 ~ 현재 원광대학교 전자및제어공학부 교수.

주관심분야: Active Filter, Low-voltage Low-power analog circuit

E-mail: hongkyu@wku.ac.kr

## 조 성 익 (趙 成 翊)

1987년 전북대학교 전기공학과 학사 졸업. 1989년 전북대학교 전기공학과 석사졸업. 1994년 전북대학교 전기공학과 박사 졸업. 1996년~2004년 Hynix 반도체메모리 연구소 책임연구원. 2004년~현재전북대학교 전자공학부 부교수.

주관심분야: 저전압/고속 Graphic DRAM, Low-voltage Low-power analog circuit, High speed data Interface circuit, ADC/DAC, Filter, PLL/DLL

E-mail: sicho@jbnu.ac.kr