# 2009 전력전자학술대회 우수추천논문

# 2단 AC/DC 컨버터의 링크 캐패시터 전류 스트레스 저감 기법

張斗熙<sup>\*</sup>, 丁永振<sup>\*</sup>, 盧政煜<sup>\*\*</sup>, 洪成洙<sup>\*\*</sup>, 韓翔圭<sup>†</sup>

The RMS Current Stress Reduction Technique in Link Capacitor of Two-stage AC/DC Converter

Doo-Hee Jang, Young-Jin Jung, Chung-Wook Roh, Sung-Soo Hong, and Sang-Kyoo Han

요 약

본 논문에서는 PFC단 링크 캐패시터의 실효 전류를 크게 저감 할 수 있는 링크 캐패시터 전류 스트레스 저감기법을 제안한다. 링크 캐패시터 선정 기준에는 여러 가지가 있으나 가장 큰 비중을 차지하는 것이 캐패시터 실효전류이다. 제안된 C-L 필터는 PFC단 출력 전류를 필터링하여 링크 캐패시터의 실효 전류를 크게 줄일 수 있고, 제안된 C-L-L-C 필터는 C-L 필터의 출력 전류 필터링 효과와 함께 L-C 필터가 DC/DC단 입력 전류를 필터링 함으로써 링크 캐패시터의 실효 전류를 더욱 크게 줄일 수 있다. 제안된 필터는 설계가 간단하고 PFC단의 Crossover frequency가 매우 낮아 C-L 필터 및 C-L-L-C 필터의 Cut-off frequency가 PFC단의 제어기 루프에 영향을 주지않으므로 적은 소자를 가지고 손쉬운 방법으로 링크 캐패시터의 실효전류를 크게 줄일 수 있다. 제안된 필터의 이론적 해석과 설계 방법을 제시하며, 실험을 통하여 그 우수성을 검증한다.

# **ABSTRACT**

The RMS(Root Mean Square) current stress reduction technique for the PFC link capacitor is proposed. Although the various parameter is exist for optimizing the link capacitor, the RMS current stress is the most weighty practical parameter. The proposed C-L filter can reduce effectively the RMS current stress by filtering the output current. And with the C-L-L-C filter proposed in this paper, the more RMS current stress can be reduce because it filters not only the output current, like C-L filter, but also the input current of DC/DC stage. The proposed filter is simple to design and have no effect on the control part of the PFC because of the very low crossover frequency. To confirm the validity of proposed filter, theoretical analysis, the design guide, verification of experimental results are presented.

Key Words: Two-stage, AC/DC converter, Filter, Current stress

1. 서 론

E-mail : djhan@kookmin.ac.kr

접수일자: 2009. 8. 18 1차 심사: 2009. 9. 15

심사완료 : 2009. 9.28

최근의 디스플레이 장치나 컴퓨터와 같은 소비자 전자기기에 적용되는 전원회로는 IEC 61000-3-2와 같은역률규제 및 고조파 규제를 만족하기 위하여 교류의입력전압과 입력전류의 위상을 일치시키는 능동형 역

<sup>&</sup>lt;sup>†</sup>교신저자 : 정회원, 국민대 전자정보통신공학부 조교수

<sup>\*</sup>학생회원, 국민대 전자공학과 박사과정 "정회원, 국민대 전자정보통신공학부 부교수

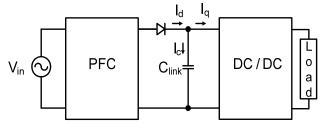

- (a) PFC단, DC/DC단의 주파수 동기화 기법 블록도

- (a) The block diagram of the frequency synchronization technique for PFC and DC/DC converter

- (b) 동기 시 각부 전류 파형

- (b) The current waveform at frequency synchronization

그림 1 PFC단, DC/DC단의 주파수 동기화 기법

Fig. 1 The frequency synchronization technique for PFC and DC/DC converter

률개선 회로와 절연 규격을 만족하면서도 시스템 구동 에 요구되는 DC전압 생성을 위한 절연형 DC/DC 컨 버터를 사용한 2단 AC/DC 컨버터가 많이 사용되고 있다. 이러한 2단 AC/DC 컨버터는 높은 역률, 낮은 고조파 왜곡 및 DC/DC 컨버터의 최적 설계 등 많은 장점들을 가지고 있으나, PFC단 링크 캐패시터의 큰 전류 스트레스로 인하여 큰 전류 용량을 가지는 고가 의 캐패시터를 사용해야하는 단점을 지닌다. 또한 고 가의 캐패시터를 사용함으로써 전류 스트레스에 대한 마진을 크게 가지기 어려우므로 높은 제품 신뢰성확보 가 어려운 단점을 지닌다.

최근에는 이러한 문제점을 해결하기 위하여 그림 1(a)와 같이 PFC단과 DC/DC단의 주파수를 동기 하는 주파수 동기화 기법이 제안되었다. 제안된 방법은 그 림 1 (b)와 같이 PFC단의 스위치가 OFF될 때에 DC/DC단의 스위치를 동작함으로써, PFC단의 출력전 류가 PFC단 출력 캐패시터를 거치지 않고 DC/DC단 의 입력 전류로 흐르게 함으로써 PFC단 링크 캐패시 터의 실효전류를 줄일 수 있다. 그러나 PFC단 DC/DC 단의 주파수를 동기 하는 주파수 동기화 기법은 회로

구동방식이 매우 복잡하고, DC/DC단이 LLC Converter와 같은 주파수 가변 방식인 경우 링크 캐패 시터의 전류스트레스 저감 효과가 크지 않으므로 제품 상용화가 매우 어려운 단점을 지닌다.

따라서 본 논문에서는 간단한 방법으로 링크 캐패시 터의 전류 스트레스를 크게 줄일 수 있는 C-L 필터 및 C-L-L-C 필터를 제안한다. 제안된 C-L 필터는 PFC단 출력 전류를 필터링하여 링크 캐패시터의 실효 전류를 크게 줄일 수 있고, 제안된 C-L-L-C 필터는 C-L 필터의 출력 전류 필터링 효과와 함께 L-C 필터 가 DC/DC단 입력 전류를 필터링 함으로써 링크 캐패 시터의 실효 전류를 더욱 크게 줄일 수 있다. 제안된 필터는 설계가 간단하고 작은 크기의 바 초크 인덕터 및 필름 캐패시터를 사용하므로 PCB 크기가 크게 증 가하지 않는 장점을 지닌다. 제안된 필터의 이론적 해 석과 설계 방법을 제시하며, 실험을 통하여 그 우수성 을 검증한다.

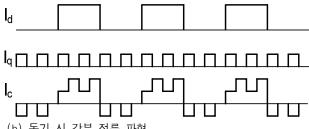

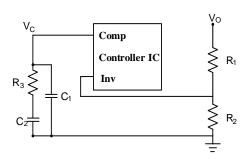

# 2. 제안 필터 기술

본 논문에서는 C-L 및 C-L-L-C 필터를 사용하여 PFC단 링크 캐패시터의 실효전류를 저감하는 링크 캐 패시터 전류 스트레스 저감 기법을 제안한다. 제안된 C-L 필터는 그림 2와 같이 링크 캐패시터 앞에 C<sub>1</sub>과 L<sub>1</sub>이 위치하여 PFC 출력 전류를 필터링함으로써 링크 캐패시터의 전류 스트레스를 저감한다.

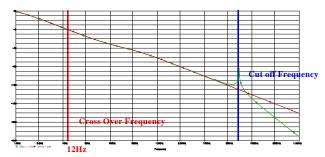

추가적인 링크 캐패시터의 전류 스트레스 저감을 위 한 C-L-L-C 필터 또한 그림 2와 같이 C<sub>1</sub>-L<sub>1</sub>필터 뒤 에 L2와 C2를 추가로 삽입하여 DC/DC단의 입력 전류 를 필터링함으로써 링크 캐패시터의 전류 스트레스를 크게 저감할 수 있다. 제안 필터는 설계가 간단하고 PFC단의 Crossover frequency가 매우 낮아 C-L 필터 의 Cut-off frequency가 PFC 단의 제어기 루프에 영 향을 주지 않으므로 적은 소자를 가지고 손쉬운 방법 으로 링크 캐패시터 실효전류를 크게 저감할 수 있다.

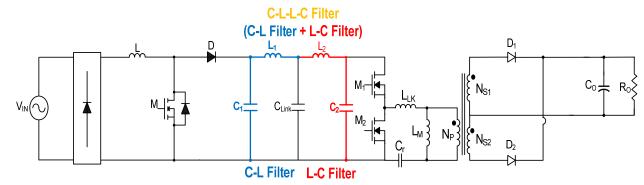

그림 3은 일반적으로 설계되는 PFC단의 Current control loop bode plot과 Voltage control loop bode plot을 나타낸 것이다. PFC 단의 Current Control Loop의 Crossover frequency는 스위칭 주파수의 1/10 로 설정을 하고, Voltage Control Loop의 경우에는 Crossover Frequency를 10~30Hz로 설정을 하여 C-L 필터의 Cut-off frequency는 스위칭 주파수에 있으므 로 PFC단의 제어기 성능에 영향을 주지 않는 것을 확 인할 수 있다.

그림 2 C-L-L-C 필터가 적용된 2단 AC/DC 컨버터

Fig. 2 The two-stage AC/DC converter adopted C-L-L-C filter

그림 3 일반적인 PFC단의 Bode Plot

Fig. 3 The Bode plot of conventional PFC stage

# 2.1 C-L 필터 설계

C-L 필터의 설계 방안은 다음과 같다. C1 캐패시터 선정 기준은 C1 캐패시터와 PFC단 인덕터의 공진이 PFC단의 스위칭 주파수에 영향을 미치지 않아야 하므 로 C<sub>1</sub> 캐패시터는 식 (1)과 같은 관계를 가진다.

$$f_{sw} > \frac{1}{2\pi\sqrt{L \times C_1}} f_{sw} > \frac{1}{2\pi\sqrt{L \times C_1}}$$

(1)

또한 C-L 필터의 Cut Off Frequency는 PFC 단의 스위칭 리플을 필터링 해야 하므로 C-L 필터의 C<sub>1</sub>과 L<sub>1</sub>은 식 (2)의 관계를 갖는다.

$$f_{sw} > \frac{1}{2\pi\sqrt{L_1 \times C_1}} \tag{2}$$

식 (1)을 계산하면 식 (3)과 같이 C<sub>1</sub> 캐패시터를 선 정 할 수 있다.

$$C_1 > \frac{1}{4 \times \pi^2 \times L \times f_{sw}^2} \tag{3}$$

또한 식(2)를 계산하면 식(4)와 같이  $L_1$  인덕터를 선정 할 수 있다.

$$L_1 > \frac{1}{4 \times \pi^2 \times C_{1 \times f_{sw}^2}} \tag{4}$$

#### 2.2. C-L-L-C 필터 설계

링크 캐패시터의 추가적인 전류스트레스 저감을 위하 여 L-C 필터를 추가적으로 삽입할 경우 설계 방법은 다음과 같다. 앞서 설계한 식 (3), (4)를 이용하여 C-L 필터의 설계가 가능하고, 추가적인 L-C 필터의 L2 인 덕터 및 C2 캐패시터는 앞선 C-L 필터와 마찬가지로 Cut-off Frequency가 DC/DC단의 스위칭 주파수보다 작아야 하므로 식(5)의 관계를 갖는다.

$$f_{sw} > \frac{1}{2\pi\sqrt{L_2 \times C_2}} \tag{5}$$

또한 C2가 C2보다 작을 경우 LLC Converter의 LLK 와 공진 하여 LLC Converter의 공진에 영향을 미칠 수 있으므로 C>Cc의 조건을 반드시 추가하여 설계 한다.

## 3. 제안 필터 검증

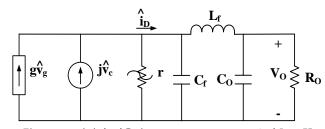

제안된 필터가 PFC단 및 DC/DC단의 제어기 루프에 영항을 미치는지를 확인하기 위하여 PFC단은 Small signal Model을 이용하여 제어기 루프 영향을 검증 하였 고 DC/DC단의 경우에는 네트워크 아날라이저인 PSM 1700을 사용하여 제어기 루프 영향을 검증 하였다.

그림 4 PFC CCM Boost Converter 소신호 모델

Fig. 4 Small signal model of PFC CCM Boost converter

표 1 소신호 모델 파라미터 Table 1 small signal model parameter

| 소 신호 모델 파라미터 |                                                      |

|--------------|------------------------------------------------------|

| g            | $\eta \frac{K V_g (V - V_g)}{2 R_s V} \frac{V_g}{V}$ |

| j            | $\eta \frac{K V_c (V - V_g)}{2 R_s V}$               |

| r            | $-\frac{I_{D}}{V}$                                   |

그림 5 PFC단의 제어기 모델

Fig. 5 Controller model of PFC stage

그림 6 C-L 필터가 적용된 PFC Boost Converter 소신호 모델 Fig. 6 Small signal model of PFC Boost Converter adopted

Fig. 6 Small signal model of PFC Boost Converter adopted C-L filter

그림 7 소신호 모델 주파수 응답 비교

Fig. 7 The frequency response comparison of small signal model

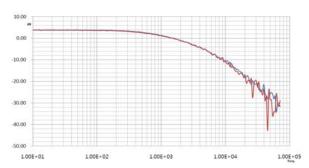

그림 8 LLC Converter 주파수 응답 비교

Fig. 8 The frequency response comparison of the LLC converter

# 3.1 PFC 제어기 루프 영향 검증

PFC단의 제어기 루프 영향을 미치는 지를 판단하기 위하여 그림4와 같이 PFC단을 Small signal model을 이용하여 필터가 있는 경우와 필터가 없는 경우를 비교 하였다. 그림 4는 PFC CCM Boost Converter의 소신호 모델이고, 소신호 모델 파라미터는 표1에 나타내었다. 그림 5는 PFC단의 제어기를 나타낸 것이고 입출력 관계식은 다음과 같다.

$$H(s) = \frac{\stackrel{\wedge}{V_C}}{V_O} = \frac{-1}{R_1} \frac{sC_2R_3 + 1}{s(sC_1C_2R_3 + C_1 + C_2)}$$

(6)

그림 4의 소신호 모델과 그림 5의 제어기 모델을 이용하여 Boost Converter의 제어기 루프 이득을 구하여 보면 다음과 같다.

$$T(s) = G(s) \cdot H(s)$$

$$= \eta \frac{KV_g^2(V_o - V_g)}{2R_1R_sV_o^2} \cdot \frac{sC_2R_3 + 1}{s(sC_1C_2R_3 + C_1 + C_2)} \cdot \frac{R_o}{1 + sC_oR_o}$$

(7)

또한 C-L필터를 적용한 경우에는 그림 6의 소신호 모델로 나타낼 수 있고 제어기 루프 이득을 구하여 보 면 다음과 같다.

$T(s)=G(s)\cdot H(s)$

$$= \eta \frac{KV_g^2(V-V_g)}{2RR_y^2} \cdot \frac{sCR_0+1}{s(sCCR_0+G+C)} \cdot \frac{R_0}{s^2L_fC_fC_RO_0+s^2L_fC_f+sR_0(C_f+C_O)+1}$$

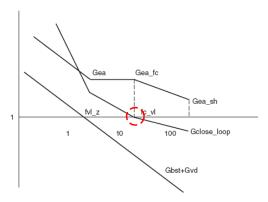

식 (7)과 식 (8)을 이용하여 주파수 응답을 비교한 것을 그림 7에 나타내었다. 그림 7은 필터를 적용하지 않은 경우와 필터를 적용한 경우의 주파수 응답을 나타낸 것이다. 주파수는 1Hz부터 1MHz까지의 주파수 응답을 비교 하였다. 그 결과 필터를 적용하지 않은 경우와 필터를 적용한 경우 모두 Cross-over frequency는 약 12Hz에 있는 것을 확인 하였고, 제안된 필터의 Cut off frequency는 스위칭 주파수에 있으므로 제어기성능에 영향을 주지 않음을 확인 할 수 있다.

그림 8은 LLC resonant converter의 L-C 필터를 적용한 경우와 필터를 적용하지 않은 경우의 주파수 응답을 측정한 결과이다. 측정은 네트워크 아날라이저인 PSM 1700을 이용하여 측정을 진행 하였고, 측정 주파수는 1Hz에서 100kHz까지 측정 하였다. 그 결과 측정주파수 전 영역에서 필터를 추가하여도 주파수 응답은 바뀌지 않음을 확인 할 수 있다. 이는 L-C필터의 C2 캐패시터는 DC/DC단의 전력 단에서 전압 원으로 모델링 할 수 있으므로 필터에 의한 제어기 성능에 영향을주지 않음을 확인할 수 있다.

## 4. 실험 및 결과

제안된 C-L 필터 및 C-L-L-C 필터를 2단 AC/DC 컨버터에 적용하여 동작을 확인 하였다. 설계된 회로에 사용된 소자와 설계 사양은 다음과 같다.

### PFC 단

- -BCM PFC Boost Converter

- -V<sub>in</sub>=90~264Vac\_rms, V<sub>O</sub>=385Vdc, P<sub>O</sub>=200W

- $-f_{s\_min}$ =100kHz,

- -L= 200uH,  $C_{link}$ = 150uF

- -M= FQPF10N60(600V/11A), D= FSU10U60 (600V/10A)

DC/DC 단

- -LLC Resonant Converter

- $-V_0=24Vdc$ ,  $I_0=8.33W$ ,  $P_0=200W$

- $-f_{s\_min}$ = 95kHz,

- $-L_M$ = 500uH,  $L_{LK}$ = 90uH,  $C_r$ = 22nF, Turns ratio= 35:4  $-M_1,M_2$  =2SK3561 (600V/9A),  $D_1,D_2$ =FCH20U10 (100V/20A)

제안 필터

- $-C_1 = 510 \text{nF}, L_1 = 8.8 \text{uH}$

- $-C_1$ = 510nF,  $L_1$ = 8.8uH,  $C_2$ = 1uF,  $L_2$ = 3.3uH

#### 4.1 링크 캐패시터 전류 스트레스 비교

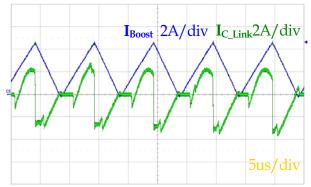

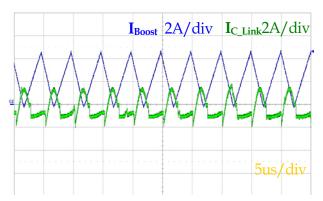

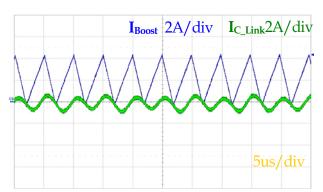

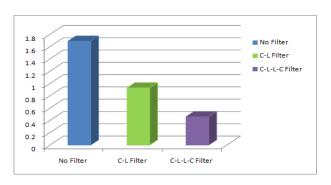

실험은 2단 AC/ DC컨버터를 200W에서 동작하도록 제작하였고, 필터가 없는 경우 및 C-L 필터를 적용한 경우 그리고 C-L-L-C 필터를 적용한 경우 총 3가지로 나누어 실험을 실시 하였다. 그 결과 PFC단의 필터가 적용되지 않은 경우에는 그림 9 (a)와 같이 링크 캐패시터 실효전류는 1.69A로 나타났다. 그러나 제안된 C-L 필터 ( $C_1$ =510nF,  $L_1$ =8.8uH)가 추가된 경우에는 그림 9 (b)와 같이 링크 캐패시터의 실효 전류는 0.93A로 나타났고, 추가적인 링크 캐패시터의 설효 전류 스트레스 저 감을 위한 C-L-L-C 필터 ( $C_1$ =510nF,  $L_1$ =8.8uH,  $C_2$ =1uF,  $L_2$ =3.3uH)를 적용한 경우에는 그림 9 (C)와 같이 링크 캐패시터의 실효전류는 0.46A로 나타났다.

그림 10은 기존 및 제안 필터의 링크 캐패시터 실효전류 실험결과를 비교한 그래프이다. C-L 필터를 적용하였을 경우에는 기존 필터가 없는 구조 대비 약 43%의 링크 캐패시터 실효전류 감소가 이루어 졌고, 이는 C-L 필터가 PFC 단의 스위칭 리플을 필터링 함으로써링크 캐패시터의 전류 스트레스를 저감한 결과이다. 또한 C-L-L-C 필터를 적용하였을 경우에는 기존 필터가없는 구조 대비 약 72.8%의 링크 캐패시터 실효전류저감을 확인할 수 있다. 이는 C-L 필터가 PFC단의 스위칭 리플을 퍼러함과 동시에 L-C필터가 DC/DC단의입력 전류를 필터링함으로써 링크 캐패시터의 전류 스트레스를 크게 저감한 결과이다.

# 4.2 기존 및 제안 필터 동작 특성 비교

앞선 4.1 장에서는 제안 필터를 이용하여 링크 캐패시터 전류 스트레스를 저감하여 기존의 82uF의 캐패시터 2개를 제안 필터를 적용하여 47uF 캐패시터 1개만으로 전류 스트레스를 만족할 것으로 판단 하였다. 따라서 본 논문에서는 제안필터를 적용하여 링크 캐패시

- (a) 인덕터 전류 및 링크 캐패시터 전류 파형

- (a) The current waveform of the inductor and the link capacitor

- (b) C-L 필터가 추가된 인덕터 전류 및 링크 캐패시터 전류 파형

- (b) The current waveform of the inductor and the link capacitor with the C-L filter

- (c) C-L-L-C 필터 추가된 구조의 인덕터 전류 및 링크 캐패 시터 전류 파형

- (c) The current waveform of the inductor and the link capacitor with the C-L-L-C filter

- 그림 9 기존 및 제안 필터 실험 파형 비교

- Fig. 9 The comparison of the conventional and the proposed filter experimental waveform

그림 10 기존 및 제안 필터 적용 시 실효전류 비교 그래프 Fig. 10 The graph of comparison between the conventional

rms currents and rms currents with the proposed filter

터를 감소하고 기존의 2단 AC/DC 컨버터와 동적 특성을 비교 하였다. 실험은 크게 2가지로 Full Load 조건에서 전압리플을 비교 하였고, 부하 변동시 정착시간을 비교 하였다.

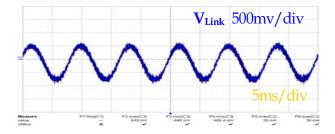

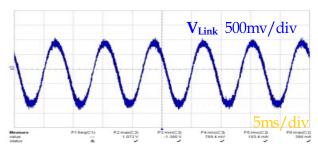

첫 번째 전압 리플을 측정한 경우, 기존의 컨버터는 그림 11과 같이 Full Load 조건에서 약  $466\text{mV}(C_{\text{link}}=164\text{uF})$ 인 것으로 나타났다. 그러나 제안 필터를 적용하여 링크 캐패시터를 47uF으로 감소한 경우에는 그림 12와 같이 789mV인 것으로 나타났다. 제 안필터를 사용한 경우에는 기존의 링크 캐패시터를 사용한 경우 보다 323mV 증가하였지만, 링크 캐패시터 뒤에 DC/DC단이 존재 하므로 컨버터 동작의 큰 문제는 되지 않을 것으로 판단한다.

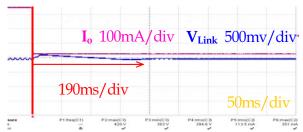

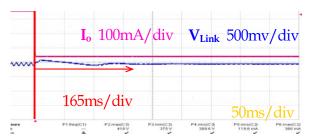

두 번째 컨버터를 최대 부하 조건에서 동작하였다가 10%부하로 동작 할 경우 정착시간을 비교 하였다. 기존의 경우에는 그림 13과 같이 정착시간이 약 190ms인 것으로 나타났지만, 제안 필터를 적용한 경우에는 그림 14와 같이 정착시간이 165ms로 나타났다. 이는 기존대비 약 25ms 개선된 것을 확인 할 수 있다.

그림 11 기존 컨버터 링크 캐패시터 전압 파형

Fig. 11 The link capacitor voltage waveform of the conventional boost converter

그림 12 C-L-L-C 필터 적용 시 링크 캐패시터 전압 파형 Fig. 12 The link capacitor voltage waveform with C-L-L-C filter

그림 13 기존 컨버터 정착 시간 측정

Fig. 13 The the settling time measurement of the conventional converter

그림 14 C-L-L-C 필터 적용시의 정착 시간 측정 Fig. 14 The the settling time measurement of the proposed C-L-L-C filter adopted

#### 5. 결 론

본 논문에서는 2단 AC/DC 컨버터의 링크 캐패시터 실효 전류 저감 기법에 관하여 제안하였다. 기존의 PFC단과 DC/DC단의 주파수 동기 방법은 실효 전류를 줄일 수 있지만, 회로 및 구동방식이 복잡한 단점을 지니고, DC/DC단이 LLC Converter와 같은 주파수 가변 방식인 경우 그 효과가 크지 않은 단점을 가졌다.

따라서 본 논문에서는 2단 AC/DC 컨버터의 링크 캐 패시터 전류 스트레스를 저감하는 C-L필터 및 C-L-L-C 필터를 제안하였다. 제안된 C-L 필터는 PFC단 출력 전류를 필터링하여 링크 캐패시터의 실효 전류를 크게 줄일 수 있고, 제안된 C-L-L-C 필터는 C-L 필터의 출력 전류 필터링 효과와 함께 L-C 필터가 DC/DC단 입력 전류를 필터링 함으로써 링크 캐패시터의 실효 전류를 더욱 크게 줄일 수 있다. 제안된 필터는 설계가 간단하고 PFC단 Crossover Frequency가 매우 낮아 C-L 필터 및 C-L-L-C 필터의 Cut-off Frequency가 PFC단의 제어기 루프에 영향을 주지 않으므로 적은 소자를 가지고 손쉬운 방법으로 링크 캐패시터의 실효전류를 저감할 수 있다. 제안된 C-L 필터를 2단 AC/DC 컨버터에 적용하였을 경우에는 약 43%의 링크 캐패시터 실효전류 감소효과를 나타내었고, C-L-L-C 필터를 적용하였을 경우에는 약 72.8%의링크 캐패시터 실효전류 감소효과가 나타났다.

또한 제안 필터를 적용하여 컨버터 동적 특성을 비교하였을 경우, 전압리플은 323mV증가하였지만 링크 캐패시터 뒤에 DC/DC단이 존재하므로 큰 문제가 되지 않음을 확인 하였고, 최대 부하 조건에서 무부하로 부하가 변동 하였을 경우에는 제안필터를 적용한 경우가약 25ms 빠른 정착 시간을 가지는 것을 확인 하였다.

따라서 제안된 필터는 기존의 기술들이 가진 단점을 극복 하였고, 설계가 용이하고 적은 소자를 이용하여 링크 캐패시터의 실효전류를 크게 줄일 수 있으므로 링크 캐패시터의 가격 저감이 가능하고, 낮은 전류 스트레스로 인하여 전류 스트레스에 대한 마진을 크게 가질 수 있으므로 높은 제품신뢰성을 확보할 수 있을 것으로 기대한다.

본 연구는 2009년도 국민대학교 교내 연구비 지원과 지식경제부 및 정보통신 연구진흥원의 대학 IT연구센터 지원사업의 연구결과로 수행되었음 (NIPA -2009 -C1090-0904-0002)

### 참 고 문 헌

- [1] IEC 61000-3-2, Limit for harmonic current emissions (equipment input current ≤ 16A per phase), Internal Standard, 1998.

- [2] 정영석, 윤명중 "전력 변환 시스템의 역률개선 기술동향", 전력전자학회 논문지, pp. 30-36, 1997. 3.

- [3] Yonghan Kang, Byungcho Choi "Small-Signal Model for a Controlled On-Time Boost Power Factor Correction Circuit", 전력전자학회 논문지, pp. 642-647,

1998. 10.

- [4] 정영석, 문건우, 이준영, 윤명중, "평균화 모델을 이용한 역률개선 제어기법", 전력전자학회 논문지, pp. 85-88, 1996 6

- [5] O. Garcia et al., "Power factor correction: A survey", in Proc. IEEE PESC, pp. 8-12, 2001, June.

- [6] Jing Sun, B.E., "New Leading/Trailing Edge Modulation Strategies for Two-Stage PFC AC/DC Adapters to Reduce DC-LINK Capacitor Ripple Current", Master thesis, Texas A&M University, 2007, May.

- [7] Abraham I. Pressman, "Switching Power Supply Design", McGraw Hill, pp. 563-609, 1998.

### 저 자 소 개

# 장두희(張斗熙)

1982년 2월 13일생. 2007년 국민대 공과대학 기계자동차공학부 졸업. 2009년 국민대대학원 전자공학과 졸업(석사). 2009년 3월~현재 국민대 전자공학과 박사과정.

### 정영진(丁永振)

1978년 9월 2일생. 2003년 수원대 전기공학과 졸업. 2006년 국민대 전자공학과 졸업(석사). 2008년~현재 국민대 전자공학과박사과정.

### 노정욱(盧政煜)

1971년 9월 10일생. 1993년 한국과학기술 원 전기 및 전자공학과 졸업. 1995년 동 대학원 전기 및 전자공학과 졸업(석사). 2000년 동 대학원 전기 및 전자공학과 졸 업(공박). 2000년~2004년 삼성전자(주) 영

상 디스플레이 사업부 책임연구원. 2004년~현재 국민대 전자 정보통신공학부 부교수, 당 학회 국문지 편집위원.

### 홍성수(洪成洙)

1961년 1월 25일생. 1984년 서울대 전기공학과 졸업. 1986년 한국과학기술원 전기및 전자공학과 졸업(석사). 1992년 동 대학원 전기 및 전자공학과 졸업(공박). 1984년~1999년 현대전자(주) 정보통신 연구소

책임연구원. 1999년~현재 국민대 전자정보통신공학부 부교수.

### <u>한상규(韓翔圭)</u>

1973년 12월 13일생. 1999년 2월 부산대 전기공학과 졸업. 2001년 2월 한국과학기 술원 전자전산학과 졸업(석사). 2005년 2월 동 대학원 전자전산학과 졸업(공박). 2005 년 3월~2005년 8월 한국과학기술원 정보

\_\_\_\_\_ 전자연구소 박사후연구원. 2005년 9월~현재 국민대 전자정보 통신공학부 조교수.