# 글리치 전력소모 감소를 이용한 CPLD 저전력 알고리즘 연구

허화라\*

## A Study of CPLD Low Power Algorithm using Reduce Glitch Power Consumption

Hur, Hwa Ra

#### - <Abstract>

In this paper, we proposed CPLD low power algorithm using reduce glitch power consumption.

Proposed algorithm generated a feasible cluster by circuit partition considering the CLB condition within CPLD. Glitch removal process using delay buffer insertion method for feasible cluster. Also, glitch removal process using same method between feasible clusters.

The proposed method is examined by using benchmarks in SIS, it compared power consumption to a CLB-based CPLD low power technology mapping algorithm for trade-off and a low power circuit design using selective glitch removal method. The experiments results show reduction in the power consumption by 15% comparing with that of and 6% comparing with that of.

Key Words: Low power, Glitch, CLB, CPLD

### Ⅰ. 서론

VLSI(Very Large Scale Integration) 제조 및 설계 기술의 발달과 더불어 최근 휴대용 전자 제품의 수요가 급증함에 따라 회로의 전력 소모를 개선하기 위한 저전력 회로의 설계가 중요한 사양으로 등장하고 있다. 전력을 소모하는 원인들 중에서 가장 많은 비중을 차지하는 것은 캐피시턴스(capacitance)와 충전(charging), 방전(discharging) 과정에서 발생되는 동적 전력(dynamic power)이다[1]. 특히 저전력 회로 설계의 경우 노드의 스

위치 캐패시턴스를 감소시켜 회로의 동적 전력을 줄이는데 중점을 두고 있다[2]. 스위치 캐패시턴스의 수를 줄이기 위한 가장 효율적인 방법으로 노드의 스위칭 동작 (switching activity)을 감소 시켜야 하며, 소비 전력을 줄이기 위한 방법으로 여러 가지 방법들이 제안되고 있다[3-5].

저전력을 위한 논리 회로 설계는 주로 STG(State Transition Graph) 수준과 논리 게이트(logical gate) 및 F/F(Flip/Flop) 수준에서 이루어지고 있다. 그러나 이러한 알고리즘들은 입력 변수만을 제한 조건으로 그래프 분할을 수행함으로써 LUT(Look-Up Table)를 기저로 하

<sup>\*</sup> 송호대학 컴퓨터정보과 부교수

는 FPGA(Field Programmable Gate Array)에 적용 가능 하도록 구성되어 있다[6-9]. 이에 반하여 현재 많이 사용 하고 있는 CLB(Common Logic Block)를 기저로 하는 CPLD(Complexity Programmable Logic Device)의 경우 OR텀수를 고려하여 그래프 분할을 수행하여야 함으로 CPLD에 적용하기에는 어려움이 많다. 기존에 발표된 CPLD 기술 매핑 알고리즘으로는 DDMAP과 TEMPLA, TMCPLD, PLAmap등만이 제안되어 있다[10-14]. 이러한 알고리즘 중에서 저전력과 면적, 시간 등을 고려한 알고 리즘은 TMCPLD나 상관관계(trade-off)에 의한 CLB구조 의 CPLD 저전력 기술 매핑 알고리즘이 있다[15]. 그러나 상관관계(trade-off)에 의한 CLB구조의 CPLD 저전력 기 술 매핑 알고리즘의 경우 저전력의 회로 구현을 제안하 였으나 매핑 가능 클러스터에 글리치를 고려하지 않은 것이 대부분이며 선택적 글리치 제거 방법을 이용한 저 전력 회로 설계만이 글리치 제거 방법을 제안하였으나 글리치 발생 확률에 따라 선택적으로 글리치를 제거하였 으며 매핑 가능 클러스터 사이의 글리치는 고려하지 않 은 단점이 있다[18].

본 논문에서는 이러한 단점을 보완하여 매핑 가능 클 러스터에 대해 지연 버퍼 삽입 방법을 이용하여 글리치 를 제거하고, 글리치가 제거된 매핑 가능클러스터들에 대해 발생될 수 있는 글리치를 제거하여 저전력의 회로 를 구현할 수 있는 방법을 제안하였다.

### Ⅱ. 관련연구

### 2.1 글리치 모델

회로의 한 노드에서의 논리 값이 0 에서 1, 또는 1 에서 0 으로 천이 할 경우에 전력 소모가 발생한다.

CMOS 회로에서의 전력 소모는 직접적인 전력 소모 와 간접적인 전력 소모로 나누어 볼 수 있다. 직접적인 전력 소모는 용량성 부하로의 충전시 발생되는 전력 소 모로서 0에서 1로 신호 천이시 발생된다. 간접적인 전력 소모는 용량성 부하의 방전에 의해 발생되는 전력 소모 로서 1에서 0으로 천이시 발생되는 전력 소모이다.

글리치 신호는 회로의 동작과 무관하게 발생되는 신호로서 생성글리치(generated glitch)와 전파글리치 (propagation glitch)로 나누어진다[16]. 생성글리치는 글리 치가 아닌 입력 신호들의 충돌(collision)로 발생되며 입력 신호에 대해 도착 시간의 차이가 충분히 크며 입력 신호의 패턴이 글리치의 발생 조건을 만족할 경우에 발생된다. 전 파글리치는 게이트의 입력신호에 존재하는 글리치가 게이 트의 출력단까지 전달되어 발생되는 글리치이다. 글리치를 고려한 소모 전력은 식 (1)과 같이 표현된다[17].

$$P = \frac{1}{2} V_{dd}^2 \sum_{n} D(n) \cdot C(n)$$

(1)

D(n): 천이밀도(단위 시간당 글리치를 포함한 신호 천이 횟수)

C(n): 노드 n에서의 용량성 부하 값

### 2,2 매핑가능 클러스터

디지털 회로를 CPLD와 같은 디바이스에 기술 매핑하기 위해서는 CLB(Common Logic Block)와 같이 CPLD를 구성하고 있는 구성 요소에 맞도록 회로를 분할하여야 한다. 이와같이 분할된 회로의 묶음을 매핑가능 클러스터(feasible cluster)라 한다.

매핑 가능 클러스터를 생성하기 위해서는 선택된 CPLD를 구성하고 있는 CLB의 OR 텀수를 알아야 한다. CLB의 OR 텀수는 CLB\_OR로 정의 한다. CLB\_OR를 이용하여 매핑 가능 클러스터를 생성한다. 매핑 가능 클러스터는 노드의 비용을 계산하여 생성하여야 한다. 각각의 노드 비용은 노드가 가지고 있는 OR텀수를 노드 비용으로 정의한다.

클러스터의 전체 비용은  $CST_C$ 로 정의하고 클러스터의 전체비용은 클러스터가 생성될 때 생성되는 OR 이 전체비용은

의 수를 의미한다.  $CST_C$ 의 비용을 계산하는 방법은 식 (2)와 같다.

$$CST_{\textit{C}}(n) \ = \ \left[ \begin{array}{cc} H^n_{p=1}[Child\_Node(p)] & Pre\_Node(k) = 1 \\ \\ \sum_{p=1}^n[Child\_Node(p)] & Pre\_Node(k) > 1 \end{array} \right]$$

$Child\_Node\left(p\right)$  : 계산하고자 하는 노드의 입력 노 드들이 가지고 있는 OR 텀수

### 2.3 기존 알고리즘

본 논문에서 비교 대상으로 하는 알고리즘은 상관관 계에 의한 CLB구조의 CPLD 저전력 기술 매핑 알고리즘 [15]과 선택적 글리치 제거 방법을 이용한 저전력 통신 회로 설계[18]이다.

## 2.3.1 상관관계에 의한 CLB구조의 CPLD 저전력 기술 매핑 알고리즘

상관관계에 의한 CLB구조의 CPLD 저전력 기술 매핑 알고리즘은 주어진 불린 네트워크를 DAG로 구성하여 소모전력 계산을 위한 TD(Transition Density) 계산 단계 와 매핑 가능 클러스터 생성, CLB 패킹의 단계로 구성하 였다. TD 계산 단계는 DAG를 구성하고 있는 각 노드들 에 대한 스위칭 동작을 계산하여 전체 소모 전력을 계산 하는 단계이다. 매핑 가능 클러스터 생성 단계는 주어진 CPLD의 CLB에 대한 입출력의 수와 OR 텀수를 고려하 여 매핑 가능 클러스터를 생성하는 단계이다. 매핑 가능 클러스터를 생성하기 위하여 공통 노드 클러스터 병합과 노드 분할, 노드 복제의 방법을 이용하여 저전력의 회로 를 구현할 수 있는 알고리즘이다.

## 2.3.2 선택적 글리치 제거 방법을 이용한 저전력 통신 회로 설계

선택적 글리치 제거 방법을 이용한 저전력 통신 회로

설계는 불린 네트워크를 DAG로 구성하여 소모 전력 계 산을 위한 TD(Transition Density) 계산 단계와 매핑 가 능 클러스터 생성 단계, 글리치 제거 단계, CLB 패킹의  $CST_C(n) = \left[ egin{array}{ll} I_{p=1}^n[Child\_Node(p)] & Pre\_Node(k) = 1 \\ \sum\limits_{p=1}^n[Child\_Node(p)] & Pre\_Node(k) > 1 \end{array}

ight] ext{ 단계로 구성하였다. 첫 번째 단계는 TD 계산 단계로서 DAG를 구성하고 있는 각 노드들에 대한 스위칭 동작을}$ 계산하여 전체 소모 전력을 계산하는 단계이다. 매핑 가 능 클러스터 생성 단계는 주어진 CPLD의 CLB에 대한 입출력의 수와 OR 텀수를 고려하여 매핑 가능 클러스터 를 생성하는 단계이다. 매핑 가능 클러스터를 생성하기 위하여 공통 노드 클러스터 병합과 노드 분할, 노드 복제 의 방법을 이용한다. 글리치 제거는 매핑 가능 클러스터 들 중에서 TD가 가장 큰 값을 가진 매핑 가능 클러스터 를 대상으로 수행된다. 마지막은 CLB 패킹을 수행하여 저전력의 통신 회로를 설계하는 방법이다.

## Ⅲ. 글리치 전력소모 감소를 이용한 CPLD 저전력 알고리즘

디지털 회로를 구현한 CPLD에 대해 저전력을 수행하 기위해서는 CPLD에 매핑해야할 매핑 가능 클러스터에 대한 저전력 매핑 가능 클러스터로 변환하여야 한다. 저 전력의 매핑가능 클러스터를 생성하기 위해서는 저전력 을 적용해야할 매핑가능 클러스터를 우선 선정하여야 한 다. 선정된 매핑 가능 클러스터에 대해 글리치 제거를 통 해 저전력의 매핑 가능 클러스터를 생성한다.

#### 3.1 매핑 가능 클러스터의 선정

저전력의 매핑 가능 클러스터를 만들기 위한 적용 대상 의 순서는 매핑 가능 클러스터를 구성하고 있는 게이트의 단수가 가장 많은 것을 우선 대상으로 한다. 게이트의 단 수가 가장 많은 것은 매핑 가능 클러스터의 입력에서 출력 까지의 시간이 가장 긴 것을 의미하며 글리치가 발생될 수 있는 가능성이 가장 높다는 것을 의미하기 때문이다.

### 3.2 글리치 제거

글리치 제거 방법에는 게이트 사이징(Gate sizing)과 버퍼 삽입(Buffer insertion)의 방법이 있다[17]. 게이트 사이징 방법은 용량성 부하를 줄이는 방법으로 게이트의 사이즈를 줄이거나 크게하여 글리치를 없애는 방법이다. 버퍼 삽입 방법은 글리치를 생성하는 경로불균형화를 지연버퍼(delay buffer) 삽입의 방법으로 경로균형화(Path balancing)를 이루어 글리치를 제거하는 방법이 있다. 본논문에서는 매핑 가능 클러스터에 대해 저전력을 구현하기 위한 방법으로 버퍼 삽입 방법을 사용한다. 버퍼 삽입 방법은 크게 두 가지로 나누어 실행한다. 첫 번째는 매핑 가능 클러스터를 생성하고 있는 게이트들의 경로 정보를 이용하여 글리치를 제거한다. 두 번째는 글리치가 제거된 매핑 가능 클러스터들의 단수를 계산하여 매핑 가능 클러스터 간에 발생될 수 있는 글리치를 제거하는 방법이다.

#### 3.2.1 매핑 가능 클러스터에 대한 글리치 제거

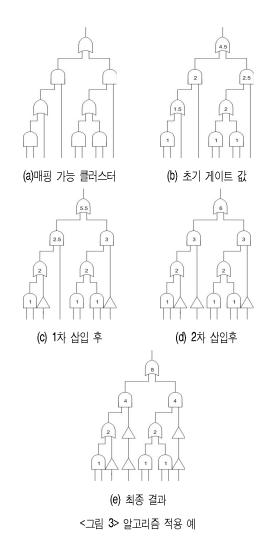

매핑 가능 클러스터에 대해 글리치를 제거하기 위해 매핑 가능 클러스터를 구성하고 있는 게이트와 연결 정보를 이용한다. 매핑 가능 클러스터를 구성하고 있는 게이트는 2입력 1출력의 게이트들로만 구성되어 있다고 가정한다. 매핑 가능 클러스터의 입력을 FC\_Input이라 하며 가중치는 0.5로 한다. 매핑 가능 클러스터의 출력은 FC\_Output으로 정의하며, 매핑 가능 클러스터를 구성하고 있는 게이트는 FC\_Gate로 정의한다. 게이트의 단수는 Gate\_level의 값이 X.5와 같이 소수점 값이 있거나 1을 제외한 홀수의 값인 경우 경로불균형이 되었다고 정의하고 지연버퍼를 삽입하여 글리치를 제거한다. 지연버퍼를 삽입하는 알고리즘은 <그림 1>에, 글리치 제거 알고리즘은 <그림 2>에 나타내었다. 알고리즘의 적용 예는 <그림 3>에 나타내었다.

```

Insert_Delay_Buffer(FC_Gate(), Gate_level())

{

for(n=1; FC_Gate(n); n++)

{

if(Gate_level(n)=decimal)

{

insert_delay_buffer_to_left_input;

}

els

{

insert_delay_buffer_to_right_input;

}

}

elsif(Gate_level(n) \neq 1 && Gate_level(n)=odd)

{

if(left_input>right_input)

{

insert_delay_buffer_to_left_input;

}

els

{

insert_delay_buffer_to_left_input;

}

els

{

insert_delay_buffer_to_right_input;

}

}

}

```

<그림 1> 지연버퍼 삽입 알고리즘

```

Glitch_Removal_in_FC(FC_Input(), FC_Output, FC_Gate())

{

FC_Input()=0.5;

FC_Gate_Input()=null;

//FC_Gate_Input():Input으로만 구성된 게이트 목록

for(l=1; FC_Gate(l); l++)

{

Search a gate having been composed of input only

Gate_level(l)=1;

Save FC_Gate_Input(l)=;

}

Rest_Gate(m)=FC_Gate(m)-FC_Gate_Input(m);

for(n=1; Rest_Gate(n); n++)

{

Insert_Delay_Buffer(Gate_level());

}

for(q=1; FC_Gate(q); q++)

{

```

```

Generate Gate_level(q);

if(Gate_level(q)=odd)

{

Insert_Delay_Buffer(Gate_level());

}

}

```

<그림 2> 글리치 제거 알고리즘

### 3.2.2 매핑 가능 클러스터 사이의 글리치 제거

매핑 가능 클러스터 사이의 글리치를 제거하기 위해 서는 최종 출력(Primary Output)에서 초기 입력(Primary Input)까지의 경로를 검색하여 매핑 가능 클러스터간의 연결 정보와 단수를 파악한다. 매핑 가능 클러스터 간의 글리치를 제거하기 위해서는 경로균형화를 이루어야 한다. 따라서 PO을 가지고 있는 매핑 가능 클러스터에서 PI만으로 구성된 매핑 가능 클러스터 방향인 topdown 방식으로 검색하며 지연 버퍼를 삽입하여 글리치를 제거한다. 매핑 가능 클러스터의 값은 Cost\_FC라 하고, 매핑 가능 클러스터의 출력 게이트가 가진 값으로 한다. <그림 3>의 예제에서 최종 매핑 가능 클러스터의 값은 8이다. 매핑 가능 클러스터 사이의 글리치 제거 알고리즘은 <그림 4>에 나타내었다.

<그림 4> 매핑 가능 클러스터 사이의 글리치 제거 알고리즘

### Ⅳ. 실험 결과

본 논문에서 제안한 방법에 대한 실험으로 상관관계에 의한 CLB구조의 CPLD 저전력 기술 매핑 알고리즘

[15]과 글리치 제거 방법을 이용한 알고리즘[18]과 전력을 비교하였다.

실험에 사용한 예제는 SIS에서 제공되는 MCNC 벤치마크 회로들의 불린 네트워크를 사용하였다.

MCNC 벤치마크 회로들은 조합논리회로와 순서논리 회로가 있으며 그 중에서 11개의 회로를 선정하여 실험 에 사용하였다. 선정된 회로들에 대하여 소모 전력 감소 를 수행한 결과는 표 1에 제시하였다.

| <班 ′ | 1> | 전력 | 비교 |

|------|----|----|----|

|------|----|----|----|

|        | [15] |       | [18] |       | 제안한 알고리즘 |       |

|--------|------|-------|------|-------|----------|-------|

|        | FC   | power | FC   | power | FC       | power |

| alu2   | 57   | 5.2   | 57   | 4.8   | 57       | 4.2   |

| alu4   | 189  | 23.6  | 189  | 19.9  | 189      | 16.7  |

| dalu   | 488  | 27.6  | 488  | 27.4  | 488      | 26.9  |

| ех5р   | 134  | 12.2  | 134  | 11.8  | 134      | 11.9  |

| duke2  | 71   | 7.3   | 71   | 7.3   | 71       | 7.2   |

| t481   | 94   | 21.8  | 94   | 18.6  | 94       | 18.1  |

| cps    | 135  | 26.5  | 135  | 24.2  | 135      | 19.3  |

| apex4  | 129  | 30.5  | 129  | 24.3  | 129      | 23.8  |

| misex3 | 142  | 30 7  | 142  | 29.7  | 142      | 29.7  |

| psdes  | 127  | 28.4  | 127  | 26.3  | 127      | 25.1  |

| sort   | 101  | 22.1  | 101  | 18.8  | 101      | 17.6  |

| Total  | 1667 | 235.9 | 1667 | 213.  | 1667     | 200.5 |

표 1에 나타낸 것과 같이 [15]와 [18]의 알고리즘에 면적은 동일하나 소모 전력은 [15]에 비해 약 15%, [18]에비해 약 6%의 전력 소모가 감소된 것으로 나타났다.

### V. 결론

본 논문에서는 글리치 전력소모 감소를 이용한 CPLD 저전력 알고리즘을 제안하였다.

제안한 알고리즘은 디지털 회로를 구현하기 위한 CPLD를 구성하고 있는 CLB의 제한 조건에 맞도록 회로 를 분할하여 매핑 가능 클러스터를 생성하였다. 생성된 매핑 가능 클러스터에 대해 지연 버퍼 삽입 방법을 이용하여 글리치를 제거할 수 있는 글리치 제거 알고리즘을 제안하였다. 또한 글리치가 제거된 매핑 가능 클러스터 사이의 글리치를 제거 할 수 있는 알고리즘도 제안하였다.

제안한 알고리즘을 SIS에서 제공되는 벤치마크에 적용하여 상관관계에 의한 CLB구조의 CPLD 저전력 기술 매핑 알고리즘[15]과 선택적 글리치 제거 방법을 이용한 저전력 기술 매핑 알고리즘[18]과 소모 전력을 비교하였다. 비교 결과 [15]에 비해 약 15%, [18]에 비해 약 6%의 전력 소모가 감소되어 제안한 방법이 기존의 다른 방법보다 소모 전력이 최소인 설계 방법임을 실험을 통해 입증하였다.

### 참고문헌

- [1] The MACH 4 Family Data Sheet, Advanced Micro Devices, 1996.

- [2] S. Devadas, S. malik, "A Survey of Optimization Techniques Targeting Low Power VLSI Circuits", in Proc. 32nd DAC, June 1995, pp. 242-247.

- [3] A. Chandrakasan, T. Sheng, and R. Brodersen, "Low Power CMOS Digital Design", Journal of Solid State Circuits, vol. 27, no. 4, April 1992, pp. 473-484.

- [4] S. ErColani et al., "Testability measures in pseudorandom testing", IEEE Trans. Conputer-Aided Design., vol. 11, 1992, June, pp. 794-800.

- [5] J. Cong and Y. Ding, "FlowMap: An 'Optimal Technology Mapping Algorithm for Delay Optimization in Lookup-Table Based FPGA Designs", IEEE Transactions on Computer-Aided Design of Integrated Circuit and Systems, Vol. 13, No. 1, January 1994, pp. 1-11.

- [6] R. J Francis, J. Rose and Z. Vranestic, "Chortle-crf

: Fast Technology Mapping for Lookup

Table-Based FPGAs", 28th ACM/IEEE Design

Automation Conference, June 1991, pp. 227-233.

- [7] Zhi-Hong Wang, En-Cheng Liu, Jianbang Lai, Ting-Chi Wang, "Power Minimization in LUT-Based FPGA Technology Mapping", ASP-DAC, January 2001, pp. 635-640.

- [8] A. H. Farrahi and M. Sarrafzadeh, "FPGA Technology Mapping for Power Minimization", Proc. Int. Workshop on field Programmable Logic and Applications, 1994, pp. 66-77.

- [9] C. -C. Wang and C. -P. Kwan, "Low Power Technology Mapping by Hiding high-Transition Paths in Invisible Edges of LUT-Based FPGAs", Proc. Int. Symp. on Circuits and Systems, 1997, pp. 1536-1539.

- [10] R. J Francis, J. Rose and Z. Vranestic, "Technology Mapping of Lookup Table-Based FPGAs for Performance", 1991 IEEE Conference on Computer Aided Design, pp. 568-571.

- [11] E. M. Sentovice et al., "SIS: A system for sequential Circuit Synthesis", Technical Report UCM/ERL M92/41, Electronics Research Laboratory, Department of Electrical Engineering and Computer Science, University of California, Berkeley, 1992.

- [12] Jason Helge Anderson, Stephen Dean Brown, "Technology Mapping for Large Complex PLDs", Design Automation Conference, 1998, pp. 698-703.

- [13] 윤충모, 김희석, "시간적 조건에서 실행 시간을 개선한 CPLD 기술 매핑 알고리즘 개발", 한국 OA 학회 논문집 vol 4권 3호, 1999, pp. 35-46.

- [14] Jae-Jin Kim, Hi-Seok Kim, Chi-Ho Lin, "A New Technology Mapping for CPLD under the time

- constraint", ASP-DAC, January 2001, pp. 235-238.

- [15] 김재진, 이관형, "상관관계에 의한 CLB구조의 CPLD 저전력 기술 매핑 알고리즘", 한국컴퓨터정 보학회 논문집 제10권 제2호, 2005, pp. 49-57.

- [16] M. Hahimoto, H. Onodera, and K. Tamaru, "A Power Optimization Method Considering Glitch Reduction by Gate Sizing", in Proc. Int'l Symp. on Low Power Design, August, 1998, pp. 221-226.

- [17] 강승일, "트랜지스터 사이징을 통한 CMOS 회로에 서의 글리치 감소의 저 전력 설계에 대한 연구", 서 강대학교, 1999.

- [18] Kwan-Houng Lee, Jin-Gu Kang, Nam-Seo Park, Choong-Mo Yun, Jae-Jin Kim, "A Low Power Communication Circuit Design using Selective Glitch Removal Method", FGCN2008, December, 2008, pp. 51-56.

#### ■ 저자소개 ■

허화라 Hur, Hwa Ra

2001년 8월 부산대학교 전자공학과 공학박사 2000년~현재

송호대학 컴퓨터정보과 교수

관심분야 : 알고리즘, 컴퓨터구조 E-mail : hrhur@songho.ac.kr

논문접수일: 2009년 8월 4일 수 정 일: 2009년 8월 21일 게재확정일: 2009년 8월 30일