# Study of Thermal Stability of Ni Silicide using Ni-V Alloy

Zhun Zhong, Soon-Young Oh, Won-Jae Lee, Ying-Ying Zhang, Soon-Yen Jung, Shi-Guang Li, Ga-Won Lee, Jin-Suk Wang, and Hi-Deok Lee<sup>a</sup> Department of Electrical Engineering, Chungnam National University, 220 Gung-dong, YuSeung-gu, Daejeon 305-764, Korea

# Yeong-Cheol Kim

Department of Materials Engineering, Korea University of Technology and Education, Gajeonri 307, Byeongcheon-myeon, Cheonan-si, Chungnam 330-702, Korea

<sup>a</sup>E-mail: <u>hdlee@cnu.ac.kr</u>

(Received September 6 2006, Accepted February 18 2008)

In this paper, thermal stability of Nickel silicide formed on p-type silicon wafer using Ni-V alloy film was studied. As compared with pure Ni, Ni-V shows better thermal stability. The addition of Vanadium suppresses the phase transition of NiSi to NiSi<sub>2</sub> effectively. Ni-V single structure shows the best thermal stability compared with the other Ni-silicide using TiN and Co/TiN capping layers. To enhance the thermal stability up to 650 °C and find out the optimal thickness of Ni silicide, different thickness of Ni-V was also investigated in this work.

Keywords: Ni-V(Nickel vanadium) alloy, Thermal stability, Ni silicide, RTP

## 1. INTRODUCTION

The Self-aligned silicide (Salicide) is one of the key methods in modern ULSI technologies to increase device speed by reducing the series resistance of source/drain and gate[1-3]. Titanium silicide (TiSi<sub>2</sub>) was firstly used 0.35-um complementary metal semiconductor (CMOS) technology attribute to its low sheet resistance and high thermal immunity. However, due to the difficulty of the phase transition from  $C_{49}$  to C<sub>54</sub> on a very narrow line, which can induce a dramatic increase in the sheet resistance, TiSi2 was replaced by CoSi<sub>2</sub> in 0.25-um CMOS technology. However, the CoSi<sub>2</sub> also has its drawbacks, such as the high consumption of the silicon and large increment of the sheet resistance below sub-100 nm MOSFETs. Therefore, nowadays, nickel silicide (NiSi) is being rese arched actively as a substitute of TiSi<sub>2</sub> and CoSi<sub>2</sub> in nanoscale CMOS device fabrication processes. Ni silicide (NiSi) has characteristics like low resistivity, low formation temperature, small stress and less silicon consumption compared with the commonly used TiSi2 and CoSi<sub>2</sub>[4-6]. All of these features made NiSi as a competent material for nanoscale CMOSFETs. In addi tion, the low-resistivity Nickel monosilicide (NiSi) can be easily obtained from one step rapid thermal process (RTP) at low temperature. However, the thermal stability of Ni silicide is poor because of the formation of highresistivity phase NiSi<sub>2</sub>, which is the main obstacle to the successful application of NiSi in conventional ULSI processes. In order to improve its thermal stability, many approaches such as ion implantation[7], alloy target of NiTa[8], NiPt[9] and deposition of inter- and/or capping- layers have been proposed[10].

In this paper, various film structures such as Ni-V, Ni-V/TiN and Ni-V/Co/TiN had been investigated to enhance the thermal stability of Ni silicide. It is proved that Ni-V has a better thermal stable characteristic w hen compared with Ni-V/TiN and Ni-V/Co/TiN. Moreover, as the thickness of Ni-V structure increased, the sheet resistance was shown to be more stable. As a result, NiSi utilizing Ni-V alloy is most recommended for highly thermal immune CMOS technology.

## 2. EXPERIMENT

In this experiment, four structures of Ni (8 nm), Ni-V (8 nm), Ni-V/TiN (8/25 nm), and Ni-V/Co/TiN (6/2/25 nm) were deposited on p-type Si wafers using RF magnetron sputtering system without breaking vacuum after removal of the native oxide in the HF dilute solution (HF:  $H_2O = 1:100$ ). Nickel silicide was formed in rapid thermal process (RTP) at various temperatures (400, 500, 600, 650 and 700 °C) for 30 sec. Un-reacted metals were selectively wet-etched in  $H_2SO_4 + H_2O_2$  (4:1) solution. To test the thermal stability of nickel silicide, post-silicidation annealing was carried

out at three different temperatures (550, 600 and 650 °C) for 30min with N<sub>2</sub> ambient. Sheet resistance of nickel silicide was measured using conventional four point probe (FPP). AFM (Atomic Force Microscope) and XRD (X-ray Diffraction) analysis were performed to investigate surface roughness and phase identification. Thickness and morphologies of Nickel silicide were characterized by FE-SEM (Field Emission Scanning Electron Microscopy, Jeon-ju Branch of the Korea Basic Science Institute, Model S-4700).

#### 3. RESULTS AND DISCUSSION

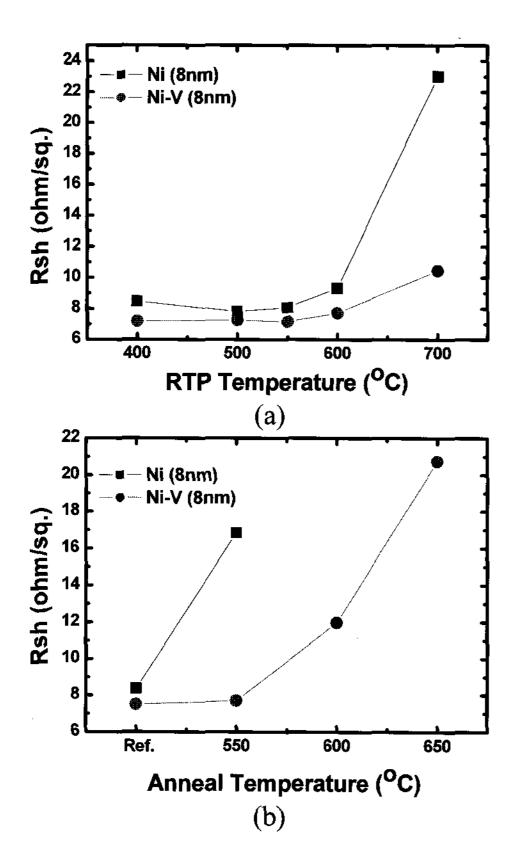

Phase transition study shows the influence of vanadium addition on stability of nickel silicide. Phase transition curves of Ni and Ni-V films on p-type silicon were obtained as in Fig. 1. Ni-V case shows lower sheet resistance and wider RTP window compared with Ni only case. Moreover, there is a drastic improvement of thermal stability by addition of Vanadium as shown in Fig. 1(b). After post-silicidation annealing, Ni-V silicide film remains more stable than the pure Ni film of the same physical thickness. These results imply that the addition of vanadium makes NiSi more stable and enlarges the RTP process window by suppressing the phase transition to high resistive NiSi<sub>2</sub>.

Fig. 1. Sheet resistance as a function of RTP temperature (a) and post-silicidation annealing (b) for Ni-V alloy and pure Ni cases.

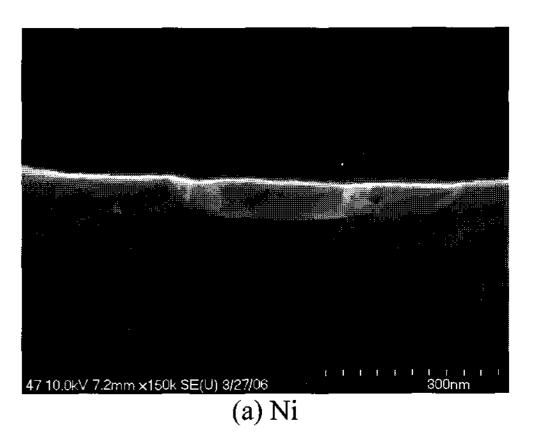

Fig. 2. FESEM images of NiSi for pure Ni (a) and Ni-V alloy (b) after post-silicidation annealing at 600 °C.

FE-SEM images of nickel silicide for pure Ni and Ni-V alloy were shown in Fig. 2. In case of pure Ni structure, NiSi was agglomerated and large silicide island was found. However, NiSi with Ni-V case maintained stable resistance even after the post-silicidation annealing for 30 min at 600 °C and the result is well matched with sheet resistance properties as shown in Fig. 1(b).

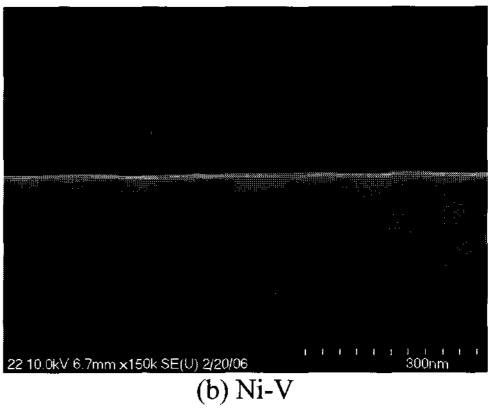

Fig. 3. XRD scans of pure-Ni and Ni-V silicide for both RTP temperatures of 500-700  $^{\circ}$ C( $\blacksquare$  for NiSi and  $\bullet$  for NiSi<sub>2</sub>).

XRD was used to identify the silicide phases as presented in Fig. 3. Almost same profiles were obtained from pure-Ni and Ni-V cases. However, in case of Ni-V, less NiSi<sub>2</sub> peaks were observed reflecting that better thermal stability than pure-Ni structure. The result suggests that the addition of vanadium suppresses the phase transition of NiSi to high resistive NiSi<sub>2</sub> effectively.

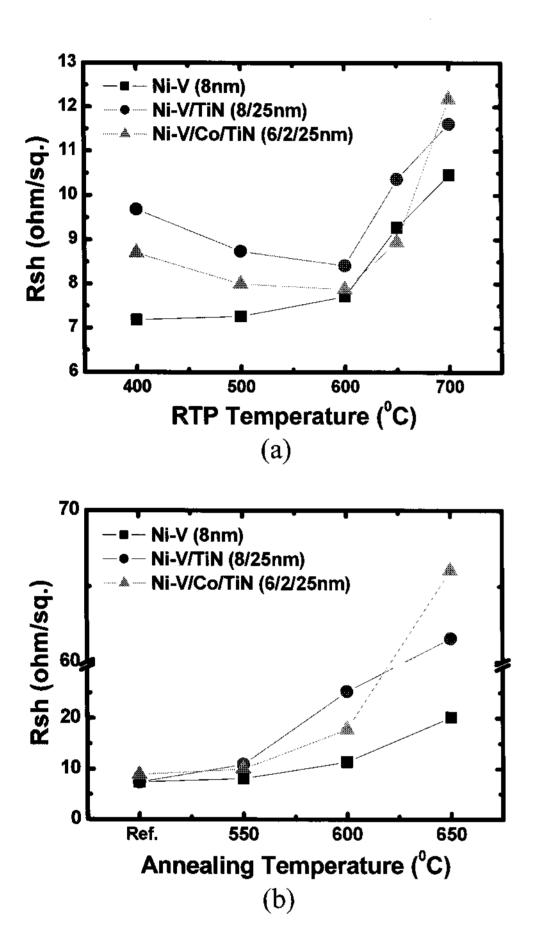

Fig. 4. Sheet resistance of Nickel silicide after (a) RTP and (b) post-silicidation annealing.

Figure 4(a) shows the sheet resistance of nickel silicide after different RTP temperatures. It can be seen that Ni-V structure has lower sheet resistance compared with other structures. Moreover, after post-silicidation annealing for 30 min, nickel silicide formed with Ni-V system shows better thermal stability than that formed with Ni-V/TiN and Ni-V/Co/TiN structures as shown in Fig. 4(b). It is quite interesting that sheet resistance of Ni-silicide increases by the adoption of capping layers such as TiN and Co/TiN. But in case of pure Ni target, sheet resistance decreased by using capping layers. Sheet resistance of nickel silicide shows drastic increase from annealing temperature at 600 °C. To explain this

phenomenon, the surface roughness and cross-sectional profiles were investigated.

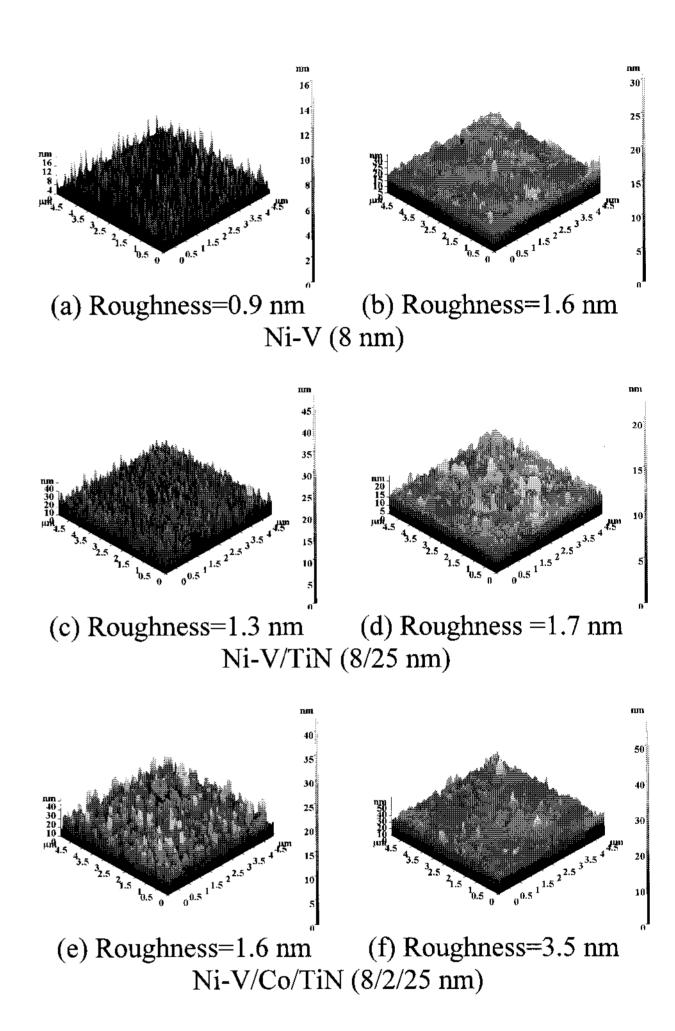

Figure 5 shows surface roughness of silicides formed with Ni-V, Ni-V/TiN and Ni-V/Co/TiN. The picture of Ni-V (RMS=1.6 nm) shows better surface roughness than Ni-V/TiN (RMS=1.7 nm) and Ni-V/Co/TiN (RMS=3.5 nm). The difference of surface roughness, however, is not serious.

Fig. 5. AFM surface roughness of NiSi before post-silicidation annealing (a), (c), (e) and after post-silicidation annealing (b), (d), (f).

Figure 6 are the cross-sectional FE-SEM images of nickel silicide before and after post-silicidation annealing. The interface of NiSi/Si shows uniform and the thickness of NiSi shows similar property in all three cases. However, after post-silicidation annealing, the Ni-V/TiN and the Ni-V/Co/TiN show agglomerations after post-silicidation annealing. Contrary to these cases, Ni-V presents a better NiSi/Si interface profile. Because the agglomeration usually accompanies the phase transition from low-resistivity phase mono-silicide

(NiSi) to high-resistivity phase disilicide (NiSi<sub>2</sub>), the drastic increase of sheet resistance after post-silicidation annealing temperature at 650 °C that shown in Fig. 4(b) can be explained by the agglomeration of Ni-silicide during high temperature post-silicidation annealing.

Fig. 6. FE-SEM cross-sectional profile of NiSi before post-silicidation annealing (a), (c), (e) and after post-silicidation annealing (b), (d), (f).

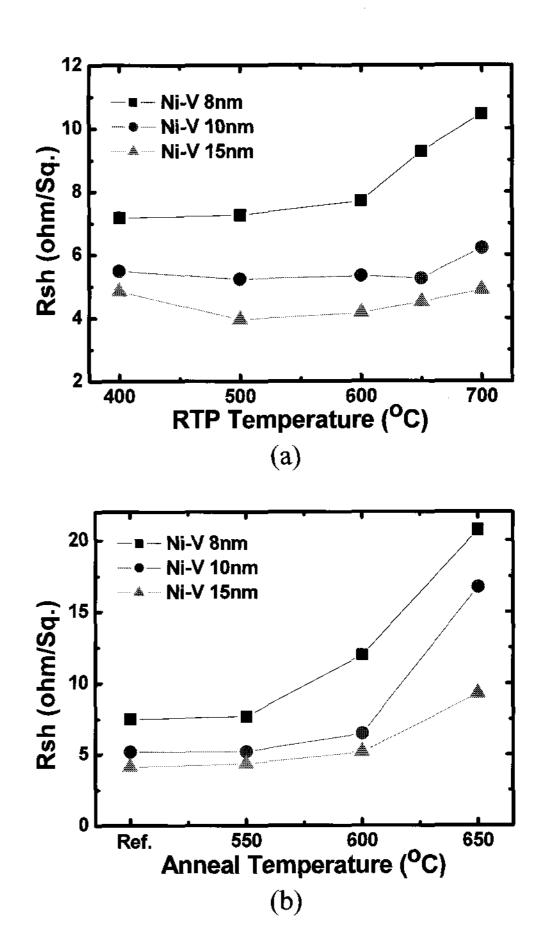

Figure 7 indicates that the thermal stability of Nickel silicide is dependent on the thickness of Ni-V film. The sheet resistance of nickel silicide with 8 nm Ni-V becomes more than 10 Ohm/Sq while 15 nm Ni-V maintains its low and stable sheet resistance after post-silicidation annealing at 600 °C. Therefore, film thickness should be carefully decided for nano-scale CMOS technology.

## 4. CONCLUSION

The nickel silicide properties were studied in this paper. Better thermal stability was achieved by the proposed Ni-V structure while sheet resistance of the Ni-V/TiN and the Ni-V/Co/TiN increases abruptly after

post-silicidation annealing at 600 °C. Ni-V structure also shows smoother cross-sectional profile than the other structures. Moreover, in case of Ni-V system, it is found that the sheet resistance becomes more stable as the thickness of Ni-V structure increased.

Fig. 7. Dependence of sheet resistance and thermal stability of Nickel silicide on the thickness of Ni-V (a) after silicidation (RTP) and (b) after post-silicidation annealing.

# **ACKNOWLEDGMENTS**

This work was supported by grant No. (R01-2003-000-11659-0) from the Basic Research Program of the Korea Science and Engineering Foundation (KOSEF).

## **REFERENCES**

[1] Zhang S. L. and Ostling M., "Metal silicides in CMOS technology: Past, present and future trends", Critical Reviews in Solid State and Materials Sciences, Vol. 28, No. 1, p. 1, 2004.

- [2] T. Morimoto, T. Ohguro, H. S. Momose, T. Iinuma, I. Kunishima, K. Suguro, I. Katakabe, H. Nakajima, M. Tsuchiaki, M. Ono, Y. Katsuma, and H. Iwai, "Self-aligned nickel-mono-silicide technology for high-speed deepsubmicrometer logic CMOS ULSI", IEEE Transaction On Electron Devices, Vol. 42, No. 5, p. 915, 1995.

- [3] C. Y. Lin, W. J. Chen, C. H. Lai, A. Chin, and J. Liu, "Formation of Ni germano-silicide on single crystalline Si/sub 0.3/Ge/sub 0.7/Si", IEEE Electron Device Letters, Vol. 23, No. 8, p. 464, 2002.

- [4] H. Iwai, T. Ohguro, and S. I. Ohmi, "NiSi salicide technology for scaled CMOS", Microelectron. Eng., Vol. 60, p. 157, 2002.

- [5] Lauwers A., Streegen A., de Potter M., Lindsay R., Satta A., Bender H., and Maex K., "Materials aspects, electrical performance, and scalability of Ni silicide towards sub-0.13 um technologies", Journal of Vacuum Science & Technology B, Vol. 19, No. 6, p. 2026, 2001.

- [6] Iwai H., Ohguro T., and Ohmi S. I., "NiSi salicide technology for scaled CMOS", Microelectronic Engineering, Vol. 60, p. 157, 2002.

- [7] C. J. Choi, S. A. Song, Y. W. Ok, and T. Y. Seong, "Nickel-silicidation process using hydrogen implantation", Electronics Letters, Vol. 40, No. 6, p. 391, 2004.

- [8] M. C. Sun, M. J. Kim, J. H. Ku, K. J. Roh, C. S. Kim, S. P. Youn, S. W. Jung, S. Choi, N. I. Lee, H. K. Kang, and K. P. Suh, "Thermally robust Tadoped NiSALICIDE process promising for sub-50 nm CMOSFETs", 2003 Symposium on VLSI Technology Digest of Technical Papers, p. 81, 2003.

- [9] P. S. Lee, D. Mangelinck, K. L. Pey, J. Ding, D. Z. Chi, T. Osipowicz, J. Y. Dai, and A. See, "Enhanced stability of Ni monosilicide on MOSFETs poly-Si gate stack", Microelectronic Engineering, Vol. 60, Issues 1-2, p. 171, 2002.

- [10] J. G. Yun, S. Y. Oh, B. F. Huang, H. H. Ji, Y. G. Kim, S. H. Park, H. S. Lee, D. B. Kim, U. S. Kim, H. S. Cha, S. B. Hu, J. G. Lee, S. K. Baek, H. S. Hwang, and H. D. Lee, "Highly thermal robust NiSi for nanoscale MOSFETs utilizing a novel hydrogen plasma immersion ion implantation and Ni-Co-TIN tri-layer", IEEE Electron Device Letters, Vol. 26, No. 2, p. 90, 2005.