# Stress Dependence of Thermal Stability of Nickel Silicide for Nano MOSFETs

Ying-Ying Zhang, Won-Jae Lee, Zhun Zhong, Shi-Guang Li, Soon-Yen Jung, Ga-Won Lee,

Jin-Suk Wang, and Hi-Deok Lee<sup>a</sup>

Department of Electronics Engineering, Chungnam National University,

220 Gung-dong, Yusong-gu, Daejeon 305-764, Korea

Sung-Kyu Lim

Thin Film Team, National Nanofab Center,

53-3 Eoeun-dong, Yuseong-gu, Daejeon 305-806, Korea

<sup>a</sup>E-mail: <u>hdlee@cnu.ac.kr</u>

(Received March 5 2007, Accepted April 24 2007)

Dependence of the thermal stability of nickel silicide on the film stress of inter layer dielectric (ILD) layer has been investigated in this study and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) layer is used as an ILD layer. Nickel silicide was formed with a one-step rapid thermal process at 500 °C for 30 sec. 2000 Å thick Si<sub>3</sub>N<sub>4</sub> layer was deposited using plasma enhanced chemical vapor deposition after the formation of Ni silicide and its stress was split from compressive stress to tensile stress by controlling the power of power sources. Stress level of each stress type was also split for thorough analysis. It is found that the thermal stability of nickel silicide strongly depends on the stress type as well as the stress level induced by the Si<sub>3</sub>N<sub>4</sub> layer. In the case of high compressive stress, silicide agglomeration and its phase transformation from the low-resistivity nickel mono-silicide to the high-resistivity nickel di-silicide are retarded, and hence the thermal stability is obviously improved a lot. However, in the case of high tensile stress, the thermal stability shows the worst case among the stressed cases.

Keywords: Nickel silicide, Thermal stability, Silicon nitride, Mechanical stress, Nano MOSFETs

## 1. INTRODUCTION

Self-aligned-silicides (SALICIDEs) are inevitable for complementary metal oxide semiconductor field effect transistor (CMOSFET) to reduce the series resistance of gate, source and drain areas[1]. Recently, nickel monosilicide (NiSi) has been considered as a viable candidate for contact material because of its low resistivity, relatively low formation temperature, no resistivity increase in narrow lines and smaller silicon consumption during silicidation[2]. However, poor thermal stability of the nickel silicide is a main weakness to be applied to nano-scale CMOSFET technology which needs high temperature processes after formation of the silicide[3]. To overcome this problem, many attempts such as ion implantation[4], application of alloying target materials [5-10] and deposition of capping layer[11,12] have been suggested.

As the device dimensions scale down to nano-scale regime, mobility variation induced by mechanical stress

of various films has shown more pronounced effect on the device performance. Therefore, stress engineering or control of the mechanical stress of various films such as shallow trench isolation gap fill oxide layer, silicide blocking layer and inter layer dielectric (ILD) layer has attracted a lot of attention to improve the device performance of metal oxide semiconductor field effect transistors (MOSFET) and it is known that tensile stress improves n-type MOSFET and compressive stress improves p-type MOSFET, respectively[13]. Among the various oxide layers, stress of ILD layer has an effect on the silicide property because it is directly deposited on top of the silicide layer. Especially, Si<sub>3</sub>N<sub>4</sub> layer on top of silicide is a must in a high density CMOS technology as an etch stop layer for formation of borderless contacts. Therefore, the stress of Sl<sub>3</sub>N<sub>4</sub> layer will directly affect the nickel silicide property as well as the device performance. However, there was little studies on the mechanical stress effect of ILD layer on the Ni silicide properties although the influences of stress on the

interfacial reactions of Ti and Ni metal thin films on Si [14] and stress evolution during silicide formation[15-17] have been studied.

In this paper, the dependence of the thermal stability of nickel silicide on the mechanical stress of Si<sub>3</sub>N<sub>4</sub> layer is characterized in depth by varying the stress type from compressive to tensile stress. The stress level of each stress type is also split for thorough analysis of the dependence.

#### 2. EXPERIMENTAL

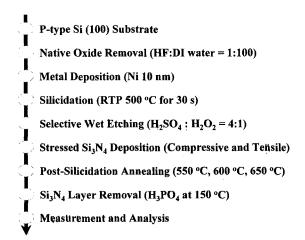

A brief fabrication process flow is summarized in Fig. 1. P-type Si (100) wafer was cleaned and dipped in a HF solution to remove the native oxide. Then, 10 nm thick Ni layer was deposited by RF magnetron sputtering system with a base pressure of  $5 \times 10^{-7}$  Torr and a working pressure of 1 mTorr. For the formation of Ni silicide, a one-step rapid thermal process (RTP) was carried out at 500 °C for 30 sec. Un-reacted metal was selectively removed using a mixture of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> with the volume ratio of 4:1. Then, 2000 Å thick Si<sub>3</sub>N<sub>4</sub> layer was deposited by plasma enhanced chemical vapor deposition (PECVD) using a standard recipe with a mixture of SiH<sub>4</sub> and NH<sub>3</sub>. The film stress of Si<sub>3</sub>N<sub>4</sub> was split from tensile to compressive stress by controlling the RF power of PECVD as will be detailed later. Reference sample without the Si<sub>3</sub>N<sub>4</sub> layer was also fabricated for comparison. Finally, to evaluate the thermal stability of silicides, samples were furnace annealed in N<sub>2</sub> ambient at three different high temperatures for 30 min (postsilicidation annealing in short). Wet etching of the Si<sub>3</sub>N<sub>4</sub> layer was carried out to measure the variation of sheet resistance of Ni silicide using H<sub>3</sub>PO<sub>4</sub> solution at 150 °C.

Fig. 1. Key process flow for experiments.

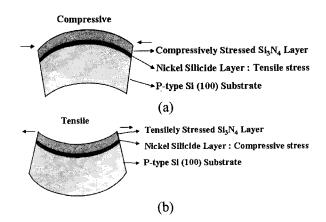

Fig. 2. Schematic diagrams of the (a) compressively and (b) tensilely stressed samples.

Table 1. The samples classification for experiments.

| Sample | Stress Type      | Stress Magnitude |

|--------|------------------|------------------|

| A      | Reference        | <u>-</u>         |

| В      | High Compressive | -600 MPa         |

| С      | Low Compressive  | -110 MPa         |

| D      | High Tensile     | 580 MPa          |

| Е      | Low Tensile      | 25 MPa           |

Figure 2 shows the schematic diagrams of the samples with compressive and tensile stresses, respectively. Wafer curvature measurements were performed using FSM500TC (Frontier Semiconductor, Inc.), which utilizes a scanning laser technique. Film stress was calculated from curvature measurements using the wellknown Stoney's equation[18] for biaxial film stress,  $\sigma_f$ :  $\sigma_f = (k - k_0) \left[ E_s / (1 - v_s) \right] \left( t_s^2 / 6t_f \right)$ , where k and  $k_0$ are curvatures of the film-substrate system and bare substrate, respectively,  $E_s$  is the substrate Young's modulus,  $v_s$  is the substrate Poisson's ratio, and t is thickness with subscripts appropriate to the film, f, and substrate, s. The biaxial modulus,  $E_s/(1-v_s)$ , of (100) silicon is 180.5 GPa[19]. The stress type and magnitude of the Si<sub>3</sub>N<sub>4</sub> films were varied with the control of the radio frequency (RF) operation power of high frequency (HF) power source with a frequency of 13.56 MHz and low frequency (LF) power source with a frequency of 250 kHz, respectively. The sum of operation powers of HF and LF power sources is kept to be 1000 Watt. As the operation power of LF power source was adjusted from 900 to 500 Watt and from 100 to 500 Watt of the HF power source, the magnitude of compressive stress was varied from 600 to 110 MPa. The tensile stress of Si<sub>3</sub>N<sub>4</sub> film was split from 25 to 580 MPa with decreasing the RF power of LF power source from 400 to 0 Watt and increasing power of HF power source from 600 to 1000 Watt, respectively. The classification of samples with stress split is summarized in Table 1.

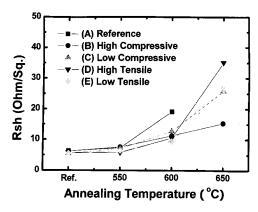

Fig. 3. Comparison of sheet resistance of silicide between with and without stressed Si<sub>3</sub>N<sub>4</sub> layer as a function of post-silicidation annealing temperature.

Sheet resistance was measured using conventional four point probe method. The uniformity of the silicide was observed using field emission scanning electron microscopy (FESEM, Jeonju branch of Korea Basic Science Institute (KBSI), model: Hitach S-4700). Thinfilm X-ray diffraction (XRD) and secondary ion mass spectrometer (SIMS) analyses were performed to investigate phase identification and depth profile of Ni, respectively.

#### 3. RESULTS AND DISCUSSION

After post-silicidation annealing, the sheet resistance window as a function of post-silicidation annealing temperature is shown in Fig. 3. Little difference of sheet resistance between the stressed and reference samples is observed until 550 °C. However, the sheet resistance of sample A or reference sample increases abruptly from 600 °C and becomes immeasurable at 650 °C, while the other samples with stressed  $Si_3N_4$  layer show more stable sheet resistance than the reference. Among the stressed samples, the compressive stress case shows smaller sheet resistance than the tensile stress one and the higher compressive stress results in the lower sheet resistance. Among the tensile stress cases, the higher tensile stress shows higher sheet resistance than the lower stress case.

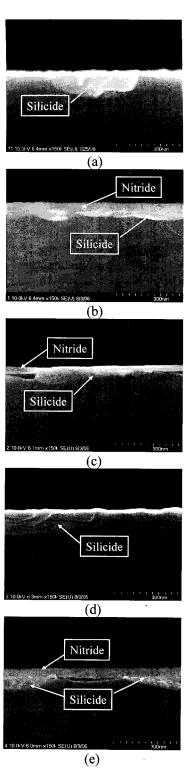

Figure 4 presents cross-sectional FESEM images of samples after post-silicidation annealing at 650 °C for 30 min. Because the etching rate of Si<sub>3</sub>N<sub>4</sub> layers with different stress type and level is not identical, the etching time of each sample is carefully controlled but some samples show thin remained Si<sub>3</sub>N<sub>4</sub> layer, as can be seen in Figs. 4(b), (c) and (e). However, there was no problem in measuring sheet resistance. The best cross-sectional profile of silicide layer is found in the high compressively stressed silicide (sample B), as shown in Fig. 4(b), which is in good agreement with the low sheet resistance in Fig. 3. However, the agglomerations can be observed in sample A, C, D and E, as shown in Figs. 4(a),

Fig. 4. FESEM images of nickel silicide (a) reference, (b) high compressive, (c) low compressive, (d) high tensile, and (e) low tensile cases after post-silicidation annealing at 650  $^{\circ}$ C for 30 min in N<sub>2</sub> ambient.

(c), (d) and (e). Silicide with lower compressive stress shows less agglomeration than tensilely stressed silicides. Therefore, it can be said that the lower sheet resistance and

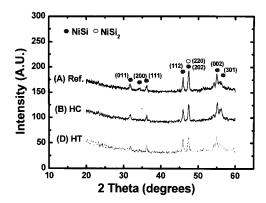

Fig. 5. XRD spectra of nickel silicide after post-silicidation annealing at 650 °C for 30 min in  $N_2$  ambient.

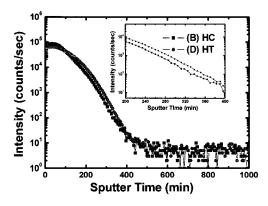

Fig. 6. SIMS depth profiles of Ni for sample B and D after post-silicidation annealing at 650 °C for 30 min in N<sub>2</sub> ambient. The inset shows the partial enlarged figure.

better cross-sectional profile of compressive case is owing to the retardation of agglomeration by the compressively stressed  $Si_3N_4$  layer.

XRD analyses of samples after post-silicidation annealing at 650 °C were performed to characterize the phase change by the Si<sub>3</sub>N<sub>4</sub> layer and the difference between samples, as shown in Fig. 5. The low-resistivity NiSi phase peaks of (011), (200), (111), (112), (202), (002) and (301) appear in all samples and there is little difference between samples. However, the high-resistivity NiSi<sub>2</sub> phase peak also appears in all samples even though there is some overlap between the NiSi (202) diffraction peak with the NiSi<sub>2</sub> (220) diffraction peak. By taking into account of sheet resistance and XRD analysis, it can not be said that the lowest sheet resistance of sample B is owing to the retardation of phase transformation from NiSi to NiSi<sub>2</sub>.

The SIMS depth profiles of Ni for high compressively stressed sample B and high tensile stressed sample D after post-silicidation annealing at 650 °C are reported in Fig. 6. Although the remarkable difference between

sample B and sample D has not been observed, sample B shows less diffusion of Ni into substrate than sample D, as clearly shown in the inset in Fig. 6. Therefore, it can be concluded that the improved thermal stability of high compressive case is mainly owing to the enhanced retardation of silicide agglomeration during the post-silicidation annealing.

## 4. CONCLUSION

Dependence of the thermal stability of nickel silicide on the stress of ILD Si<sub>3</sub>N<sub>4</sub> layer is systematically analyzed with detailed split of film stress of Si<sub>3</sub>N<sub>4</sub> layer. It is found that Ni silicide with compressive stress shows a lower sheet resistance and less agglomeration than silicide with tensile stress and higher compressive stress is desirable for the better silicide properties. It is also shown that the retardation of silicide agglomeration by the compressive stress results in a lower sheet resistance and uniform silicide profile. Therefore, stress of ILD layer should be carefully considered to prevent the degradation of Ni silicide for the nano-scale strained-Si CMOS technology.

#### ACKNOWLEDGMENTS

This work was supported by grant No. (R01-2003-000-11659-0) from the Basic Research Program of the Korea Science and Engineering Foundation (KOSEF), and Ying-Ying Zhang thanks Ilun Science and Technology Foundation for support of this work.

### REFERENCES

- [1] S. P. Murarka, "Self-aligned silicides or metals for very large scale integrated circuit applications", J. Vac. Sci. Technol. B, Vol. 4, p. 1325, 1986.

- [2] H. Iwai, T. Ohguro, and S. I. Ohmi, "NiSi salicide technology for scaled CMOS", Microelectron. Eng., Vol. 60, p. 157, 2000.

- [3] F. Deng, R.A. Johnson, P. M. Asbeck, and S. S. Lay, "Salicidation process using NiSi and its device application", J. Appl. Phys., Vol. 81, No. 12, p. 8047, 1997.

- [4] C. J. Choi, Y. W. Ok, S. S. Hullavarad, T. Y. Seong, K. M. Lee, J. H. Lee, and Y. J. Park, "Effects of hydrogen implantation on the structural and electrical properties of nickel silicide", J. Electrochem. Soc., Vol. 149, p. G517, 2002.

- [5] Y. J. Kim, S. Y. Oh, W. J. Lee, Y. Y. Zhang, Z. Zhong, S. Y. Jung, H. H. Ji, H. S. Cha, Y. C. Kim, J. S. Wang, and H. D. Lee, "Thermal stability improvement of Nickel Germanosilicide utilizing

- Ni-Pd alloy nano-scale CMOS technology", IEEE Si Nanoelectronics Workshop, p. 51, 2006.

- [6] L. J. Jin, K. L. Pey, W. K. Choi, D. A. Antoniadis, E. A. Fitzgerald, and D. Z. Chi, "Electrical characterization of platinum and palladium effects in nickel monosilicide/n-Si Schottky contacts", Thin Solid Films, Vol. 504, p. 149, 2006.

- [7] K. L. Pey, P. S. Lee, and D. Mangelinck, "Ni(Pt) alloy silicidation on (100) Si and poly-silicon lines", Thin Solid Films, Vol. 462-463, p. 137, 2004.

- [8] P. S. Lee, K. L. Pey, D. Mangelinck, J. Ding, D. Z. Chi, and L. Chan, "New salicidation technology with Ni(Pt) alloy for MOSFETs", IEEE Electron Device Lett., Vol. 22, No. 12, p. 568, 2001.

- [9] S. Y. Oh, J. G. Yun, B. F. Huang, Y. J. Kim, H. H. Ji, U. S. Kim, H. S. Cha, S. B. Heo, J. G. Lee, J. S. Wang, and H. D. Lee, "Novel nitrogen doped Ni self-alingned silicide process for nanoscale complementary metal oxide semiconductor technology", Jpn. J. Appl. Phys., Vol. 44, p. 2142, 2005.

- [10] M. C. Sun, M. J. Kim, J. H. Ku, K. J. Roh, C. S. Kim, S. P. Youn, W. Jung, S. Choi, N. I. Lee, H. K. Kang, and K. P. Suh, "Thermally robust Ta-doped Ni SALICIDE process promising for sub-50 nm CMOSFETs", Symposium on VLSI Tech. Dig., p. 81, 2003.

- [11] Y. J. Kim, C. J. Choi, R. J. Jung, S. Y. Oh, J. G. Yun, W. J. Lee, H. H. Ji, J. S. Wang, and H. D. Lee, "The effect of triple capping layer (Ti/Ni/TiN) on the electrical and structural properties of nickel

- monosilicide", J. Electrochem. Soc., Vol. 153, p. G35, 2006.

- [12] B. F. Huang, S. Y. Oh, J. G. Yun, Y. J. Kim, H. H. Ji, Y. G. Kim, J. S. Wang, and H. D. Lee, "Study of Ni-germano silicide thermal stability for nano-scale CMOS technology", J. of KIEEME(in Korean), Vol. 17, No. 11, p. 1149, 2004.

- [13] J. L. Hoyt, H. M. Nayfeh, S. Eguchi, I. Aberg, G. Xia, T. Drake, E. A. Fitzgerald, and D. A. Antoniadis, "Strained silicon MOSFET technology", in IEDM Tech. Dig., p. 23, 2002.

- [14] S. L. Cheng, H. M. Lo, L. W. Cheng, S. M. Chang, and L. J. Chen, "Effects of stress on the interfacial reactions of metal thin films on (0 0 1)Si", Thin Solid Films, Vol. 424, p. 33, 2003.

- [15] C. J. Tsai and K. H. Yu, "Stress evolution during isochronal annealing of Ni/Si system", Thin Solid Films, Vol. 350, p. 91, 1999.

- [16] S. S. Guoa, Y. C. Chub, and C. J. Tsai, "Stress evolution in Co/Ti/Si system", Mater. Chem. Phy., Vol. 88, p. 71, 2004.

- [17] C. J. Tsai, P. L. Chung, and K. H. Yu, "Stress evolution of Ni/Pd/Si reaction system under isochronal annealing", Thin Solid Films, Vol. 365, p. 72, 2000.

- [18] G. G. Stoney, "The tension of metallic films deposited by electrolysis", Proc. R. Soc. London, Ser. A, Vol. 82, p. 172, 1909.

- [19] W. A. Brantley, "Calculated elastic constants for stress problems associated with semiconductor devices", J. Appl. Phys., Vol. 44, p. 534, 1973.