# The Characterization of Poly-Si Thin Film Transistor Crystallized by a New Alignment SLS Process

Sang Jin Lee\*, Joon Young Yang, Kwang Sik Hwang, Myoung Su Yang\*, and In Byeong Kang\*

#### Abstract

In this paper, we investigated the SLS process to control grain boundary(GB) location in TFT channel region, and it has been found to be applicable for locating the GB at the same location in the channel region of each TFT. We fabricated TFT by applying a new alignment SLS process and compared the TFT characteristics with a normal SLS method and the grain boundary location controlled SLS method. Also, we have analysed degradation phenomena under hot carrier stress conditions for n-type LDD MOSFETs.

Keywords: Poly-Si, SLS crystallization, Grain boundary

#### 1. Introduction

Polycrystalline Silicon thin-film transistors(poly-Si TFTs) have been very arrractive for the integration of driver circuit into microelectronic applications such as active matrix liquid crystal displays(AMLCDs) and organic light-emitting diodes(OLEDs). In order to improve the TFT device performances, various crystallization techniques have been proposed. SLS(Sequential Lateral Solidification) has attracted a considerable attention due to its excellent throughput and high field-effect mobility.[1, 2, 3, 4, 5]

However, using the SLS to fabricate OLED devices, grain boundary(GB) location in channel region varies between the TFTs and it results an image quality deterioration of the panel. Therefore, grain boundary location control in channel region is an important factor to conisder in order to improve the uniformity and performance of the TFTs, which enhances the image quality of the OLED panel.

In this work, we carried out a grain boundary location controlled SLS method by applying a new key recognition alignment crystallization and it is possible to locate the GB at the same position in the channel region of each TFT.

Manuscript received November 16, 2007; accepted for publication December 25, 2007.

Corresponding Author: Sang Jin Lee

LGPhilips LCD Inc. LG R&D Center, 533 Hogae-dong, Dongan-gu,

Anyang-shi, Gyongki-do, 431-080, KOREA

E-mail: wernerlee@lgphilips-lcd.com Tel: 031-450-7494 Fax: 031-450-7408

#### 2. Experiments

#### Process I

Top gate n-channel poly-Si TFTs were fabricated on SiO2/SiNx (300 nm/100 nm) which was stacked as a buffer layer on NEG glass substrate. A 50 nm-thick amorphous silicon was deposited on the buffer layer by plasma enhanced chemical vapor deposition (PECVD) as the precursor to laser crystallization. Precursor was dehydrogenated in furnace at 430°C. Then, alignment process keys were formed on an amorphous silicon layer by photolithography at each corners of the glass substrate. This was the first photo-lithography layer and following processes were aligned with these keys. After that, SLS crystallization (2-shot process) was carried out.

#### Process II: Key alignment SLS process

In the normal SLS crystallization method, we just perform a basic substrate pre-align on the stage and apply a whole substrate area scan. After we complete all the TFT fabrication processes, each TFT has different GB location in channel region. The number of grain boundaries in the channel also varies from one to two, which can cause non-uniform TFT characteristics and image quality deterioration of the panel. This is because the tilt between the grain boundary and the following gate line cannot be aligned well when applying the normal SLS crystallization method. Therefore, we carried out a grain boundary location controlled SLS method in this work by applying a new key

<sup>\*</sup> Member, KIDS

recognition alignment crystallization which is possible to locate the GB at the same position in the channel region of each TFT.

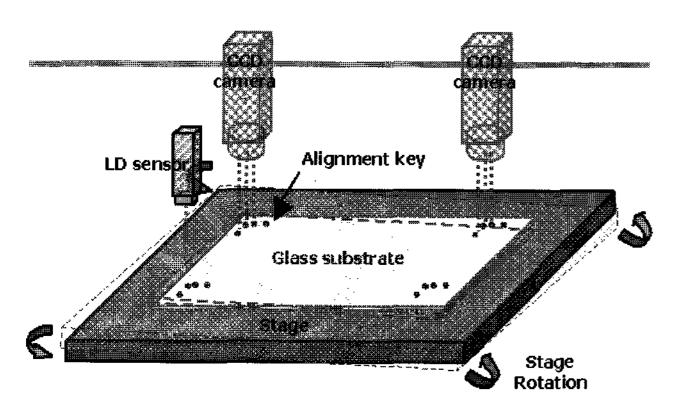

Fig. 1. shows a concept of a new key alignment SLS process. It was preformed as follows: 1) Glass is loaded onto a substrate stage. 2) Laser diode sensors detect loaded glass edges and calculate the right stage angle. 3) Stage rotates slightly to the calculated angle.(paralleled to substrate scan direction) 4) CCD cameras search alignment process keys on the glass substrate and system calculates the angle and perform a slight rotation to a correct scanning angle. 5) Whole substrate area laser scanning is performed. This new method of key alignment SLS process enables grain boundary to be aligned more finely to following gate lines so it can be advantageous to have more uniform grain boundary location. If we apply an offset value from the start position of line scanning, we can control the exact location of the grain boundary.

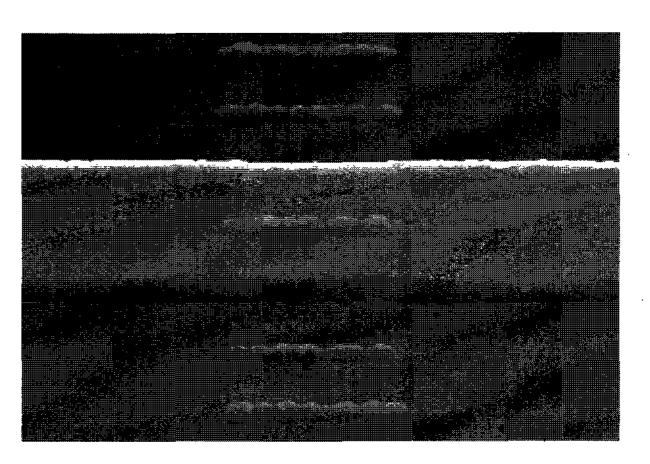

Fig. 2. shows a top view of SEM image(tilted) of TFT channel region with two grain boundaries located. The change in the GB location can affect TFT performances. Using the grain boundary location controlled SLS method, we have crystallized and fabricated poly-Si TFTs with only one grain boundary located at the same position in channel region at a same gate line.

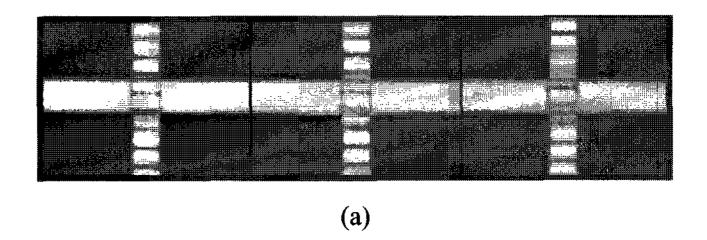

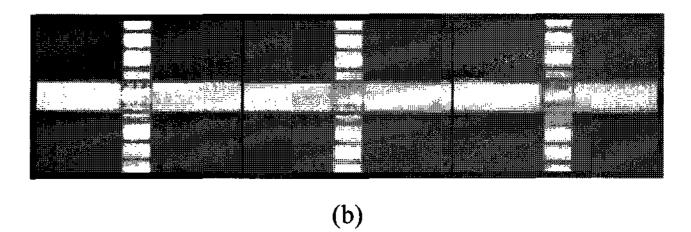

Fig. 3. shows continuous optical images of grain boundary within TFT channel region on the same gate line. As shown in the optical image, there is a change in the grain boundary location within channel region in case of normal SLS crystallization method (a) however, when we apply the grain boundary location controlled SLS method there is no change in grain boundary location within channel region at the same gate lines (b).

Fig. 1. Conceptual image of new key alignment SLS process

Fig. 2. Top view SEM image(tilted) of TFT channel region of one grain boundary located

Fig. 3. Optical images of TFT channel (a) when normal SLS crystallization method was applied and (b) when the new alignment SLS crystallization method was applied

## Process III

After laser crystallization, active layer was patterned. Gate insulator(SiO<sub>2</sub>) of 75nm and gate metal(Mo) of 300nm were deposited and patterned. Doping process was carried out in the source and drain region. The source and drain doping concentration was  $3x10^{15}$ cm<sup>-2</sup> for n-type TFT. LDD (Lightly Doped Drain) structure was adopted to reduce the high electric field in the fringe of the drain junction of the poly-Si TFT. Additional nitride(SiNx) layer was deposited for hydrogen passivation. Source and drain metal(Al) of 500nm and ITO were deposited and patterned.

### 3. Results and discussion

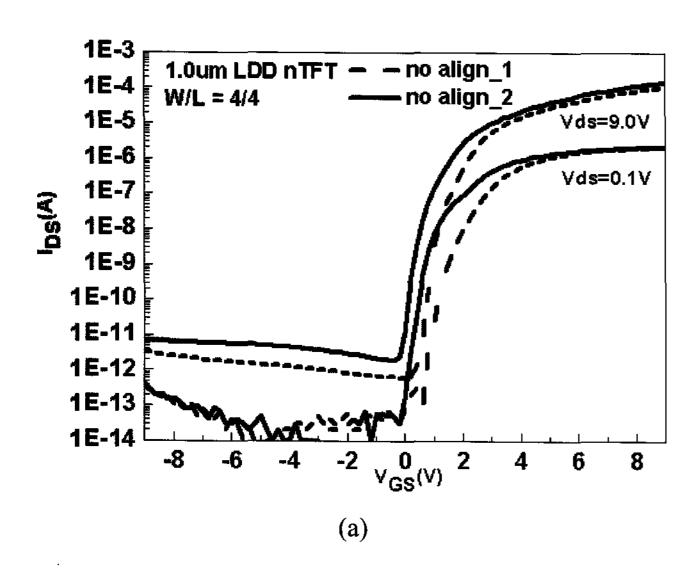

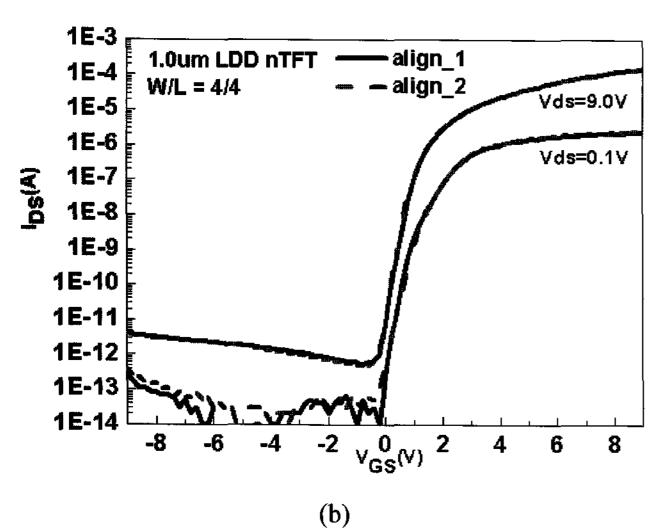

The transfer characteristics of TFTs were measured at room temperature with Vds=0.1 V and Vds=9.0 V, where the gate voltage(Vg) varied from -9.0 to +9.0 V. We measured TFT characteristics of 1.0 \mu LDD (Lightly Doped Drain) n-type TFT(channel width(W)/length(L)= 4\mu m/4\mu m)

Fig. 4. shows Id-Vg transfer characteristics of TFTs crystallized with normal SLS crystallization method. As shown in the transfer curves, when we applied the grain boundary location controlled SLS method, the TFT characteristic showed more uniform performances than with the normal crystallization process. The Vth uniformity was improved from 35% to 7%.

Fig. 4. 1.0 \( \mu\text{LDD} \) (Lightly Doped Drain) n-type TFT device transfer characteristics

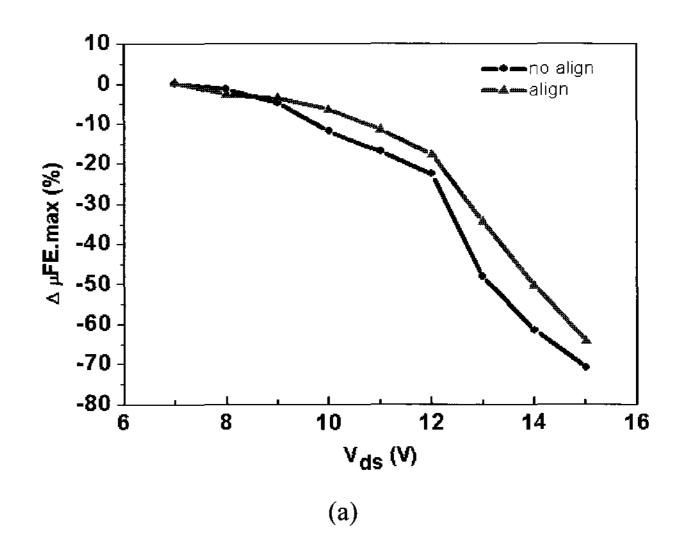

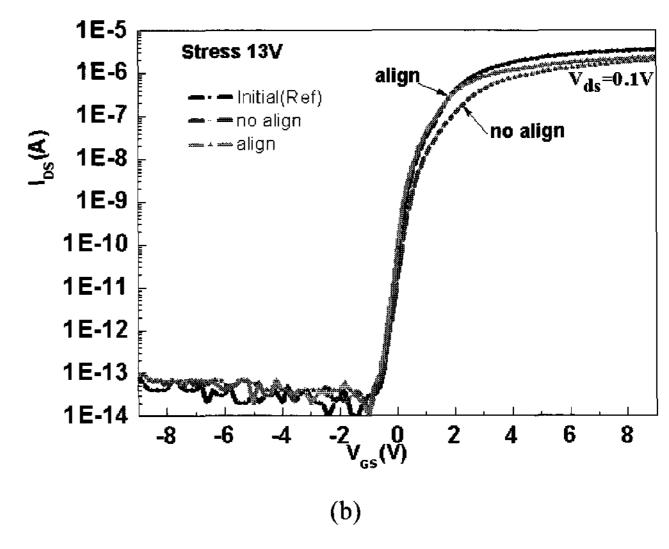

In order to examine the alignment crystallization effects on the TFT reliability characteristics, we measured hot carrier stress(HCS) device performances. Figure 5. shows the comparison of mobility degradation under hot carrier stress as a function of applied Vds with stress duration of 60 sec and n-type TFT transfer characteristics after stress Vds=13V. HCS characteristics of applying the new align method also showed better result than normal crystallization process. As shown in Fig. 5 (a), when we applied the grain boundary location controlled SLS method, the Δmobility was decreased about 28% compared with normal process at Vds=13V. In case of applying the grain boundary location controlled SLS method, we found that Ion characteristic was higher than the TFT with normal process after

Fig. 5. Comparison of (a)mobility degradation under hot carrier stress and (b)n-type TFT transfer characteristics after stress  $V_{ds}$ =13V

hot carrier stress(Fig. 5(b)). Therefore, we came to the conclusion that the grain boundary control in the channel region is an important factor to improve the uniformity and reliability of TFT characteristics. As a result, we have accomplished more uniform TFT characteristics than conventional poly TFT by applying the grain boundary location controlled SLS method.

# 4. Conclusions

We fabricated a poly-Si TFT using a grain boundary location controlled SLS method by applying a new key recognition alignment crystallization. In this way, it is possible to locate the grain boundary at the same position in the channel region of each TFT. When we applied the grain boundary location controlled SLS method, the TFT characteristic showed more uniform performances than the TFT with normal SLS crystallization process. The Vth uniformity was improved from 35% to 7%, and also Δmobility characteristic was decreased about 28% at Vds=13V

condition. In conclusion, we have accomplished more uniform and reliable TFT characteristics than conventional poly TFT by applying the grain boundary location controlled SLS method. Also, it can be said that control of grain boundary location is an important factor for the image quality of the panel.

### References

- [1] P Mark A. Crowder, A. Tolis Voutsas, Steven R. Droes, Masao Moriguchi and Yasuhiro Mitani, IEEE Transactions on ELECTRON DEVICES, VOL. 51, NO. 4, APRIL 2004

- [2] Y. J. Kim, K. S. Hwang, Y. I. Park, S. W. Lee, H. C. Kang,K. M. Lim, C. D. Kim and I. J. Chung, AMLCD 05, 249 (2005)

- [3] L. Mariucci, A. Pecora, R. Carluccio and G. Fortunato, Thin Solid Films 383, 39 (2001)

- [4] G. A. Armstrong, S. Uppal, S. D. Brotherton and J. R Ayres, Jpn. J. Appl. Phys. Vol. 37 1721 (1998)

- [5] A. Bonfiglietti, A. Valletta, P. Gaucci, L. Mariucci and G. Fortunato, S. D. Brotherton, JOURNAL OF APPLIED PHYSICS 98, 033702 (2005)