# Binary CDMA를 기반으로 하는 Koinonia 시스템의 모뎀 설계

강성진 책임연구원 전자부품연구원 통신네트워크연구센터 (sikang@keti,re,kr)

홍대기 전임강사\_상명대학교 정보통신공학과 (hongdk@smu,ac,kr)

이현석 선임연구원 전자부품연구원 통신네트워크연구센터 (hslee75@smu.ac.kr)

조진웅\_ 수석연구원\_전자부품연구원 통신네트워크연구센터 (chojw@keti.re.kr)

# 1. 서론

인터넷 사용자가 급증하면서 기기간의 정보공유를 가능케 하기 위한 '근거리 무선 네트워크' 기술이 급부상하고 있다. "Anytime, Anywhere" 를 모토로 한 근거리 무선 네트워크 기술은 기기간의 상호 연동성과 외부 망과의 연동성이 제공되는 서비스를 효과적으로 운용할 수 있는 시스템이 어야 한다. 현재 주로 사용되는 IEEE 802.11/15 계열 표준, Bluetooth, HomeRF 등 근거리 통신에 적용 되어온 기술들은 다음과 같은 문제들로 인해 보급이 지연되고 있는 실정이다.

- 첫째, 사용자가 증가하면서 사용자간 상호 간섭의 영향으로 모든 사용자들의 전송 품질이 저하된다.

- 둘째, 만일 다수의 디바이스가 접속하여 화상회의 및 음성통화를 수행하면 영상 및 음성 데이터가 끊기는 등 각 서비스별 QoS(Quality of Service)를 보장하지 못하는 문제가 발생한다.

- 셋째, 다양한 무선 액세스 포인트의 증가로 액세스 포인트 간의 주파수 배정 문제가 발생한다.

이러한 문제들을 효율적으로 해결할 수 있는 방법 중 하나는 CDMA (code division multiple access) 기술을 이용하는 것이다. CDMA를 이용한 고속의 데이터 전송기술로는 여러 개의 병렬 브랜치의 다중 코드를 사용하는 Multi-Code CDMA 시스템이 가장 보편적인 것으로 알려져 있다. 이 기술은 확산 이득이 변화가 없고 대역폭의 증가가 없다는 장점이 있지만 다중 레벨의 신호를 증폭하기 위한 앰프의 선형성을 보장하여야 하므로 구조가 복잡하고, 전력 소모가 많고, 가격이 높아 근거리 무선통신 기기에 적용하기에는 많은 문제가 있다.

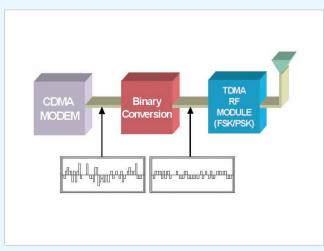

이러한 문제들을 해결하기 위해 Binary CDMA (BCDMA) 무선 PAN (Personal Area Network) 기술이 제안되었는데, 〈그림 1〉에 나타나 있듯 기존의 다중 코드 CDMA 방식에 의해 발생되는 다양한 레벨의 변조신호를 이진화 하여 외형적으로 TDMA 신호 파형으로 만들어 전송하므로 구조의 복잡성, 높은 가격, 높은 전력소모 등의 현존하는 문제들을 해결할 수 있는 근거리 통신기술의 해결 방안이 될 수 있다. BCDMA 기술을 이용하는 무선 PAN 기술 표준의 별칭을 Koinonia라고 한다. 본 기고에서는 2장에서 BCDMA 시스템을 이용하는 Koinonia 시스템의 물리층 표준에 대해 알아본다. 그리고 3장에서는 Koinonia 표준을 FPGA (Field Programmable Gate Array)로 구현하는 방법에 대해 소개한다. 이어서 4장에서는 Koinonia SOC (System On Chip) 기술에 대해 설명하며, 마지막으로 5장에서는 결론을 맺는다.

〈그림 1〉 BCDMA 개념도

#### 2. Koinonia 시스템의 물리층 개요

BCDMA 기술을 기반으로 하는 홈 네트워크의 표준을 목표로 Koinonia 시스템이 제안되었다. 본 절에서는 특히 Koinonia 시스템의 물리 계층을 위주로 설명하도록 한다.

#### 2.1 주파수 대역 및 패킷 형식

2.4-2.4835 GHz의 ISM (Industrial, Scientific, and Medical) 대역을 사용하는데 전체 10개의 대역으로 구성되며, 각각의 주파수 대역폭은 7.2MHz이고 전송 속도는 6.2MHz이다. 물리 계층 패킷의 형식은 〈그림 2〉 에 나타나 있는데, 패킷의 LSB (Least Significant Bit)비트부터 송·수신 이 이루어진다. 같은 순서의 송·수신이 물리 계층과 MAC (Medium Access Control)계층간에 적용된다.

〈그림 2〉 물리 계층 패킷 형식

#### 2.2 정진폭 신호 변환 방식

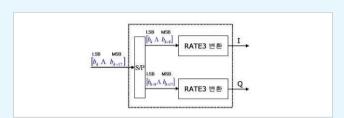

정진폭 신호 변환 방식은 총 4가지로 나뉘는데, 4가지의 방식은 각각 RATE i, i∈{1,2,3,4},이며 서로 다른 전송률을 지원할 수 있다. 그 중 RATE 1, RATE 2, RATE 3은 I/Q (Inphase/ Quadrature) 채널에 동일한 데이터를 전송하고, RATE 4는 I/Q채널에 서로 다른 데이터를 보내 채널의 효율을 높인다.

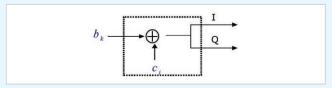

먼저 RATE 1은 일반적인 대역 확산 변조 방식과 유사하다. 〈그림 3〉에 도시된 바와 같이 데이터가 입력되면 확산 이득 16인 왈쉬 코드가 곱해져 서 원래 데이터의 대역폭보다 넓어진 확산 신호가 만들어 진다.

〈그림 3〉 RATE 1의 블럭도

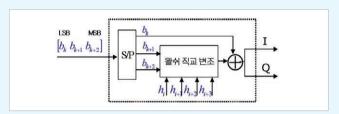

RATE 2는 이진 직교 변조 방식을 사용한다. (그림 4)에 도시된 바와 같이 정보 데이터 3비트 중 2비트는 4개의 직교 코드 중 하나를 선택하고 선택된 코드는 나머지 1비트와 곱한다.

〈그림 4〉 RATE 2의 블럭도

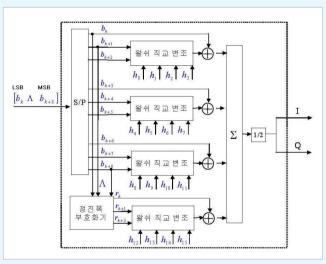

RATE 3은 RATE 2 블록을 확장한 형태로 한번에 9비트를 전송할 수 있다.

〈그림 5〉 RATE 3의 블럭도

〈그림 5〉에 도시된 바와 같이 이진 직교 변조 블록 4개를 사용하는데 그 중 3개는 입력되는 정보 9비트를 각각 3비트씩 변환하고 나머지 한 블록은 정보 9비트로부터 정진폭 출력을 위해 다음의 식을 통해 변환한다.

$$egin{aligned} r_k &= \overline{b_k \oplus b_{k+1} \oplus b_{k+2}} \ r_{k+1} &= b_{k+3} \oplus b_{k+4} \oplus b_{k+5} \ r_{k+2} &= b_{k+6} \oplus b_{k+7} \oplus b_{k+8} \end{aligned}$$

이때. 4개의 블록으로부터 나온 신호의 합이 ±2이므로 1/2로 나누어 변 조부에 전달한다. RATE 4는 〈그림 6〉에서처럼 I/Q에 각각 다른 데이터를 변조하므로 전송률은 RATE 3에 비해 2배 높다.

〈그림 6〉 RATE 4의 블럭도

#### 2.3 패킷 각 부분의 변조 방법

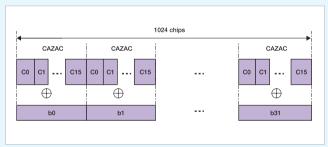

먼저 프리앰블 신호는 수신단에서 프레임 동기, 심벌 시간 조정 등의 목적으로 사용한다. 32 비트의 프리앰블 수열 [bx]을 주기 16인 CAZAC (Constant Amplitude Zero Autocorrelation Code) 수열 [Cx]로 확산해만들어진 512개의 심벌로 이루어진 프리앰블은 I/Q 채널에 각각의 신호를 구성하며 그 구조는 〈그림 7〉과 같다.

〈그림 7〉 프리앰블 수열의 구조

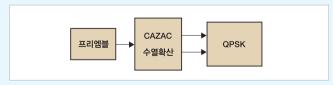

최종적으로 확산된 신호는 〈그림 8〉에서와 같이 QPSK에 의해 변조되어 전송된다.

〈그림 8〉 프리앰블 변조

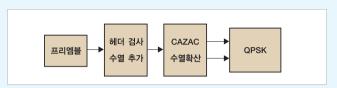

두 번째로 헤더는 총 24비트의 정보를 CAZAC 수열 확산해 전송하는데, I/Q 채널에 같은데이터를 전송한다. 먼저 순수 헤더 정보 16비트에 헤더 검사 수열 8비트를 추가하고 CAZAC 수열 확산을 이용해 I/Q 신호를만들어 〈그림 9〉와 같이 QPSK를 이용해 전송한다.

〈그림 9〉 헤더 변조

마지막으로 페이로드는 실제 데이터 부분과 프레임 검사 수열 32비트로 이루어지는데 RATE i, i(1,2,3,4), 중 하나를 선택한다.

〈그림 10〉 페이로드 변조 방법

#### 3. Koinonia 시스템의 데이터 링크 계층 개요

Koinonia 시스템의 데이터 링크 계층은 매체접근 부계층과 Adaptation 부계층으로 이루어져 있다.

#### 3.1 매체접근 부계층

Koinonia의 데이터 링크 계층에서는 물리계층인 Binary CDMA의 특성을 살려 코드와 시간슬롯의 조합을 통해 매체접근을 하는 HMA(Hybrid Multiple Access) 방식을 사용하고 있다. Koinonia는 슈퍼프레임이 반복되는 구조로 이루어져 있으며, 하나의 슈퍼프레임은 비콘구간, 경쟁구간, 할당구간으로 나누어진다.

- 1. 비콘 구간: 마스터가 비콘을 통해 피코넷에 속한 슬레이브들에게 피코 넷의 상황 및 할당구간에서의 자원할당상황을 알려준다. 이와 같은 네트 워크 기준정보를 이용하여 슬레이브들은 마스터에 동기되어 피코넷 상황 을 공유하게 된다.

- 2. 경쟁 구간: 슬레이브와 마스터가 네트워크 합류요청/분리요청/허용, 자원 할당, 연결 그리고 인증 요청/허용 등의 명령 패킷을 임의 접근 경쟁 방식(CSMA/CA)으로 전송한다.

- 3. 할당 구간 :여러 개의 시간 슬롯으로 나뉘어지며, 각각의 스테이션에게 시간 슬롯 단위로 할당된다.

| 피코넷    | 프레임 | 송신 | 수신 | 스트림 | 일련    | 페이 | 프레임오류 |

|--------|-----|----|----|-----|-------|----|-------|

| ID     | 제어  | 주소 | 주소 | ID  | 번호    | 로드 | 확인번호  |

| 프레임 헤더 |     |    |    |     | 프레임바디 |    |       |

2B | 2B | 1B | 1B | 1B | 가변적 |

〈그림 11〉 일반적 프레임 구조

Koinonia의 가장 큰 특징 중 하나는 잡음이 많은 무선 환경에서도 QoS를 보장하는 것이다. 먼저, Koinonia가 사용하는 물리계층인 Binary CDMA 기술이 잡음에의 대응이 뛰어나다. 그리고 채널내에 잡음이 많아지는 경우 그에 따라 코드 할당수를 조정하는 동적 자원 할당이나 분할되는 패킷의 길이를 조정하는 분할(Fragmentation)가능을 지원한다.

Koinonia 시스템의 모든 패킷은 〈그림 11〉의 일반적 패킷 구조를 따르며, 패킷의 종류별로 다른 형태의 프레임 헤더 및 프레임 바디를 가진다. Koinonia 시스템에 정의된 프레임의 종류는 모두 4가지로, 비콘 프레임, 명령 프레임, 수신확인 프레임, 데이터 프레임이 있다. 그중에 수신확인 프레임은 프레임 바디없이 프레임 헤더로만 이루어진 구조를 가지고 있다.

#### 3.2 Adaptation 링크 부계층

Koinonia는 하위의 프로토콜 스택과 상위의 다른 무선 표준의 프로토콜 스택을 호환해 주는 역할을 하는 Adaptation 부계층을 통해, Bluetooth 등과 같은 타 무선 표준 어플리케이션이 Koinonia에서도 사용될 수 있도 록 지원한다.

### 4. Koinonia 시스템의 FPGA 구현

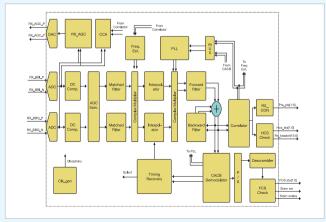

〈그림 12〉 Koinonia 시스템 복조기의 블록도

#### 4.1 물리층 복조기의 FPGA 구현

〈그림 12〉는 복조기의 전체 블록도이다. 이 복조기는 DC 편차제거기, 자동이득제어기, 정합필터, 보간기, 심볼타이밍 복원기, 결정궤환등화기, PLL, 주파수 추정기, CAZAC상관기, 정진폭복호기, HCS, FCS등등으로 나뉠 수 있다.

먼저 ADC는 성능과 복조기의 복잡도를 고려하여 칩레이트의 두 배로 동작하도록 한다. DC편차 제거기는 ADC입력 바이어스와 RF모듈간의 바이어스가 서로 맞지 않아서 발생하는 DC 성분을 제거한다. DC편차는 RF모듈의 바이어스가 조금씩 변하기 때문에 추적기능이 가능하도록 설계한다. DC성분이 제거된 신호을 이용하여 자동이득제어를 하는데, 복조기가 RF모듈의 전력증폭기와 디지털 곱셈기를 제어하여 복조기의 입력신호레벨이 동작 가능할만한 신호레벨로 근접할 수 있도록 해준다. RF모듈의 전력증폭기는 RF칩마다 다르나, 통상 6비트 디지털 입력이나, 0~2V의 아날로그 전압으로 제어한다. 6비트 디지털 입력은 1bit당 0.5~1dB씩 떨어지게되므로 정확히 맞출 수는 없다. 따라서 RX\_AGC는 Coarse AGC로 동작하게 되고, AGC는 Fine AGC로 동작한다.

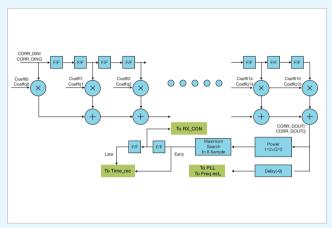

보간기는 심볼 타이밍 복원기에서 제어된 Early-Late정보를 이용하여 보간기의 계수값을 조정함으로써 입력샘플사이의 중간 값을 출력한다. 보 간기는 샘플링 레이트보다 8배 빠르게 보간한다. 그러므로 보간기의 분해 능은 Tc/16이 될 것이다. 보간기의 종류도 많지만 성능과 복잡도를 고려하 여 roll-off factor가 0.3인 49탭 Raised Cosine filter를 사용한다. 보간기 는 탭 수가 상당히 크지만 샘플링속도에 동작하기 때문에 49/8 탭 = 6탭 으로 간단히 해결할 수 있으며, 보간은 6탭의 계수 값만을 조정함으로써 간 단히 해결할 수 있다. 보간기의 계수 값을 조정하기위한 정보는 심볼타이밍 복원기에서 받게 되는데. 심볼타이밍 복원은 CAZAC상관기와 CAMCB복 호기에서 Early/Late 상관정보를 이용한다. CAZAC상관기는 Tc/2로 동작 하게 되어 있으며, 상관 Power값의 Peak치를 이용하여 프레임동기에 이 용하고 Peak 시간보다 반칩 빠르거나 느린 상관 Power값을 이용하여 심 볼 타이밍 복원에 적용시킨다. 심볼 타이밍이 정확히 맞으면 Early와 Late 상관값은 거의 동일한 값이 나온다. CAZAC 상관기는 〈그림 13〉과 같이 16탭 복소 FIR 필터로 구성된다. 상관기가 Early/Late 상관값을 추출할 수 있도록 샘플링속도에 맞춰 동작하도록 Tap 사이에 F/F을 추가한다. 곱셈 기는 덧셈기와 Mux로 구현한다.

주파수 편차와 위상편차가 있는 신호를 CAZAC 상관기에 입력시키면 상관기출력이 I성분과 Q성분으로 나눠진다. 상관값의 위상성분은 주파수 판정기과 PLL에서 사용할 수 있다. PLL이 추적하다보면 Phase ambiguity 때문에 위상이  $\pi/2$ ,  $\pi$ ,  $3/2\pi$ 로 위상회전이 될 수 있다. 이러한 문제는 RX\_CON블럭에서 Phase Rotator을 이용하여 해결해야 한다.

〈그림 13〉 CAZAC 상관기 블록도

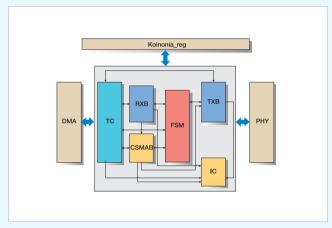

#### 4.2 매체접근 제어 부계층의 FPGA 구현

MAC 하드웨어 블록은 아래 〈그림 14〉와 같다.

송신하는 경우 DMA가 버스 마스터로 동작을 하면서, 지정된 위치의 메모리에서 송신할 데이터를 읽어서 dma\_if 블록으로 보내게 된다. dma\_if 블록에서는 암호화 과정을 거쳐서 PHY에서 데이터를 요구하면 데이터를 PHY블록에 제공하게 된다. 그런 다음 PHY에서는 MAC에서 지정한 변조 방식을 사용하여 데이터를 송신하게 된다.

수신하는 경우에는 PHY 블록에서 받은 데이터를 dma\_if 블록에서 받아 서 암호화 과정을 거쳐 DMA 블록으로 데이터를 보내게 된다. 이와 동시에 DMA 블록은 버스 마스터로 동작하면서 지정된 수신 메모리 위치에 데이 터를 저장하게 된다.

- 1. FSM 블록: MAC 하드웨어의 상태 천이를 관리하며 다른 MAC 하드웨 어 블록을 전체적으로 제어한다.

- 2. TC 블록: MAC에서 정의한 슈퍼프레임 구조를 지원하기 위해서 필요한 여러 종류의 타이머와 동기화를 처리한다.

- 3. RXB 블록: 데이터 수신과 이와 관련된 데이터 필터링, 즉시수신확인 프레임 송신 등의 일련의 동작들을 처리한다.

- 4. TXB 블록: 데이터 송신과 즉시 수신확인 프레임 수신등의 일련의 동작 들을 처리한다.

- 5. CSMA 블록: 경쟁구간에서 사용하는 임의 경쟁방식인 CSMA/CA를 구현하기 위해서 Carrier Sensing, 백오프 과정등을 처리한다.

- 6. IC 블록: MAC 하드웨어와 소프트웨어의 기본 통신 수단인 인터럽트를 처리한다.

〈그림 14〉 MAC 하드웨어 블록도

#### 5. Koinonia 시스템의 SoC 구현

#### 5.1 시스템 구조 및 특징

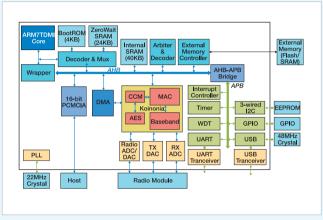

SoC 플랫폼의 형태는 완전 응용 플랫폼, 프로세서 중심 플랫폼, 통신 중심 플랫폼 그리고 프로그램이 가능한 플랫폼으로 분류된다. 본 고에서는 그중, 기본적인 소프트웨어 드라이버와 기본 응용 루틴이 지원되는 프로세서 중심 플랫폼으로 설계하였다. 〈그림 15〉는 SoC 플랫폼의 블록도이며, 보는 바와 같이 ARM/AMBA 기반으로 구성되었다. ARM/AMBA 플랫폼은 SoC 내부 모듈들을 위한 공통 시스템 버스를 정의함으로써, 선택 사항에따라 쉽게 플랫폼을 구성, 변경할 수 있으며 재사용을 강화시키는 장점을 제공한다. ARM/AMBA 플랫폼의 프로세서로는 저전력 내장형 RISC ARM/TDMI 코어를 사용하였으며, AHB 시스템 버스와 APB 주변 장치 버스를 적용하였다.

ARM7TDMI는 AHB Wrapper를 통해서 AHB 버스에 연결된다. 〈그림 15〉에서 보는 바와 같이 ARM7TDMI는 내부 메모리와 로컬 버스를 통해서 도 연결이 된다. 따라서 AHB 시스템 버스는 시스템 내의 각 하드웨어에 의해 통신 데이터를 처리하는데 할당되므로 전체 시스템의 성능을 향상시킬 수 있다.

AHB 버스는 AHB 버스의 마스터를 결정하는 Arbiter, 메모리영역을 디코딩하기 위한 어드레스 디코더, 프로그램 코드와 데이터를 저장하기 위한 내부 메모리, 외부 메모리의 내용을 내부 메모리에 매핑하기 위한 External Memory Interface(EMI) 등으로 구성된다. BCDMA 기술을 채택한 Koinonia 모뎀은 AHB 슬래이브로 연결하였다. 그리고 Koinonia 모뎀과

〈그림 15〉 SoC 블록도

메모리 사이에 빈번한 데이터 전송을 효과적으로 제어하기 위하여, 버스 마스터로 DMA가 있다. 또한 본 시스템이 컴퓨터의 서브 시스템으로 사용될 수 있도록 16-bit PCMCIA 슬래이브 모듈을 지원한다.

APB Bridge는 AHB 버스와 APB 버스를 연결하는 인터페이스 모듈이다. APB 버스에는 비교적 저속의 블록들이 연결된다. Timer와 Watch-Dog Timer(WDT)의 인터럽트 신호 발생 간격은 ARM 프로세서가 설정할수 있게 하여 활용성을 높였다. 외부 호스트와의 통신을 위하여 USB 1.1 및 16C550 Compatible UART를 APB 슬래이브로 구성하였다. 그 외에도 ARM 프로세서에 하드웨어 인터럽트를 발생시키는 인터럽트 컨트롤러, 외부 EEPROM과의 통신을 위한 3-wire Serial Interface, 그리고 사용자인터페이스를 위한 8-bit GPIO가 있다.

내부 4KB ROM에는 부트 코드가 저장되어 있어 시스템 전원이 켜질 때 실행될 수 있으며, 이후에 PCMCIA를 통하여 호스트에서 프로그램을 다운로 드해 주어야 한다. 뿐만 아니라 본 시스템은 EMI에 연결되어 있는 외부 메모 리에서 시스템 부트 코드가 실행되는 경우를 지원한다. 이때는 EMI에 Flash 메모리를 연결하고 부트 코드 및 다운로드 코드를 저장해 놓으면, 필요에 따라 프로그램을 다운로드 할 수 있어 시스템의 활용도를 높일 수 있다.

시스템 클럭은 칩 내부 PLL이 22MHz 신호를 입력으로 받아서 시스템 클럭모드에 따라 44MHz 또는 88MHz로 증배한 후 2분주(22MHz, 44MHz)하여 사용한다. 시스템 동작 중에도 필요에 따라 PLL의 클럭 증배율을 재설정할 수 있다.

본 시스템에는 3가지 파워 모드 - RUN, HALT, SLEEP-가 있다. RUN 모드에서는 시스템의 모든 블록이 동작을 한다. HALT 모드에서는 ARM 코어의 클럭이 다운된다. 그리고 SLEEP 모드에서는 SLEEP 모드 타임 아 웃 카운터를 제외한 모든 블록이 다운된다. 이 타임 아웃 카운터에 의해 미 리 설정해 둔 시간 이후에 RUN 모드로 전환되거나 혹은 PCMCIA 인터페이스를 이용하여 외부 호스트에서 원하는 시점에 전환될 수 있다.

#### 5.2 Koinonia

BCDMA 기술을 기반으로 하는 Koinonia 시스템은 크게 MAC과 PHY 블록으로 구성된다. 데이터의 흐름에서 가능한 한 프로세서의 부담을 덜어주기 위하여 DMA를 사용하였을 뿐 아니라 MAC의 일부 기능을 하드웨어로 설계하였다. 특히 MAC의 상태 (송신, 수신, IDLE, 비콘구간, 경쟁구간) 천이 관리, 정확한 타이밍을 요하는 슈퍼프레임 동기화, 데이터 송/수신, 즉시 수신 확인 프레임 송/수신 그리고 경쟁구간에서 사용하는 CSMA/CA프로토콜을 처리 등이 이에 포함된다. 전력소모를 줄이기 위해 Idle 모드를 사용하며 암호화를 지원한다.

PHY 블럭은 다시 송신부와 수신부로 구분되는데, 송신부는 Frame Generation 블록과 Preamble을 확산하는 CAZAC spreader, 32—bit 검사 수열을 추가하고 스크램블링을 거친 Payload 데이터를 정진폭 신호로 변화하는 CACB Modulator 그리고 QPSK 변조기로 구성된다. PHY에서는 데이터율, 요구되는 QoS 그리고 현재 채널 상태에 따라 687.5 Kbps에서 12.375 Mbps 까지 4가지의 서로 다른 전송율을 지원한다.

수신부의 아날로그 입력신호는 ADC를 거쳐 8비트의 디지털 신호로 변환이 되어, DC compensation 블록을 거치면서 DC offset이 보정된다. AGC에 의해 신호레벨이 일정해진 수신신호는 Roll-off Factor가 0.3인 Matched filter(Square Root Raise Cosine filter)을 거친 후 원하는 Symbol을 추출하기 위해 Interpolation이 된다. Frequency Estimation은 Preamble 구간에 존재하는 Carrier 성분의 CAZAC의 correlation 특성을 이용하여 수신 데이터에서 Carrier 성분을 제거하고, 여기서 발생한 오차 성분의 잔여 Carrier와 위상 업셋은 DFE와 PLL이 추적하여 제거한다. DFE는 채널에서 발생한 Multipath성분을 제거한다. Correalator는 CAZAC despreader로써 기저대역 신호에 존재하는 Carrier을 제거하거나 Early-Late 알고리즘의 타이밍 복원을 위해 사용된다. CACB Demodulator에서 정진폭 변환 방식에 의해 변환되었던 데이터가 복원된후 Descrambler와 FCS를 거쳐 MAC으로 최종 데이터가 전달된다.

본 칩에는 수신된 In-Phase, Quadrature (I/Q) 신호를 처리하기 위한 8-bit 22MHz dual-channel ADC와 전송할 I/Q 신호를 위한 8-bit 44MHz dual-channel DAC가 포함되어 있다. RF의 송수신 파워를 제어하는 AGC는 TxAGC와 RxAGC로 구성된다. TxAGC의 2MHz ADC에서 TX Power Sense 레벨을 검출한 뒤, 8-bit 10MHz DAC를 이용하여 송신 신호의 파워를 조절한다. RxAGC는 8-bit 10MHz DAC를 이용하여, RF의 수신 Gain을 조절함으로써 수신부가 검출 가능한 ADC 입력 레벨을 갖도록 한다.

〈그림 16〉 테스트 보드

#### 5.3 설계 방법 및 결과

SoC 플랫폼을 결정하기 위하여 Koinonia 시스템의 요구사항을 분석하였다. 즉, C와 Matlab을 이용하여 Koinonia MAC과 PHY 알고리즘을 검증한 뒤 MAC의 하드웨어 부분과 소프트웨어 부분을 구분하였다. 이를 바탕으로 ARM Core의 종류, 메모리와 버퍼의 구조 및 크기를 결정하였으며, 무선 통신 시스템으로서 활용하는데 필요한 주변 장치들을 선정하여 플랫폼을 구성하였다. 하드웨어는 Verilog 및 VHDL로 기술하였고, 소프트웨어

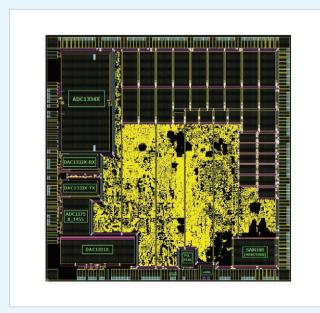

〈그림 17〉 SoC 레이아웃 도면

는 HDL 메모리 모델에서 사용 가능한 형태로 컴파일을 하여 ARM/TDM HDL 시뮬레이션 모델과 함께 통합 시뮬레이션을 하였다. 이를 다시 FPGA와 ARM/TDMI를 탑재한 테스트 보드에 올려 전체 시스템을 검증하였다. 제작된 보드는 〈그림 16〉과 같으며, RF 모듈도 포함하고 있어 실제적인 무선 데이터 통신 환경에서 에뮬레이션을 가능하게 하였다.

BCDMA SoC를 삼성 0.18um 6-metal CMOS 공정을 이용하여 칩으로 제작하였다. 〈그림 17〉은 PnR한 후 Apollo 툴에서 추출한 레이아웃 도면이다. ARM7TDMI 코어를 포함한 디지털 로직들과 USB 1.1, 16C550 Compatible UART, PLL, dual-channel ADC/DAC, 그 외 1개의 ADC, 2개의 DAC, 그리고 4KB ROM 및 64KB SRAM으로 구성되어 있다. 칩은 272핀 FBGA 패키징을 하였다.

본 칩과 RF 모듈이 탑재된 보드에 22MHz 시스템 클릭을 설정한 뒤 수백미터거리에서 단방향 통신시 평균 약 3.9Mbps의 데이터율을 얻었으며, 44MHz 시스템 클릭에서는 평균 약 7.2Mbps의 데이터율을 얻었다. 따라서 본 칩이 설계한 BCDMA 시스템 스펙을 만족함을 확인하였다.

## 6. 결론

본 논문에서는 홈 네트워크 시스템 분야에서 최근 이슈가 되고 있는 BCDMA 기술을 이용한 표준인 Koinonia 시스템의 모뎀 설계에 대해 논의하였다. 가장 핵심적인 블럭인 정진폭 다중 부호 이진직교 복조기는 게이트수와 복조기의 성능을 고려하여 간단한 16개의 가산기와 준 최적복조회로를 사용하였다. 이 변복조기는 FPGA을 이용하여 타겟팅한 후 보드실험을통해 설계에 대한 충분한 검증을 거쳐 ASIC칩으로 제작되었다. 이러한 12Mbps급 모뎀의 SoC를 위하여 ARMTDMI를 사용하였으며 64KB SRAM을 내장하였다. 16-bit PCMCIA, USB 1.1, 16C550 Compatible UART 등 다양한 통신 인터페이스를 지원할 뿐 아니라 ADC/DAC를 포함하고 있어 실제 현장에서 쉽게 활용될 수 있을 것으로 기대된다. 삼성 0.18um 6-metal CMOS 공정을 사용하였고, 272핀 FBGA 패키징을 하였다. 🖒

#### [참고문헌] --

- [1] 안호성, 류승문, 나성웅, "Binary CDMA 소개," JCCI, VI-A.1.1-4, April 2002.

- [2] 조진웅, 주민철, 서경학, 류승문 "WPAN 용 Binary CDMA기술"