# Schottky Barrier MOSFETs with High Current Drivability for Nano-regime Applications

Moongyu Jang\*, Yarkyeon Kim\*, Myungsim Jun\*, Cheljong Choi\*, Taeyoub Kim\*, Byoungchul Park\*\*, and Seongjae Lee\*

Abstract-Various sizes of erbium/platinum silicided n/p-type Schottky barrier metal-oxide-semiconductor (SB-MOSFETs) field effect transistors manufactured from 20µm to 10nm. The manufactured SB-MOSFETs show excellent DIBL and subthreshold swing characteristics due to the existence of Schottky barrier between source and channel. It is found that the minimization of trap density between silicide and silicon interface and the reduction of the underlap resistance are the key factors for the improvement of short channel characteristics. The manufactured 10 nm n-type SB-MOSFET showed 550µA/um saturation current at  $V_{GS}$ - $V_T = V_{DS} = 2V$  condition ( $T_{ox} = 5$ nm) with excellent short channel characteristics, which is the highest current level compared with reported data.

*Index Terms*—SB-MOSFETs, scaling, nanotechnology, high performance

### I. Introduction

Recently, silicide metallic junction-based electronic devices are being studied for the applications in nanometer regime as an alternative of conventional metal-oxide-semiconductor field-effect transistors (MOSFETs) [1-3]. In Schottky barrier MOSFETs (SB-MOSFETs), the source and drain are composed of silicide instead of impurity

doped silicon. Thus, the parasitic source and drain resistance can be efficiently reduced and the process temperature can be reduced dramatically (lower than 600 °C), giving the opportunity to use metal as gate electrode and high-K dielectric materials as gate insulator [1]. In SB-MOSFETs, most of the works are done in ptype transistors, using platinum-silicide because of its low Schottky barrier height (0.24 eV) for hole [2]. Recently, erbium-silicide is being considered as the candidate for the n-type SB-MOSFETs [2, 3]. The previous works reported the superior scaling characteristics of SB-MOSFETs in deep nano regime. However, the major drawback was the low current drivability in n-type SB-MOSFETs due to the high Schottky barrier height. The reported maximum saturation current was around 200 µA/um, which is too low compared with conventional MOSFETs [2, 3].

In this paper, various sizes of SB-MOSFETs are manufactured down to 10nm with 550 $\mu$ A/um saturation current at V<sub>GS</sub>-V<sub>T</sub>= V<sub>DS</sub>= 2 V condition (T<sub>ox</sub>= 5 nm). Also, the short channel characteristics of SB-MOSFETs are analyzed using DIBL and SS characteristics to check the scalability.

# II. EXPERIMENTAL

As a starting material, (100) n-type and p-type siliconon-insulator (SOI) wafers are used for the n-type and p-type SB-MOSFETs, respectively. SOI wafers are phosphorus and boron doped with a resistivity of 13.5-22.5  $\Omega$ ·cm. The thickness of the SOI and buried oxide (BOX) layer is 100 nm and 200 nm, respectively. The gate oxide is 5 nm thick SiO<sub>2</sub>, grown by thermal oxidation and the gate electrode is highly phosphorus doped n-type polycrystalline silicon. Electron-beam

E-mail: jangmg@etri.re.kr

Manuscript received Jan. 20, 2006; revised Mar. 5, 2006.

<sup>\*</sup> Nano-Bio-Electronic Devices Team, IT Convergence Technology Research Division, Electronics and Telecommunications Research Institute, Daejon 305-350

<sup>\*\*</sup> Department of Nano-science & Technology, Chungnam National University, Daejeon 305-764, Korea

lithography is employed to define gate pattern. After gate etching, 30nm thick gate sidewall spacer is formed by using thermal oxidation method. After blanket dry etching of gate sidewall spacer the remained spacer thickness is around 15 nm. After sidewall etching, 100 nm thick erbium and platinum are sputtered for n-type and p-type SB-MOSFETs, respectively. Erbium-silicide and platinum-silicide are formed by using rapid thermal annealing (RTA) technique. Annealing temperature and time is 500 °C and 5 min, respectively. The non-reacted erbium and platinum are removed by using SPM and aqua regia for 10 min, respectively. The detailed SB-MOSFETs manufacturing procedures are summarized in Table 1. The formation of ErSi<sub>1.7</sub> and PtSi phase are confirmed by x-ray diffraction (XRD) and Auger electron spectroscopy (AES) analysis. The sheet resistance are less than 30  $\Omega/\Box$  and 10  $\Omega/\Box$  for erbiumsilicide and platinum-silicide, respectively, even if the line width is less than 100 nm. Thus, erbium and platinum are applicable in sub-100 nm regime SB-MOSFETs manufacturing.

Table 1. Fabrication procedure of SB-MOSFETs

| Fabrication procedure |                                                                                                     |

|-----------------------|-----------------------------------------------------------------------------------------------------|

| 1                     | Cleaning of (100) SOI wafer ( $N_{SUB} = 10^{15} \text{ cm}^{-3} \text{ for } n/p$ -type substrate) |

| 2                     | Active lithography (e-beam) and dry etching                                                         |

| 3                     | PR strip, gate oxidation ( $T_{OX}$ = 5 nm) and $n^+$ polysilicon deposition.                       |

| 4                     | Gate lithography (e-beam), dry etching and PR strip                                                 |

| 5                     | Sidewall spacer oxidation ( $T_{SP}$ = 15 nm) and blanket etching                                   |

| 6                     | Erbium/Platinum deposition                                                                          |

| 7                     | Annealing (500℃, 10 min) and removal of erbium/platinum                                             |

# III. RESULTS AND DISCUSSIONS

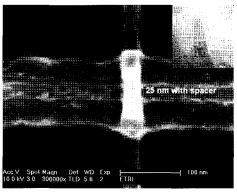

Erbium and platinum are chosen as source/drain metal of n/p-type SB-MOSFETs, because of its low Schottky barrier height for electrons and holes, respectively. Figure 1 shows the scanning electron microscopy (SEM) and transmission electron microscopy (TEM) of finally manufactured 10 nm-gate-length n-type SB-MOSFET. The uniform growth of ErSi<sub>1.7</sub> on the 20 nm width active

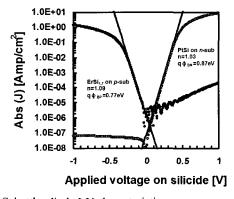

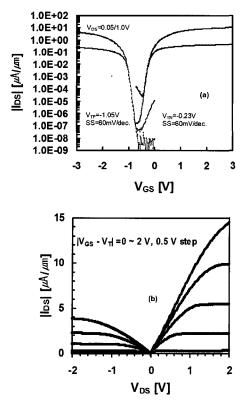

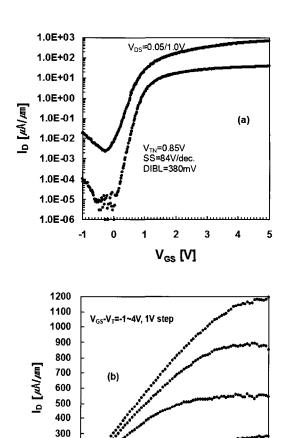

region is shown in the SEM image. Also, from the TEM image, the gate length is 10 nm with the 15nm thick SiO<sub>2</sub> sidewall spacer. Figure 2 shows the diode characteristics of ErSi<sub>1.7</sub> on p-substrate and PtSi on n-substrate, respectively. N<sub>2</sub> annealing was a very efficient method to remove the interface trap existing between silicide and silicon, thus improving diode I-V characteristics [4]. After N<sub>2</sub> annealing, Schottky barrier height of ErSi<sub>1.7</sub> for hole is 0.77eV and PtSi for electron is 0.87eV which corresponds to 0.36eV for electron and 0.25eV for hole, respectively. Figure 3 shows I<sub>DS</sub>-V<sub>GS</sub> and I<sub>DS</sub>-V<sub>DS</sub> characteristics of the 20 µm long channel n/p-type SB-MOSFETs. The gate oxide and spacer thickness is 5 nm and 15 nm, respectively. Both the n/p-type SB-MOSFETs show high on/off current ratio, larger than I<sub>on</sub>/I<sub>off</sub>>10<sup>5</sup> with low leakage current ( $I_{LKG}$ <100 pA/ $\mu$ m). The on/off ratio and the leakage current level is the highest and lowest values compared with previously published data in SB-MOSFETs [2]. Also, DIBL is almost suppressed in both n/p-type SB-MOSFETs and the SS value is 60 mV/decade both in n-type & p-type SB-MOSFETs, reaching the theoretical limit vsalue in MOSFETs.

**Fig. 1.** SEM and TEM (inset) image of the 10 nm erbium-silicided *n*-type SB-MOSFET

Fig. 2. Schottky diode I-V characteristics.

Fig. 3.  $I_{DS}$ - $V_{GS}$  (a) and  $I_{DS}$ - $V_{DS}$  (b) characteristics of  $20\mu m$  long channel n/p-type SB-MOSFET.

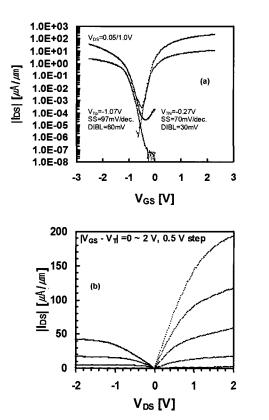

Fig. 4.  $I_{DS}$ - $V_{GS}$  (a) and  $I_{DS}$ - $V_{DS}$  (b) characteristics of 100 nm gate length n/p-type SB-MOSFET.

Figure 4 shows the  $I_{DS}$ - $V_{GS}$  and  $I_{DS}$ - $V_{DS}$  characteristics of 100 nm gate length n/p-type SB-MOSFETs. Also, this 100nm gate length n-type SB-MOSFET shows excellent short channel characteristics. The measured SS and DIBL values are 70 mV/decade and 30 mV, respectively.

Fig. 5.  $I_{DS}$ - $V_{GS}$  (a) and  $I_{DS}$ - $V_{DS}$  (b) characteristics of 10 nm n-type SB-MOSFET.

V<sub>DS</sub> [V]

1.5

0.5

200

100

0

Figure 5 shows the  $I_{DS}$ - $V_{GS}$  characteristics of 10 nm gate length n-type SB-MOSFETs manufactured on n-type substrate. Although the substrate doping concentration is  $10^{15} \rm cm^{-3}$ , short channel effect is sufficiently suppressed due to the existence of Schottky barrier between source and channel. The saturation current measured at  $V_{GS}$ - $V_T$ = $V_{DS}$ =2V is  $550 \, \mu A/\mu m$  ( $T_{ox}$ = $5 \, nm$ ). This is the highest saturation current value compared with the reported data. The major reason for the increase of saturation current is due to the reduction of underlap resistance by changing substrate type from p to n-type.

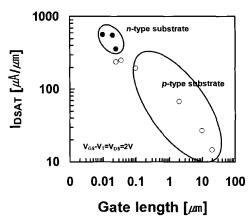

Fig. 6. Variation of saturation current with gate length.

Figure 6 shows the variation of saturation current with the gate length in n-type SB-MOSFETs. As the gate length decreases, saturation current increases. But the saturation current is clamped around 250  $\mu$ A/ $\mu$ m if the used substrate is p-type (open circle). By changing the substrate type from p to n, the saturation current gradually increases up to  $550\mu$ A/ $\mu$ m (closed circle). The major reason for the increase of saturation current is the reduction of parasitic underlap resistance.

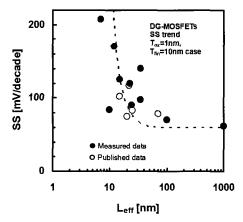

**Fig. 7.** Subthreshold swing (SS) characteristics. Scaling theory is applied for the evaluation of SS.

Figure 7 shows the SS characteristics of SB-MOSFETs with the variation of gate length. In Figure 7, dotted line represents theoretical DIBL characteristics of DG-MOSFETs. The scaling theory of DG-MOSFETs can be found in [5]. In the calculations of SS in DG-MOSFETs, gate oxide and fin thickness are assumed as 1 nm and 10 nm, respectively. Note that these assumed values correspond to the ultimate minimum values in device technology. The SS characteristics of SB-MOSFETs are

better than the ultimate limit characteristics of DG-MOSFETs. The reason for this is due to the existence of the Schottky barrier between source and channel. In MOSFETs and DG-MOSFETs, the subthreshold characteristics, including DIBL and SS, are mainly determined by the built-in potential. In short channel device, as the drain voltage increases, built-in potential between source and channel decreases, giving DIBL effect. But in SB-MOSFETs, the subthreshold characteristics are mainly determined by the Schottky barrier.

#### IV. CONCLUSIONS

In conclusion, various sizes of erbium/platinum silicided n/p-type SB-MOSFETs are manufactured from 20  $\mu$ m to 10 nm. The manufactured SB-MOSFETs show excellent DIBL and subthreshold swing characteristics due to the existence of Schottky barrier between source and channel. It is found that the minimization of trap density between silicide and silicon interface and the reduction of the underlap resistance are the key factors for the improvement of short channel characteristics. The manufactured 10 nm n-type SB-MOSFET showed 550  $\mu$ A/ $\mu$ m saturation current at  $V_{GS}$ - $V_T$  =  $V_{DS}$  = 2V condition ( $T_{ox}$  = 5nm) with excellent short channel characteristics, which is the highest current level compared with reported data.

In SB-MOSFETs, SS characteristics of SB-MOSFETs are better than the ultimately scaled DG-MOSFETs, which show the possible application of SB-MOSFETs in nanoscale regime as an alternative to the MOSFETs.

#### REFERENCES

- [1] S. Zhu, J. Chen, M.-F. Li, S. J. Lee, J. Singh, C. X. Zhu, A. Du, C. H. Tung, A. Chin and D. L. Kwong, "N-type Schottky barrier source/drain MOSFET using ytterbium silicide", *IEEE Electron Device Lett.*, vol. 25, pp. 565-567, August. 2004.

- [2] J. Kedzierski, P. Xuan, E. K. Erik, H. Anderson, J. Bokor, T.-J. King, and C. Hu, "Complementary silicide source/drain thin-body MOSFETs for the 20 nm gate length regime", in *IEDM Tech. Dig.*, 2000.

- pp. 57-60, 2000.

- [3] M. Jang, Y. Kim, J. Shin and S. Lee, "A 50-nm-gate-length erbium-silicided n-type Schottky barrier metal-oxide-semiconductor field-effect transistor", Applied Phys. Lett., vol. 84, pp. 741-743, Feb. 2004.

- [4] M. Jang, Y. Kim, J. Shin, M. Jun, and S. Lee, "Scalability of Schottky barrier MOSFETs for nanoregime applications", Silicon Nanoelectronics Workshop, pp. 90-91, 2005.

- [5] K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie and Y. Arimoto, "Scaling theory for double-gate SOI MOSFET's", *IEEE Trans. Elect. Dev.*, Vol. 40, pp. 2326, 1993.

Moongyu Jang was born in Korea on October 18, 1968. He received the B.S. degree in Physics at Kyungpook National University, Daegu, Korea, in 1991 and the MS and Ph.D degrees in Physics at Korea Advanced Institute of Science and Technology (KAIST),

Daejon, Korea, in 1993 and 1997. In 1997, he joined HYUNDAI Electronics, Inc., Ichon-Si, Korea (now HYNIX Semiconductor, Inc.), where he was involved in the process integration of MDL (Merged DRAM and Logic) devices. From 1997 to 1998, he was involved in the development of 0.35 micron MDL technology. From 1999 to 2001, he was involved in the development of 0.18 micron MDL technology. Now he has moved to Electronics and Telecommunications Research Institute (ETRI), Daejon, Korea, where he is involved in the basic research on nanoscale MOSFET devices. His research interests include processing and analysis of nanoscale MOSFETs, Schottky barrier MOSFETs (SB-MOSFETs) and mesoscopic quantum transport phenomena. Dr. Jang is the member of IEEE and Korean Physical Society.

Yarkyeon Kim received the B.S. degree in physics from Korea University in 1984, the M.S. degree in physics from Korea University in 1986, and the Ph.D in physics from Korea University in 1995. He has worked in ETRI ever since 2001 and

is presently involved in the basic research on nanoscale MOSFET devices. His research interests include the Schottky barrier MOSFETs (SB-MOSFETs) and novel electronic devices, such as spin-FETs.

Myungsim Jun was born in Korea on November 13, 1971. She graduated from Konkuk University, Seoul, Korea, with a B.S. degree in Physics in 1994. And she received the MS and Ph.D degrees in Physics and Enginnering at Korea University,

Seoul, Korea, in 1998 and 2004, respectively. During Ph.D course, she studied magnetotransport spectroscopy of coupled quantum dots and the frequency response of electron tunneling thru InAs self-assembled quantum dots by microwave pulse. She worked as a researcher at IQUIPS (Institute of Quantum Information Processing & Systems) at Univ. of Seoul in Korea. Now she is involved in the basic research on nanoscale MOSFET devices at Electronics and Telecommunications Research Institute (ETRI), Daejon, Korea. Her research interests are Schottky contact, Schottky barrier diode, Schottky barrier MOSFETs (SB-MOSFETs) and quantum transport phenomena.

Cheljong Choi was born in Korea on June 16, 1974. He received the B.S. degree in Ceramic Engineering at Hayang University, Seoul, Korea, in 1997 and the MS and Ph.D degrees in Materials Science Engineering at Gwangju Institute of

Science and Technology (GIST), Gwangju, Korea, in 1999 and 2003, respectively. From 2003 to 2005, he worked at Samsung Advanced Institute of Technology (SAIT), Suwon, Korea, in the areas of semiconductor device characterization. He joined Electronics and Telecommunications Research Institute (ETRI), Daejon, Korea, in 2005 and is now engaged in the research of nano-fabrication technology for Schottky Barrier MOSFETs devices.

**Taeyoub Kim** received the MS degree in physics from Yonsei University of Seoul, Korea, in 2000. He has been a Research Member in ETRI (Electronics and Telecommunications Research Institute) since 2000. His research intereste include

processing and analysis of nanoscale electronic devices and an investigation of quantum phenomena for silicon nano-crystals.

**Byoungchul Park** was born in Korea on January 10, 1975. He received the B.S. degree in Chemistry at Korea University, Chungnam, Korea, in 2002 and He is going to receive the M.S. degrees in Department of Nano-science and

Technology at Chungnam National University, Daejon, Korea, in 2007 Now he has worked to Electronics and Telecommunications Research Institute (ETRI), Daejon, Korea, where he is involved in the basic research on nanoscale MOSFET devices. His research interests include processing and analysis of nanoscale MOSFETs, Schottky barrier MOSFETs (SB-MOSFETs).

Seongjae Lee received the B.S. degree in physics from Seoul National University in 1980, the M.S. degree in physics from Korea Advanced Institute of Science and Technology (KAIST) in 1982, and the Ph.D in physics from Northwestern University in 1991. He

has worked in ETRI ever since 1991 and is presently a Team Manager in the basic research laboratory of ETRI. His research interests include novel nanoscale electronic Si-devices for ultimate-CMOS and post-CMOS technologies.