# 반도체산업의 기술 및 표준화 동향([)

디지털표준과 공업연구관 이상근 02)509-7266~70 sglee@ats.go.kr

### 1. 반도체산업 동향

2004년 반도체 세계시장은 전년대비 23 % 성장한 2,198억불을 기독했다. 전체IT시장에서 반도체가차지하는 비율은 2002년 1,558억불로 7.1 %를 차지했으나 2003년엔 1,774억불의 매출을 달성하며 7.5 %로 소폭 증가하였다. 주요성장 동인으로는 공급측면의 설비가동률의 개선과 적정재고수준 유지를통한 평균판매가격 인하가 많은 영향을 미쳤으며. 점차 기업들의 IT지출 증가에 따라 수요확대가 본격화

되고 있다. 세계시장은 2005년 2,275억불로 3.5 % 증가하고 2008년 2,951억불 규모로 년평균 7.8 % 성장이 예상된다(표 1). 한국은 2004년 265억불 수출에서 2006년 320억불에 이르는 수출확대가 전망된다. 메모리와 비메모리 시장은 약 1 대 4의 점유분포를 가지며, 2004년 반도체시장 2.198억불중에서메모리가 480억불로 22 %, 비메모리는 1,718억불로 78 %를 점유하는 비메모리가 주류를 이루고 있다.

<표 1. 반도체의 세계시장 추이>

(단위 : 억불)

| 년도<br>구분    | 2004  | 2005  | 2006  | 2007  | 2008  | CAGR<br>'04-' 08 |

|-------------|-------|-------|-------|-------|-------|------------------|

| 총 반도체       | 2,198 | 2,275 | 2,324 | 2,561 | 2,951 | 7.8%             |

| 총 메모리       | 480   | 496   | 428   | 505   | 640   | 8.5%             |

| D램          | 263   | 270   | 185   | 234   | 324   | 9.1%             |

| 플래시메모리 NAND | 68    | 80    | 90    | 103   | 129   | 17.4%            |

| 반도체 성장율(%)  | 23    | 3.5   | 2.1   | 10.2  | 15.2  | 7.8%             |

(출처: Gartner Dataquest, 2005. 2)

### 1) 머모리반도체 세계시장

품목별 메모리반도체의 세계시장은 2006년 메모리반도체 시장은 큰 폭으로 축소되고, 메모리반도체 중에서 큰 비중을 차지하는 D램의 시장위축주기로 인하여 2006년의 메모리반도체시장이 크게 위축된 -31 %의 성장을 이룬다(표 1). 그 이유는 D램업체들의 300mm라인 본격 가동과 미세희로 적용 등에 따른 공급과잉 등으로 성장의 정체가 예상된다

2004년에 메모리시장의 급성장(38.7 %)은 견조한 PC 및 휴대용 정보기기 출하 증가로 수급이 균형을 이루고 있다. 2004년부터 2008년까지 D램은 9%의 지속적인 증가와 NAND형 Flash메모리는 17%의 급성장으로 메모리반도체를 주도할 전망이다. 또한 D랟의 60% 규모에 그치고 있는 Flash메모리시장이 휴대형 기기의 급성장으로 2006년이후 D랟을 능가하는 시장을 이루며 메모리반도체의 시장 주도권을 놓고 치열한 경합을 벌릴 것으로 예상된다.

'04년 메모리 세계시장에서 한국은 미국, 일본과 각축하며 1위를 차지하였다(표 2).' 97년이후 D랟 시장에서 한국이 7년 연속 1위로 세계시장을 주도하 고 있으며, S램 및 Flash메모리 시장에서 한국은 미국에 이어 2위 시장점유로 일본과 함께 3강구도를 이루고 있으나 금년에 한국의 신제품 및 시장 확대가 기대된다. 또한 최근에 대만의 전폭적인 정부지원을 얻어 약진을 시작되었다.

#### 2) 한국의 반도체 산업

반도체 산업은 한국의 전략수출산업이며 단일품목으로 1992년 이래 12년 연속 수출1위 품목으로 2003년 195억불의 수출로 전체 수출의 10.1 %와 2004년 265억불의 수출로 10.4 %를 차지하고 있다(표 3). 메모리와 비메모리의 생산비율은 83:17로메모리가 주를 이루고 있어 세계 반도체업계의 평균(22:78)과 비교시 한국의 반도체 생산구조는 매우불안정한 상태이다. 향후 한국은 세계시장을 선도하는 메모리반도체분야를 더욱 강화하며, 또한 소량다품종의 고부가가치인 비메모리 제품을 사업의 다각화함으로 세계일류상품의 확대가 필수적으로 요구되고 있다.

·04년 반도체 수출은 265억불로 전년대비 35.8

<표 2 2004년 메모리 세계시장 및 국가별 시장점유율>

|       | 2004년        | 한국<br>매출액<br>(억불) |      | 비고   |      |      |       |

|-------|--------------|-------------------|------|------|------|------|-------|

| 구분    | 세계시장<br>(억불) |                   | 한국   | 미국   | 일 본  | 대 만  | 3 2 2 |

| 메모리전체 | 480          | 181               | 38.0 | 29.0 | 15.2 | 10.2 | 1 위   |

| D램    | 263          | 124               | 47.1 | 17.3 | 6.9  | 15.3 | 1 위   |

| S램    | 41           | 13                | 31.1 | 35.5 | 28.9 | 4.2  | 2 위   |

| Flash | 154          | 44                | 28.5 | 28,5 | 24.7 | 2.7  | 2위    |

(출처: Gartner Dataquest, 2005, 3)

% 증가하였으며, Flash메모리(93%) 및 DRAM(53 불로 세계 각 지역으로 5%)의 급성장하였다. 주요 수출국가는 미국 46억불, 역의 경제성장에 따라 등 대만 41억불, 일본 35억불, 중국 32억불, 독일 21억 크게 증가였다(표 4-5)

불로 세계 각 지역으로 수출을 하였고. 최근 아·태 지역의 경제성장에 따라 중국 등 아시아 지역의 수출이 크게 증가였다(표 4-5)

#### <표 3. 한국의 반도체 수출 추이>

(단위 : 억불)

| 년도    | ' 98년 | '99년  | '00년  | '해년   | '02년  | '03년  | '04년  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 총수출   | 1,323 | 1,437 | 1,724 | 1.506 | 1,624 | 1.938 | 2,538 |

| 반도체수출 | 170   | 203   | 260   | 143   | 166   | 195   | 265   |

| 비중(%) | 12.8  | 14.1  | 15.1  | 9.0   | 10.3  | 10.1  | 10.4  |

(출처: 산자부통계, 2005. 3)

#### <표 4. 2004년 한국의 국가별 반도체 수출 현황>

(단위:백만불)

| 총수출    | 미국    | 대만    | 일본    | 중국    | 싱가폴   | 독일    | 구<br>경 |

|--------|-------|-------|-------|-------|-------|-------|--------|

| 26,516 | 4,622 | 4.115 | 3.544 | 3,728 | 2,625 | 2,126 | 276    |

(출처: 산자부통계, 2005. 3)

#### <표 5. 한국의 품목별 반도체 수출 현황>

/rtol·HURL⊟\

|  | 품목 구분       | 2004년 수출 | 전년대비 성장옯(%) |

|--|-------------|----------|-------------|

|  | 메모리         | 15,956   | 47.6        |

|  | DRAM        | 9.620    | 53.3        |

|  | Flash       | 3,350    | 93.2        |

|  | 기타(SRAM 포함) | 2,896    | 3.4         |

|  | 비메모리(조립포함)  | 10.560   | 21.0        |

|  | 합계          | 26,516   | 35.8        |

(출처: 산자부통계, 2005. 3)

# 2. 반도체 기술동향

# 1) 반도체 제조공정

반도체 제조공정은 Si 웨이퍼를 가공하는 전공정 (FAB)과 조립하는 후공정(Packaging)으로 분류되며, 전공정의 핵심은 초미세화 공정기술을 다음 두 기술로 크게 대별하는데 첫째가 리소그라피 공정기술이고. 둘째가 박닥증착. 식각, 세정 등의 리소그라피 이외의 기타 공정 기술이다.

### 2) 반도체 기술발전

표6에서와 같이 메모리반도체는 PC의 메인 메모리에 주로 사용되며, 고집적화, 고속화, 저전력화, 생산단가 절감 등의 특징을 가지고 있다. 90년대 후반

부터 펜티엄급 PC출시로 이전에 비하여 D램의 속도 도 중요성을 가지기 시작하였으며 D램은 고속화를 위해 S(싱크로너스)D램. SD램의 2배의 전송속도를 가지는 DDR SD랟, SD랟의 4배의 전송속도를 가지는 램버스 D램, 랟버스 D램의 4배의 전송속도를 가지는 XDR D램 등으로 발전하고 있다

현재 SD램(25 %)과 DDR SD램(70 %)이 대부분의 D램시장을 차지하고 있으나 D램의 고집적도 향상에 의한 가격경쟁력 향상이 최우선시 되며, SD램, DDR, 램버스, XDR 등의 고속화 D램 생산업체는 제품의 개발에 앞서 우선적으로 표준화를 추진하고 있다. 삼성전자, 하이닉스 등 국내업체는 반도체분야 국제표준을 주도하고 있는 JEDEC에 적극적인 참여를통하여 차세대 D램분야 국제표준 작업에 선도적으로 활동을 하고 있다.

# <표 6. 메모리 반도체의 종류 및 전망>

| 메모리 반도체 (휘발성 & 비휘발성 메모리) |           |                                               |             |             |      |            |  |  |  |

|--------------------------|-----------|-----------------------------------------------|-------------|-------------|------|------------|--|--|--|

| 중 류                      | L         |                                               | 용도          | 기 능         | 추 세  |            |  |  |  |

| • 휘발성<br>메모리             | • Dan     | S램  DDR SD랜 DDDR2 SD랜 DDDR3 SD랜 H버스 D래 XDR D램 | 메인<br>메모리   | 고집적<br>대용량  | 고속화  | 저전력<br>저가격 |  |  |  |

|                          | •S램       | ·DDR SS <sup>2#</sup>                         | 동영상         | 고속도         |      |            |  |  |  |

| • 비휘발성<br>메모리            | • Flash에! | 로리                                            | 디지털<br>정보기기 | 비휘발성<br>저전력 | 비휘발성 |            |  |  |  |

최근에 모바일 기기 및 디지텉가전의 디지털화 확 산으로 Flash 메모리가 부상하고 있으며 Flash 메모 리의 큰 소비전력, 느린 쓰기 속도 등에 대한 한계로 집적화, 고속화, 저전력화, 생산단가 절감 등과 관련 F랟과 같은 새로운 비휘발성데모리의 개발이 요구되 하여 보고자한다.

고 있다.

표 7에서와 같이 D램 메모리반도체의 로드맵을 고

#### <표 7. D램 메모리반도체의 Road Map>

| 개발<br>년도   | 양산<br>년도 | 용량<br>DRAM | 선폭<br>(ᡣᡣ) | 리소<br>그라피<br>광원       | 웨이퍼<br>사이즈<br>(㎜) | 동작전압<br>( <sup>(</sup> ) | 커패시터<br>유전체                                                                              | 전국<br>재료  | 용량<br>(신문지)   |

|------------|----------|------------|------------|-----------------------|-------------------|--------------------------|------------------------------------------------------------------------------------------|-----------|---------------|

| ,85        | '95      | 64M        | 0.35       | I/KrF                 | 200               | 3.3                      | \$iOz/\$i:Nz<br>(ON)                                                                     | poly-Si   | 520매<br>(15일) |

| <b>'94</b> | '98      | 256M       | 0.25       | I/KrF                 | "                 | 2.5                      | ON                                                                                       | paly-Si   |               |

| '96        | 10'      | 1G         | 0.18       | KrF                   | 300               | 1.8                      | ON/<br>Ta₂O₅                                                                             | \$i/TiN   | 백과<br>사전      |

| ,00        | 04       | 4G         | 0.13       | KrF<br>ArF            | "                 | 1,5                      | Ta <sub>2</sub> O <sub>5</sub> /<br>Al <sub>2</sub> O <sub>3</sub> /<br>HfO <sub>2</sub> | Si/TiN/Ru |               |

| ,03        | 70       | 16G        | 0.10       | ArF<br>F <sub>2</sub> | "                 | 1.2                      | SrTiO₁                                                                                   | Ru        |               |

| ,06        | ,10      | 64G        | 0.07       | ArF<br>F <sub>2</sub> | 400               | 0,9                      | (Ba.Şr)TiO;                                                                              | Ru        | 인간<br>메모리     |

| ,09        | 13       | 256G       | 0.05       | EB. EUV               | "                 |                          | (Ba.Sr)TiO;                                                                              | Ru/Pt     |               |

- \* JEDEC: 합통전자소자협의회(Joint Electron Device Engineering Council)

- 미국 전자공업협회(EIA)의 하부조직으로, 제조업체와 사용자 단체가 합동으로 집적회로(IC) 등 전자장치의 통일규격을 심의, 제정

- 1960년에 설립돼 현재 300여개 회원사와 1천800명의 멤버가 활동하고 있으며 각 분야의 전문 가로 구성된 48개의 위원회를 두고있는 반도체 규격 표준화 분야에서 가장 영향력 있는 단체

# 3) 고집적화

D램의 고집적화에 따라 선폭이 축소되면서 양산성 확보의 어려움. 공정 복잡도의 증가에 따르는 생산성 저하 등의 제반 문제점을 동반하고 있다. 또한 차세대 D램의 주요 기술개발은 나노 리소그라피기술, 고정전용량 커패시터와 고유전 트랜지스터 등에 집중되고 있다.

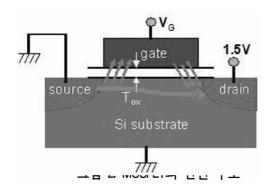

메모리 반도체의 경우 그림1에서와 같이 선폭은 한 셀의 짧은 변의 반으로 정의하며, 비메모리 토직 소자의 경우는 트랜지스터의 게이트 선폭 즉 게이트 길이로 정의한다.

리소그라피(Lithography, 노광)는 노광원을 사용하여 설계된 대로 웨이퍼 위에 미세회로 패턴을 형성하는 기술로서 0.1 ㎞이하의 선폭 축소에 따라 단파장의 광원을 채택한 나노 리소그라피기술을 개발중이며, 짧은 파장의 노광원이 높은 해상력을 가지며 더디세한 회로선폭을 형성시킨다. 0.1㎞이하의 선폭 적용을 위해 광학 리소그라피기술에서 비광학 리소그라피기술는 엑사이머 레이저(KrF. ArF . 193 ㎜ ~248 ㎜)를 사용하고 있고, 엑사이머 레이저(KrF. ArF) 리소그라피 공정의 문제점은 초점의 작은깊이, 라인모서리의라운딩, 후 노출 지연. 건식에칭의 낮은 저항. 비싼 가격 등이 있다.

이러한 문제점을 개선하기 위하여 비광학 리소그라 피기술은 전자범과 극초자외선을 사용하고 있으며, 전자범(EB, Electron Beam)는 100 kV의 전자범을 이용하며 초점의 큰 깊이와 싼가격의 마스크 등의 이점을 가지는 나노 리소그라피기술로서 극초자외선(EUV, Extreme Ultra Violet)는 현재 가장 짧은 파장(13 mm ~11 mm)을 가지며, 70 mm ~35 mm의 선폭을 형성시키는 최상의 차세대 나노 리소그라피기술로 알려져 있다

#### Half Pitch (=Pitch/2) Definition

그림1. DRAM과 CPU의 선폭

커패시터의 용량증대를 위하여 전극 표면적의 증가. 고유전율 재료의 채택에 대한 연구가 활발히 진행되고 있으며 현재의 저유전율의 유전체는 SiO<sub>2</sub>(k~3.9)와 S<sub>1</sub>,N, (8)로서, 향후 차세대 고유전율의 유전체는 Ta<sub>2</sub>O<sub>3</sub>(25). HfO<sub>2</sub> (25). STO(200), BST (>300)등이 있다.

또한 열 안전성이 높은 전극재료를 개발하기 위하여 현재의 poly-Si (Si)을 대체할 금속(Ru. Ru/Pt) 전극재료를 주목하고 있으며, 이러한 고유전체와 금속전극을 이용한 고정전용량 커패시터에 대한 연구가활발히 진행되고 있다

소자 및 트랜지스터 내에서 전자의 전달속도를 높이기 위해(게이트)선폭을 줄이는 추세이나 0.13㎞이하의 선폭에서는 short channel효과가 발생한다 그림2에서와 같이 short channel효과란 source-drain(channel)의 짧은 거리로 인하여 게이트 on/off가 조절되지 않아서 누설전류가 흐르는 현상을 말하며, short channel효과를 방지하기 위하여 기존의 SiQ, 저유전체에서 HfQ, 등의 고유전 박막절연체로 대체됨으로 고유전 트랜지스터가 개발되고 있다

### 4) 고속화

배선기술은 IC에서 트랜지스터의 상호 연결회로를 구성하며, 전원공급 및 신호전달의 통로를 실리콘 위 에 구현하는 기술을 달한다. 현재는 주로 알루미늄 배 선을 사용하고 있으나 고집적화/고속화 추세에 따라 제반 문제점이 유발된다. 선폭감소로 인하여 배선 및 콘택트 저항치가 증대되고 저항열과 일렉트로마이그 레이션(Electromigration) 등의 문제점이 발생된다 일렉트로마이그레이션은 전류밀도가 높을 경우 전자 이동의 반대방향으로 원자가 움직여 심할 경우 배선 이 끊어지기도 하는 현상이다.

고속화를 위한 차세대 배선재료로써 구리/저유전 절연재료에 대해 많은 연구가 진행중에 있다 구리는 알루미늄에 비해 낮은 저항(62 %)을 가지며, 현재의 고유전율(3 9)을 가지는 SiO,에서 저유전율(2 5)을 가지는 SiOC 절연재료가 대체되며 부각되고 있다.

# 5) 저전력화

Non-PC의 반도체 수요급증에 따라, 동작속도의 증가와 발열량의 감소를 위하여 저전압. 저소비전력의 기술을 개발하고 있다. 주요 Non-PC는 휴대전화, DVD, MPEG, GPS, 게임기, HDTV 등의 정보기기이다. 표 8에서와 같이 메모리반도체의 선폭 감소에따라 D램은 3 3 V에서 2 5 V 및 1 8 V로, S램은 1.8 V에서 1.2 V~1.5 V 및 1.0 V이하의 저전압에서 동작하는 추세를 보이고 있다. 70 mm의 선폭에서 최대소비전력은 1.0 W이하로 될 것이다.

소자와 소자, 소자내 트랜지스터 사이를 완전 절연

| DĄ    | <u> </u>      | S램      |           |  |  |

|-------|---------------|---------|-----------|--|--|

| 전압(V) | 선폭(ɹm)        | 전압(V)   | 선폭(㎞)     |  |  |

| 3.3   | 0.35~0.14     | 1.8     | 0.17~0.07 |  |  |

| 2.5   | 0,26~0,11     | 1,2~1.5 | 0.11~0.05 |  |  |

| 1.8   | 1.8 0.17~0.07 |         | ( 0.07    |  |  |

<표 8. 메모리반도체의 선폭 감소와 저전압 동작>

시키므로 누설전류를 감소하게 한다. 현재 주로 사용되는 실리콘 대신에 실리콘이중막 웨이퍼(SOI) 및에피 웨이퍼를 개발 중이며. SOI(Silicon On Insulator, SiO<sub>2</sub>)는 실리콘 웨이퍼에 산소이온을 주

입해 실리콘 표면 아래에 실리콘산화막(SiQ)을 형성 시키게 된다 SOI를 적용할 경우 전력소모량은 30 %이상 감소하고 속도는 30 %이상 향상하게 된다.

rechnolog Technolog

### B) 생산단가의 절감

300 페웨이퍼를 채택할 경우 기존의 200 페웨이 퍼보다 면직이 2.25배 늘어나 장당 칩생산량의 중대 로 인하여 생산단가가 크게 감소된다. 웨이퍼의 크기 가 커지면 단위공정당 가격은 높아지지만, 웨이퍼당 칩수가 증가하여 결과적으로 생산단가가 절감된다.

젤 크기는 참 사이즈와 젤 효율을 높이기 위하여 젤 무조를 8F\* 구조에서 6F\* 또는 4F\* 구조로 변경하여 절반의 젤 크기를 가지는 새로운 젤을 개발하고 있다. F를 minimum feature size, 즉 선폭과 대략 같다. 그러나 8F\* 이외의 cell architecture는 아직 한번도 대량 생산되어 그 성능이 검증된 바 없기 때문에 이와 같은 achitecture의 변경은 모든 회사에서 가장 끼려 하는 부분이다.

# 7) 차세대 반도체 공정과 나노기술의 적용

반도체 공정에서 나노기술은" 선목이 150 nm이므로 nano-tech이 아니고 100 nm이므로 nano-tech이 임"과 같이 구별하지 않으며, 신공정의 채택여부와 나노크기 생성돌의 새로운 특성을 나타내는가의 이부에 따라 나노기술로 정의한다.

기존 기술(마이크로기술)과 나노기술의 작용 사례를 살펴보면, CMOS (상보성급속산화물반도체) 트랜지스터의 게이트 산화박막의 정우에 대하여 150 nm 선폭의 IC에서 산화박막의 두께는 2 nm ~3 nm 수준이지만 기준의 SiO<sub>2</sub> 열산화막 공정으로 제조하고 있다. 100 nm 이하에서는 short channel 효과의 발생으로 기존 산화박막의 적용이 불가능하여 새로운 고유전율 산화박막이 요구되고 있다. ALD법(원자층 중작법)을 이용하여 절연박막을 형성하며, 새로운 산화박막의 5nm두께는 short channel 효과를 지지하여 누실전류를 억제한다. 이로 인하여 기존의 산화박막보다 새로운 박막의 두께가 두껍지만, 그 박막의 특성이 개선되었기 때문에 이는 나노기술을 작용했다고 볼 수 있다.

이미 적용증인 나노기술을 살펴보면, 기패시터 제조공정에서 LISG (hemi spherical grain)를 이용하여 거패시터 표면적을 늘리는 공장은 이미 64 M 때부터 적용하고 있다. HISG는 구불구불한 표면을 항성하여 커패시터 표면적을 최대화한다. 반도체공정에서의 나노기술은 양산성을 구비한 리소그라피기술과 결합하여 새로운 특성을 보이는 나노 생성물을 항성한다. 🔝