# **Optimization of Low Power CMOS Baseband Analog Filter-Amplifier Chain for Direct Conversion Receiver**

Minkyung Lee\*, Ickjin Kwon\*\*, and Kwyro Lee\*\*

Abstract—A low power CMOS receiver baseband analog circuit based on alternating filter and gain stage is reported. For the given specifications of the baseband analog block, optimum allocation of the gain, IIP3 and NF of the each block was performed to minimize current consumption. The fully integrated receiver BBA chain is fabricated in 0.18 µm CMOS technology and IIP3 of 30 dBm with a gain of 55 dB and noise figure of 31 dB are obtained at 4.86 mW power consumption.

#### I. Introduction

Due to the demand of longer battery life and lower cost solutions for wireless personal area network (WPAN) such as IEEE802.15.4, low power single chip CMOS receivers draw great attention [1]. Among the various receiver architectures, the direct conversion receiver (DCR) is a viable candidate solution for low cost and low power.

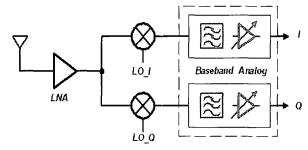

In a direct conversion receiver as shown in Fig. 1, all in band blockers reach baseband stage without filtering. Thus high linearity performance of baseband analog circuit is required to cope with interferers. Also, those in band interferer limits the allowed gain of the RF front-end and thus the noise performance becomes critical. Since input-referred third-order intercept point (IIP3) and noise figure is approximately proportional to the DC power consumption, it is a great challenge to achieve a compromise of high linearity and low noise performance at low power

consumption.

Fig. 1. Baseband analog circuit for direct conversion receiver.

In this paper, optimum allocation of gain, IIP3 and NF of filter stage and gain stage in baseband chain is proposed to minimize current consumption of the overall baseband analog (BBA) chain for a required specification. A receiver BBA circuit is designed and fabricated in 0.18 µm CMOS process. The low power receiver BBA design method is explained in detail and the fabrication results are reported.

# II. OPTIMUM DESIGN METHOD FOR LOW POWER BASEBAND CHAIN

The noise figure and IIP3 performance of the receiver depends on the noise and linearity of blocks as well as their gain. Filtering followed by gain stage suppress out-of channel interferers, relaxes linearity requirement of the gain stage. But the low noise channel selection filter is required. Gain stage followed by filtering stage relaxes LPF noise requirements while demanding a high linearity amplifier. At the same power consumption, the structure with the best noise performance leads to the worst linearity performance. Vice versa, a structure with high linearity leads to bad noise performance. To increase noise and linearity performance, more supply current

Manuscript received April 1, 2004; revised August 30, 2004.

<sup>\*</sup> Telecommunication Network, Samsung Electronics, Suwon, Korea.

<sup>\*\*</sup> Dept. of EECS, KAIST, Also with MICROS Research Center, Daejeon, Korea.

need to be used in the building block. This is not a good way because the current consumption should be minimized. The best way to design the optimum baseband chain is alternating filter and gain stages [2]. This allows better trade-offs between noise figure and linearity for each stage.

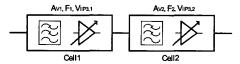

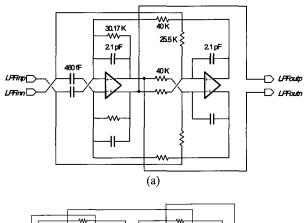

Fig. 2. Baseband analog chain which alternates filters and gain stages.

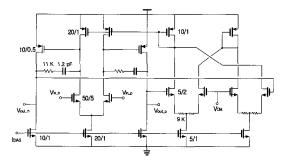

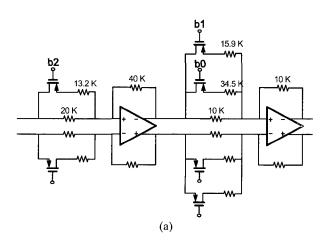

Fig. 3. Two-stage opamp.

To minimize the power consumption for the required specification, the relations between linearity, noise figure and current consumption need to be understood. In this paper, we consider the multi-stage baseband analog chain consists of unit cell with filter and gain function. Cascaded BBA chain model consists of two cells as shown in Fig. 2 can be extended to multi-stage BBA chain.

The theoretical I-V curve of a short channel MOSFET is given as following:

$$I_{d} = \frac{1}{2} \frac{W}{L} \mu_{eff} C_{ox} \frac{V_{GT}^{2}}{1 + \theta \cdot V_{GT}^{2}}$$

(1)

where  $\theta = 1/(E_{sat} \cdot L)$  and  $V_{GT} = V_{GS} \cdot V_t$ .

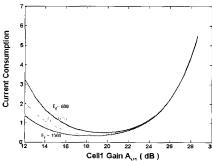

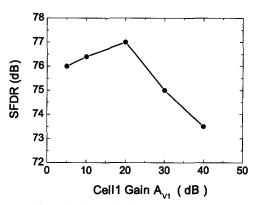

**Fig. 4.** Current consumption of overall BBA chain versus gain of cell1  $(A_{VI})$

**Fig. 5.** Transistor-level circuit simulation results of spurious free dynamic range (SFDR) versus gain of cell1 at fixed total current consumption.

$$V_{IIP3} \approx \frac{8}{3} \frac{V_{GT}}{\theta} = KV_{GT} \tag{2}$$

where  $K = 8/(3\theta)$ . Using the relation in [4], the IIP3 of Filter and PGA circuit with feedback is given by

$$V_{IIP3}^2 = KV_{GT} \left( 1 + \left| \frac{A_o}{A_v} \right| \right)^3 \tag{3}$$

where  $A_o$  is open-loop gain and  $A_V$  is closed loop gain of two-stage op-amp. We assume that feedback element is linear due to the use of linear passive element.

In an active-RC filter, both the op-amp and the resistors add noise. The input-referred noise of two-stage op-amp which used in this design as shown in Fig. 3 is determined by the active transistor and the active load of the first stage as following:

$$\frac{\overline{V_n^2}}{\Delta f} = \frac{8kT\gamma}{g_{mn}} \left( 1 + \frac{g_{mp}}{g_{mn}} \right) \tag{4}$$

where  $\gamma \ge 3/2$ . Then, noise figure of this circuit with respect to the source resistance  $R_S$  is

$$F = 1 + \frac{1}{g_{w}R_{c}} \left( \gamma + \frac{1}{A_{v}} \right) \tag{5}$$

The IIP3 and noise figure of each stage is related to the current consumption by spurious free dynamic range (SFDR) as following:

$$SFDR = \left(\frac{IIP3}{F \cdot kTB}\right)^{\frac{2}{3}} \approx \left(\frac{K \cdot I}{kTB(\gamma + 1/A_{\nu})}\right)^{\frac{2}{3}} \cdot \left(1 + \left|\frac{A_{o}}{A_{\nu}}\right|\right)^{2} \quad (6)$$

Then, current consumption of each stage is given by

$$I = \frac{1}{2R_s K} \left( \gamma + \frac{1}{A_\nu} \right) \left( \frac{V_{\mu p_3}^2}{F} \right) \left( 1 + \left| \frac{A_\nu}{A_\nu} \right| \right)^{-3} \tag{7}$$

The total current consumption of the baseband chain as shown in Fig. 2 is

$$I_{total} = \sum_{n=1}^{2} \frac{1}{2R_{s}K} \left( \gamma + \frac{1}{A_{\nu_{n}}} \right) \left( \frac{V_{IIP3,n}^{2}}{F_{n}} \right) \left( 1 + \left| \frac{A_{o}}{A_{\nu_{n}}} \right| \right)^{-3}$$

(8)

The dynamic range (DR) of a cascaded stage is determined by the noise figure, IIP3 and gain of each stage, as following:

$$\frac{1}{DR} = \frac{F}{V_{_{IIP3}}} = \left(F_{_{1}} + \frac{F_{_{2}} - 1}{A_{_{V_{1}}}^{2}}\right) \cdot \left(\frac{1}{V_{_{IIP3,1}}^{2}} + \frac{A_{_{V_{1}}}^{2}}{V_{_{IIP3,2}}^{2}}\right) \\

= \frac{F_{_{1}}}{V_{_{IIP3,1}}^{2}} + \frac{F_{_{2}} - 1}{V_{_{IIP3,2}}^{2}} + \left(\frac{F_{_{1}}}{V_{_{IIP3,2}}^{2}} A_{_{V_{1}}}^{2}\right) + \left(\frac{F_{_{2}} - 1}{V_{_{IIP3,1}}^{2}} \frac{1}{A_{_{V_{1}}}^{2}}\right)$$

(9)

Then, the dynamic range of overall cascaded stage is maximized at the following condition:

$$A_{V1}^2 = \sqrt{\frac{F_2 \cdot V_{IIP3,2}^2}{F_1 \cdot V_{IIP3,1}^2}} \tag{10}$$

The third-order intermodulation is unlike an amplifier in that it includes filtering of the input tones. The two-tone interferers are lie in the stop band and attenuated by the filter. So, the IIP3 of the gain stage after filter stage is effectively increased due to the attenuation of interferers by the previous filter stages. Then, the IIP3 increase factor  $E_f$  can be defined as  $V_{IIP3}^2$  (before filtering)  $\cdot E_f = V_{IIP3}^2$  (after filtering).

Using the above analysis, (10) can be expressed as

$$I_{total} = \frac{1}{2R_{s}K} \frac{4V_{HP3}^{2}}{F} \left( \gamma + \frac{1}{A_{\nu_{1}}} \right) \left( 1 + \left| \frac{A_{o}}{A_{\nu_{1}}} \right|^{-3} \right) + \frac{1}{2R_{s}K} \frac{4V_{HP3}^{2}}{F} \frac{1}{E_{f}} \left( \gamma + \frac{A_{\nu_{1}}}{A_{total}} \right) \left( 1 + \left| \frac{A_{\nu_{1}} \cdot A_{o}}{A_{total}} \right|^{-3} \right)^{-3}$$

(11)

For a required specification of IIP3, NF and total gain, current consumption is a function of cell1 gain  $(A_{VI})$  and optimum value of  $A_{VI}$  can be obtained to minimize current consumption.

Overall current consumption of BBA chain versus cell1 gain is shown in Fig. 4 on condition that maximum gain of BBA chain  $A_{total}$ = 58dB and op-amp open loop gain  $A_o$ =77dB. As shown in Fig 4, overall current consumption of BBA chain is affected by choice of cell1 gain due to the trade-off between noise figure and IIP3. The current consumption is minimized at the cell1 gain of 20 dB as shown in Fig. 4.  $E_f$  is constant factor depending on the filter order and higher  $E_f$  leads to lower current consumption. However, filter order is limited by overall noise figure requirements.

Transistor-level circuit simulation results of SFDR versus cell1 gain at fixed total current consumption are shown in Fig. 5. Maximum SFDR is obtained at the cell1

gain of 20 dB. To minimize current consumption for a required overall specification leads to same results as maximize overall SFDR for a given current consumption.

A proposed baseband chain is based on Fig. 2, which alternates low pass filter (LPF) stages with programmable gain amplifiers (PGA). With gain step of 35 dB in the RF part, almost 40 dB range of receiver gain programmability needs to be offered by the baseband chain. This results in a PGA range of about from 18 to 53 dB with a resolution of 2dB. Using the proposed optimum design method, optimum allocation of design parameters of each stage for minimum current consumption at required specification of BBA chain is summarized in Table 1.

**Table 1.** Power optimum design parameters at required BBA chain specification.

|                    | T            | Cell1   |      | Cell2 |      |

|--------------------|--------------|---------|------|-------|------|

|                    |              | LPF1    | PGA1 | LPF2  | PGA2 |

| Sub-block<br>Spec. | Filter order | 2nd     |      | 4th   |      |

|                    | G (dB)       | 3       | 6~20 | 3     | 0~32 |

|                    | HP3 (dBm)    | 21.5    | -3.5 | 16.5  | -27  |

|                    | NF (dB)      | 34      | 31   | 49    | 46   |

| BBA chain          | Filter order | 6th     |      |       |      |

|                    | G (dB)       | 12 ~ 58 |      |       |      |

|                    | IIP3 (dBm)   | > 15. 5 |      |       |      |

|                    | NF (dB)      | < 35.7  |      |       |      |

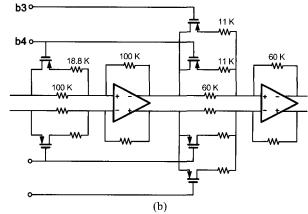

Fig. 6. Schematics of active RC filter (a) LPF1 (b) LPF2.

## III. CHANNEL SELECTION FILTER

The channel selection filter must provide the required selectivity. An active implementation of the filter must be also low noise so as not to degrade the overall receiver noise figure and be linear enough not to limit the receiver IIP3. The filter power dissipation is a also important parameter in low power application.

In this design, a second-order Chebyshev low-pass filter (LPF1) and a fourth-order Butterworth low-pass filter (LPF2) have been chosen due to the trade-offs between stopband attenuation and group delay. Additionally, first-order all-pass filter is required for group delay equalization. Active RC filter is very linear due to the linear passive components and high gain op-amps. Active RC filter is suitable for this design due to their high linearity performance compared to the other approach such as G<sub>m</sub>-C filter. Active RC implementations of the LPF1 and LPF2 are shown in Fig. 6(a) and Fig. 6(b), respectively.

Each op-amp has to drive a resistive and capacitive load, which requires the use of a two-stage op-amp. Fig. 3 shows the circuit of the two-stage op-amp used in filters and PGA. The first stage transistors are sized properly to minimize the flicker corner frequency. The op-amp has been compensated by using a Miller capacitance of 1.2 pF, along with a 11 k $\Omega$  resistor which produces a left-half plane zero and improves the op-amp phase margin. The total current drain of op-amp is equal to 112  $\mu$ A. The common-mode level at the op-amp output is set by the CMFB circuit as shown in Fig. 3. One problem of the CMFB circuits is their stability and to reduce the CMFB circuit gain, source degeneration resistors are used.

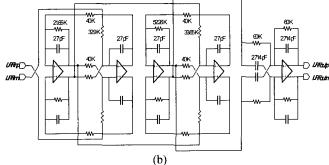

**Fig. 7.** schematics of programmable gain amplifier (PGA) (a) PGA1 (b) PGA2.

Each capacitor with an array of digitally controlled switch is used to make the filter tunable. Each unit capacitor in the filter is realized as 5-bit array of capacitances and  $\pm 50\%$  tuning range can be achieved, enough to overcome the RC process variations. The tuning accuracy is equal to 3%, which is good enough.

# IV. PROGRAMMABLE GAIN AMPLIFIER (PGA)

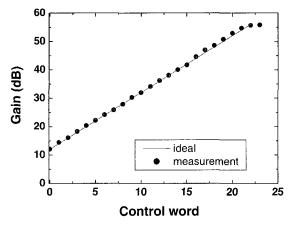

As well as in filters, op-amp based amplifiers are used due to excellent linearity performance. Programmable gain amplifiers used in this design are shown in Fig. 7. The different gains are realized by switching the feedback resistors and the resistors in the forward path. All gain stage result in a gain range from 12dB to 58dB with a step of 2dB and gain partitioning of the BBA chain is shown in Table I. The gain of the PGA in decibels changes linearly with control word by digitally controlled 5-bit switch.

Fig. 8. The chip microphotograph of the baseband analog circuits.

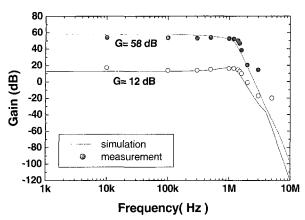

Fig. 9. Frequency response of receiver BBA.

Fig. 10. Programmable gain performance of receiver BBA.

Table 2. Measured performance summary of the receiver BBA.

| Noise figure at $50 \Omega$               | 31 dB               |  |  |

|-------------------------------------------|---------------------|--|--|

| Gain                                      | 12 ~ 55 dB          |  |  |

| IIP3 at 50 Ω<br>(2-tone: 5.2MHz, 10.2MHz) | 30 dBm              |  |  |

| Max. Group delay ripple                   | 80 nS               |  |  |

| Adj. Ch. Rejection (@5MHz)                | 72 dB               |  |  |

| Current consumption                       | 2.7 mA              |  |  |

| Supply voltage                            | 1.8 V               |  |  |

| Technology                                | 1P-6M, 0.18 μm CMOS |  |  |

With a large maximum gain of about 58 dB at baseband, the output offset of the receiver as well as the input offset of the baseband filter needs to be compensated in some way. A global servo loop is used for DC offset cancellation. DC offset is removed by measuring the output offset and subtracting it at the input using a low pass filter [5]. To keep the constant high pass corner frequency for different

gain setting, a programmable gain amplifier in the feedback integrator is used.

# V. EXPERIMENTAL RESULTS

The baseband analog circuit (BBA) including filters and PGAs has been fabricated in 0.18  $\mu$ m 1-poly 6-metal CMOS process. Fig. 8 shows the microphotograph of the BBA. The area of baseband analog circuit including filters, PGA and bias circuit is 1.5 mm<sup>2</sup>.

The frequency response of receiver BBA is shown in Fig. 9. Cut-off frequency is almost same at different gain setting from 12 dB to 55 dB. The simulated frequency response of the receiver is also shown and it is very close to the measured value. The gain characteristics of the receiver BBA with the control words are shown in Fig. 10. The gain of the PGA in decibels changes linearly with control word and error of the gain is smaller than 0.7 dB.

An IIP3 of about 30 dBm at a maximum gain of 55 dB is obtained at 2.7 mA current consumption. In the proposed receiver BBA, high linearity performance is obtained by using active RC filter implementation and high gain op-amp based PGAs. The measurement results of the cascaded receiver BBA are summarized in Table 2.

# VI. CONCLUSION

A low power CMOS receiver baseband analog circuit based on alternating filter and gain stage is reported. For the given specifications of the baseband analog block, optimum allocation of the gain, IIP3 and NF of the each block was performed to minimize current consumption. The fully integrated receiver BBA chain is fabricated in 0.18  $\mu$ m CMOS technology and IIP3 of 30 dBm with a gain of 55 dB and noise figure of 31 dB are obtained at 4.86 mW power consumption.

#### ACKNOWLEDGEMENT

This work is supported by MICROS Research Center and Samsung Electronics.

## REFERENCES

- [1] P. Choi et al., "An experimental coin-sized radio for extremely low power WPAN application at 2.4GHz," *IEEE ISSCC*, Feb. 2003, pp. 92-93.

- [2] C. Cojocaru *et al.*, "A 43mW Bluetooth transceiver with -91dBm sensitivity," *IEEE ISSCC*, Feb. 2003, pp. 90-91.

- [3] T. Soorapanth, et al., "RF linearity of short-channel MOSFETs," *1st International Workshop on Design of Mixed-Mode Integrated Circuit and Applications*, pp. 81-84, 1997.

- [4] A. A. Abidi, "General relations between IP2, IP3 and offsets in differential circuits and the effects of feedback", *IEEE Transaction on Microwave Theory and Techniques*, vol.51, no.5, pp.1610-1612, May., 2003.

- [5] R. Harjani, J. Kim, and J. Harvey, "DC coupled IF stage design for a 900-MHz ISM receiver", in *IEEE Journal of Solid-State Circuits*, vol.38, no.1, pp.126-134, Jan., 2003.

Minkyung Lee was born in Jeongup, Korea, on August 13, 1978. She received the B.S. degree and the M.S. degree in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea,

in 2002 and 2004, respectively. In 2004, she joined the Samsung Electronics and she is currently a research engineer in Telecommunication network. Her current research interests include CMOS RF integrated circuits and wireless communication.

Ickjin Kwon received the B.S. degree and the M.S. degree in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1998 and 2000, respectively, and the Ph.D.

degree in electrical engineering and computer science from the KAIST, in 2004. In 2004, he joined the Samsung

Advanced Institute of Technology (SAIT) and he is currently a research engineer in communication and network lab. in SAIT. His current research interests include CMOS RF integrated circuits and receiver design for wireless PAN.

**Kwyro Lee** received the B.S. degree in Electronics Engineering from Seoul National University in 1976 and the M.S. and Ph. D. degrees from the University of Minnesota, Minneapolis in 1979 and 1983 respectively, where he did many pioneering works for

modeling Heterojuction Field Effect Transistor. After graduation, he worked as an Engineering General Manager in GoldStar Semiconductor Inc. Korea, from 1983 to 1986, responsible for development of first polysilicon CMOS products in Korea. He joined KAIST in 1987 in the Department of Electrical Engineering, where he is now a Professor. His research interests are focused on RF device, circuit and polylithic integration of heterogeneous system on a single chip. He led the development of AIM-Spice and is the principal author of the book titled, "Semiconductor Device Modeling for VLSI", 1993, Prentice Hall. He is a Senior Member of IEEE and a Life Member of IEEK. He served as the Chairman of IEEE Korea Electron Device Chapter and is currently serving as the elected member of IEEE EDS AdCom. He has also been working as the Director of MICROS(Micro Information and Communication Remote-object Oriented Systems) Research Center since 1997.