# 표준 셀 라이브러리 P&R 포팅과 테스트 칩의 설계

# P&R Porting & Test-chip implementation Using Standard Cell Libraries

임호민\*, 김남섭\*, 김진상\*, 조원경\*

Ho-min Lim\*, Nam-sub Kim\*, Jin-sang Kim\*, Won-kyung Cho\*

#### 요 약

본 논문에서는 최신의 미세공정인 0.18um CMOS 공정을 이용한 표준 셀 라이브러리를 설계하고, 이를 P&R(Placement and Routing) CAD 툴에 사용할 수 있도록 포팅한다. 제작결과를 검증하기 위하여 간단한 테스트칩을 제작하였으며 설계에 사용된 표준 셀 라이브러리는 0.18um 아남반도체의 공정이다. 이러한 설계 및 제작과정을 통하여 최신의 미세공정을 이용하여 디지털 시스템의 자동설계가 가능함을 확인하였다.

#### **ABSTRACT**

In this paper, we design standard cell libraries using the 0.18um deep submircom CMOS process, and port them into a P&R (Placement and Routing) CAD tool. A simple test chip has been designed in order to verify the functionalities of the 0.18um standard cell libraries whose technical process was provided by Anam semiconductor. Through these experiments, we have found that the new 0.18um CMOS process can be successfully applied to automatic digital system design.

Key words: VLSI, CAD, CBIC, P&R

#### I. 서 론

표준 셀 라이브러리는 여러 가지 ASIC(Application Specific IC)이나 VLSI(Very Large Scale Integration) 설계방법중 semi-custom방식인 CBIC(Cell Based IC)방법을 이용할 때 사용된다. 이는 FPGA(Field Programmable Gate Array)를 이용한 방법보다 훨씬 더 디자인에 최적화된 결과를 제공하며, Full custom IC방법보다 훨씬 더 간단하고 쉬운 설계환경을 제공해 준다 [2][3].

Semi-custom 방식으로 설계하는 설계자들은 이

셀 라이브러리에 절대적으로 의존하여 디지털 시스템을 설계하고 검증한다. 따라서 설계한 디자인의 동작주파수, 크기, 전력소모 등의 성능은 절대적으로 셀라이브러리의 성능에 따라 좌우되기 마련이다.

따라서 CBIC기법을 이용하기 위하여 절대적으로 필요한 것이 바로 Cell Library이며, 본 논문에서는 0.18um 공정용 Cell Library를 개발한 후 이를 테스 트하기 위하여 테스트 칩을 제작하였다.

또한 Automatic P&R환경을 제공하기 위하여 EDA툴에 이 라이브러리를 포팅하고, 포팅한 라이 브러리를 이용하여 칩을 제작하여 포팅이 정확히 이

<sup>\*</sup> 경희대학교 전자공학과

<sup>·</sup> 논문번호 : 2003-2-14

<sup>·</sup>접수일자: 2003년 4월 25일

루어 졌는지도 검증할 수 있도록 하였다.

일반적으로 테스트칩은 다음과 같은 몇 가지의 목적에 의해서 설계된다.

- I) 각 셀의 동작특성 파악.

- Ⅱ) 각 셀의 타이밍 측정.

- Ⅲ) 각 셀의 레이아웃의 정확성(디자인 룰).

- IV) 합성툴의 결과가 정확한지를 검증.

- V) 최적화된 P&R을 수행할수 있는지를 검증

본 논문에서는 기본적으로 I) 항목의 동작이 올바른가를 전제로 테스트칩을 설계하였으며, 그에 따라 III), IV), V)의 항목도 함께 검증하였다. 각 셀의 타이밍 측정은 다른 칩을 통하여 할 수 있으며, 설계한테스트 칩에서는 동작특성만을 파악하였다.

본 논문에서 설계한 칩은 0.18um 최신공정을 이용하여 설계한 셀 라이브러리의 동작특성을 검증하기 위한 것으로, 설계한 모든 셀에 대하여 모든 입력을 제어하고, 모든 출력을 관측할 수 있도록 설계하였다. 설계한 테스트 칩의 목적은 각 셀의 기능의 정확성을 검증하기 위한 것이다.

# Ⅱ. P&R 도구 포팅

#### 2-1 설계 흐름도

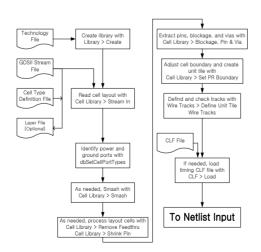

본 논문에서 사용한 Apollo II P&R 도구 [1] P&R을 수행할 때 실제 레이아웃 데이터를 사용하

그림 1. Placement & Routing Design Flow Fig. 1. Placement & Routing Design Flow

지 않고 FRAM이라고 불리는 가상의 셀을 사용하여 P&R과정을 수행한다. FRAM셀은 실제 레이아웃 데이터에서 P&R과정에 필요한 데이터만을 추출한 함축된 레이아웃이라고 할 수 있으며, 이와 같은 FRAM을 사용하여 P&R을 할 경우 데이터의 크기가 감소되므로 빠른 시간내에 P&R이 가능하다. 그러나 이와 같은 FRAM은 실제 레이아웃 데이터가아니므로 최종 칩제작시에는 반드시 실제 레이아웃으로 변환을 시켜 주어야 한다.

그림 1은 FRAM셀 제작을 위한 전체적인 흐름도 이며 각 블록에 대한 설명은 다음과 같다.

#### 2-1. Input Data

FRAM 제작을 위하여 필요한 입력 데이터는 크 게 다음과 같은 3 종류의 데이터 파일이 필요하다.

# ■ Technology File

Technology File은 Apollo II에서 칩 제작과정에 필요한 여러 가지 정보를 저장한 파일로서 각 Layer에 대한 정의, Routing Pitch, DRC Rule, 툴에 대한 옵션 등이 포함되어 있다.

#### ■ GDSII Format의 Primitive Cell

GDSII는 Layout data의 표준규격으로서 Apollo II에서는 기본적으로 Layout Data를 읽을 때 GDSII Format의 data를 읽을 수 있는 기능을 갖고 있다.

#### ■ Cell Type Definition File

Apollo II는 기본적인 Standard Cell 이외에 MACRO, PAD등과 같은 셀의 사용을 지원하며 이를 위하여 각 셀들의 역할을 기술하는 파일이 필요하다.

#### 2-3 Stream in, smash, extract blockage

생성된 라이브러리에 실제 레이아웃 데이터를 읽는 작업은 Stream In을 함으로 수행한다. Stream In은 생성된 라이브러리에 실제적인 GDS II 포맷의 데이터를 읽어 들이는 과정을 수행하며 이렇게 읽혀 진 데이터는 임시 데이터로 저장되어 FRAM Cell추출에 활용이 되어진다.

일반적으로 레이아웃 데이터를 만들 때 계층적인

구조로 만든다. 그러나 레이아웃 데이터로부터 FRAM을 추출하기 위해서는 레이아웃안의 모든 셀들이 Flatten되어져 있어야 하므로 Apollo II에서는 이와 같은 기능을 Smash 명령이 수행하게 된다. 읽혀진 데이터로부터 메뉴바의 Smash옵션을 사용하면 읽혀진 레이아웃 데이터를 모두 Flatten 시킬 수 있다.

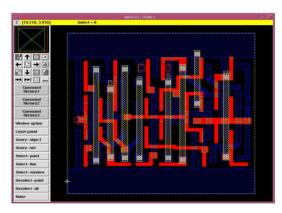

그 다음은 blockage를 추출하게 되는데, Blockage 란 실제로 라우팅 CAD 툴이 Over-the-Routing 과정을 수행할 때 라우팅 레이어가 지나가서는 안될 부분을 일컫는다. 일반적으로 전체 블록을 Metal 1 blockage로 설정하여 셀 안에서의 Metal 1 라우팅을 금지하도록 하고 있으나 본 제작에서는 셀 내부에서도 Metal 1 라우팅이 가능하도록 설정하였으며 설정된 내용을 아래 그림 2에 나타내었다.

그림 2. 추출된 blockage의 예 Fig. 2. example of extracted blockage

추출된 Blockage 부분은 Blockage의 생성외에 각 핀의 내용을 해당되는 Layer에 할당하는 역할도 수 행된다. 그림 2는 이와 같은 Blockage 생성과정을 통하여 생성된 Blockage의 예를 보여준다. 실제 셀 제작에서는 Metal 1뿐만 아니라 Metal 2 도 동시에 사용이 되었으므로, Metal 1, Metal2의 Blockage들 이 생성된 것을 확인 할 수 있고 또한 각 핀이 해당 되는 레이어에 할당되었음을 표시하여 준다.

#### 2-4 Create Cell Boundary

Cell Boundary 는 셀의 경계를 나타내는 것으로

서 일반적으로 레이아웃 제작시 Boundary 레이어를 설정함으로써 만들어진다.

Apollo II에서는 Boundary 레이어가 설정되어 있지 않은 셀들에 대해서 자동적으로 Boundary 레이어를 설정하는 기능을 갖고 있다. 본 제작에서는 Boundary의 설정을 확실히 하기 위하여 각 셀에 대하여 Cell Boundary를 다시 설정하였다.

#### 2-5 Set PR boundary

PR Boundary는 Placement & Routing Boundary 로서 이것은 실제적으로 P&R 과정시 셀의 경계를 나타내는 중요한 설정 항목이다.

Apollo II의 각 셀이 배치될 때 서로 겹쳐서 배치가 가능하도록 되어 있으며(double back) 또한 크기가 다른 셀들의 배치가 가능하기 때문에 이와 같은 셀의 배치를 위해서는 실제 셀 경계와는 다르게 PR 경계를 설정하여야 한다.

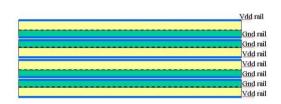

본 제작에서는 칩면적의 최소화를 위하여 그림 3 과 같은 Double-Back이 가능하도록 PR Boundary 를 설정하였다.

그림 3. 더블 백 Fig. 3. Double back

그림 4. 설정된 PR 경계 Fig. 4. set PR boundary

그림 4는 설정된 PR Boundary를 나타낸다. 이와 같이 설정된 PR Boundary는 그림과 같이 파워레일 의 중간부분에 위치하게 되고 이렇게 함으로써 인 접한 Power와 Ground가 서로 연결될 수 있도록 하 였다.

## Ⅲ. 시험 칩 제작

본 논문에서 설계한 테스트 칩은 세 개의 블록으로 나누어 설계하였다.

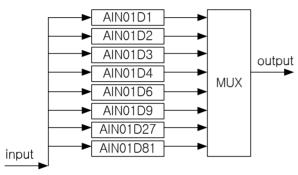

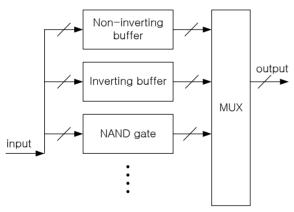

그림 5. 인버팅 버퍼의 세부블럭 Fig. 5. detailed block of Inverting buffer

그림 6. 블록 1의 구조 Fig. 6. structure of Block 1

첫 번째 회로는 모든 셀의 입력을 공유하고, 모든 셀의 출력을 멀티플렉싱하여 결과를 확인할 수 있도 록 하였다. 이는 제한된 핀 안에 모든 셀의 입출력을 제어하고 관측하기 위해서 할 수 있는 최선의 방법 이며, 설계된 멀티플렉서가 올바르게 동작을 한다는 가정 하에 최소한의 핀을 사용하게 되었다. 또한 이 회로는 합성기를 통하여 합성하지 않고 Verilog 파일에서 모든 셀을 각각 파생한 후 바로 P&R을 수행하였다. 동작특성만 검증하므로 각 셀은 구동력에 관계없이 그 기능에 따라 다음 그림 5와 6과 같이 블록을 나누었다.

두 번째와 세 번째 블록은 합성 라이브러리의 검증을 포함하는 것으로, 간단한 조합회로와 순차회로가 포함되는 시스템을 구현하여 합성기를 통하여 합성 한 후 P&R을 수행하였다.

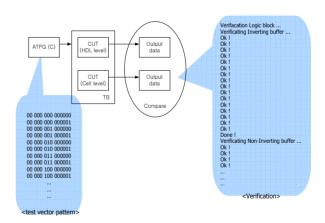

## 3-1 시험방법

테스트 패턴은 진리표를 이용하여 ATPG를 C언어로 작성하여 사용하였다. 모든 입력에 대하여 정확한 출력값을 예상하고, 예상된 출력값과 회로를시물레이션한 출력값을 비교하여 동작을 검증하였다. 그림 7에서 볼 때에 제일 왼쪽에 만들어진 테스트 벡터를 HDL testbench에 입력하여주며, 입력된테스트 벡터는 HDL level의 모델과 Cell level모델,두개의 모델로 입력된다. 각 모델에서 출력된 데이터를 다시 ATPG에서 비교하여 같은가 다른가를최종적으로 출력하여 주게 된다.

그림 7. 테스팅 환경 Fig. 7. testing environment

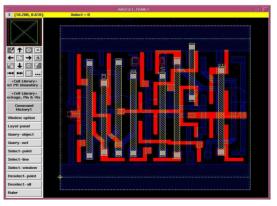

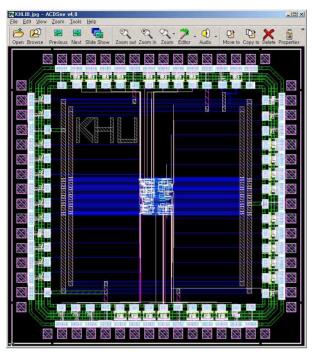

# 3-2 P&R 결과

PAD를 포함한 전체의 칩의 레이아웃을 다음 그림에 나타냈으며, 2mm x 2mm의 TQFP 타입의 칩으로 제작될 예정이다.

그림 8. test chip의 레이아웃 Fig. 8. layout of test chip

## Ⅳ. 결 론

본 논문에서는 표준 셀 라이브러리를 P&R툴에 맞게 포팅하고, 포팅한 라이브러리를 이용하여 테스

#### 임 호 민(林虎珉)

2001년 8월: 경희대학교 전자공 학과(공학사)

2003년 8월: 경희대학교 전자공 학과(공학석사)

2003년 5월~현재:LG전자기술원 연구원

# 김 남 섭(김남섭)

1990년 2월: 경희대학교 전자공 학과 (공학사)

1992년 2월 : 경희대학교 전자 공학과 (공학석사)

2000년 2월~현재: 경희대학교 전자공학과 박사과정 트칩을 설계하여 기능을 검증하였다. 설계된 테스트 칩은 현재 공정에 맞추어 Fab-in중이며, 6월경에 64 핀 TQFP 패키지 형태로 제작되어 Fab-out될 것이다. Fab-out된 칩은 시물레이션 결과와 일치하는지를 ATS2등의 테스트 장비를 이용하여 검증하게 되고, 그 결과에 따라 라이브러리의 제작이 제대로 되었는지를 확인할 수 있다.

## 참 고 문 헌

- [1] "IC Layout Command Reference Manual", Avant!, 1999.

- [2] Y.D.Bae, H.J.Song, "Design of Function Verification Chip for ASIC Cell Library," 4th IDEC MPW(Multi-Project Wafer) Workshop, pp. 66-70, Jan. 1999.

- [3] Rung-Bin Lin; Isaac Shuo-Hsiu Chou; Chi-Ming Tsai, "Benchmark circuits improve the quality of a standard cell library" Proceedings of the ASP-DAC '99. Asia and South Pacific, Page(s): 173-176 vol.1, 18-21 Jan 1999.

## 김 진 상(金진상)

1985년 2월: 경희대학교 전자공학과(공학사) 1987년 2월: 경희대학교 전자 공학과(공학석사) 2000년: 콜로라도주립대 전기 및 컴퓨터공학과(공학박사) 현재 경희대학교 전자정보학부 전 임강사

## 조 원 경(조원경)

1971년 2월: 경희대학교 전자 공학과(공학사) 1973년 2월: 한양대학교 전자 공학과(공학석사) 1986년 8월: 한양대학교 전자 공학과(공학박사) 현재 경희대학교 전자정보학부

정교수