# SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> 이중 박막의 C-V 특성

論 文 52C-10-8

# Capacitance-Voltage Characteristics in the Double Layers of SiO2/Si3N4

洪能 杓\*・洪 眞 雄\*\* (Nung-Pyo Hong・Jin-Woong Hong)

Abstract - The double layers of SiO2/Si3N4 have superior charge storage stability than a single layer of SiO2. Many researchers are very interested in the charge storage mechanism of SiO2/Si3N4 [1,2]. In this paper, the electrical characteristics of thermal oxide and atmospheric pressure chemical vapor deposition (APCVD) of Si3N4 have been investigated and explained using high frequency capacitance-voltage measurements. Additionally, this paper will describe capacitance-voltage characteristics for double layers of SiO2/Si3N4 by "Athena", a semiconductor device simulation tool created by Silvaco, Inc.

Key Words: Electret, Oxide (SiO2), Nitride (Si3N4), C-V Plot, HTB(High Temperature Bias)

#### 1. Introduction

Many applications in the field of sensors and actuators benefit from the possibility of advanced charge storage in electrets as an important component. Various devices based on the characteristics of electrets, such as microphones, air filters, and radiation dosimeters, have already been proposed and utilized in the industry [2, 3].

SiO2 is well known as a superior electrets material. Unfortunately, the thermal oxide layer shows compressive stress and significant surface conduction, which affects the charge storage lifetime [4]. In recent years, the double layers of SiO2/Si3N4 electrets were widely investigated because of their excellent charge storage stability [5,6]. Due to the tensile stress of the double layers of SiO2/Si3N4, electrets can be directed to the compensate the internal stress by variation of the ratio of their layer thickness [7]. In this paper, the electrical characteristics of thermal oxide and atmospheric pressure chemical vapor deposited (APCVD) nitride were investigated using high frequency capacitance-voltage measurements.

This paper will describe the C-V characteristics of double layers SiO2/Si3N4 with the help of the semiconductor device simulation tool, "Atlas" manufactured by Silvaco, Inc.

\* 正 會 員:光云大 工大 電氣工學科 博士課程

\*\* 正 會 員:光云大 工大 電氣工學科 教授・工博

接受日字: 2003年 6月 7日 最終完了: 2003年 9月 20日

# 2. Experimental

# 2.1 Composition of samples

We started with a 100[mm] silicon wafer (manufactured by ShinEtsu Co.), and <111> oriented and p-doped materials (substrate resistivity of  $25[\Omega \, \mathrm{cm}]$ ) were chosen as substrate.

These wafers were thermally oxidized at 1000[°C] for several minutes in quartz furnaces. To obtain a higher density thermal oxide, they are made with two additional dry oxidation steps and are thus called dry-wet-dry structures. The photograph of the wafer probe station for capacitance-voltage characteristics is shown in Photo 1.

**Photo. 1** The photo of wafer probe station for capacitance-voltage characteristics.

The Si3N4 layer was deposited by the APCVD (Atmospheric Pressure Chemical Vapor Deposition) method at 780[°C]. The desired film thickness was extracted by variation of the deposition duration and then measured using a Nanometrics210 (Film Thickness System).

The silicon wafers were made from the front side with an evaporated aluminum electrode of 1[\mu m] thickness. The unwanted SiO2 layer and Si3N4 films on the backside of the substrate wafer were removed by chemical etching using the SEG102(Spin Processor Co.). 1[\mu m] of aluminium was deposited on the oxide. The mask for C-V measurement was used. The composition of the samples is provided in Table 1.

Table 1 The sample composition information

| No. | SiO2 Thickness [A] | Si3N4 Thickness [Å] |

|-----|--------------------|---------------------|

| #1  | 2000               | 1000                |

| #2  | 2000               | 1500                |

| #3  | 2000               | 2000                |

| #4  | 3000               | 1000                |

| #5  | 3000               | 1500                |

| #6  | 3000               | 2000                |

| #7  | 3000               | 0                   |

| #8  | 0                  | 1500                |

Total capacitance of the double layers per unit area were calculated with

$$\frac{1}{C_{tot}} = \frac{1}{C_{ox}} + \frac{1}{C_{nit}} \tag{1}$$

where  $\mathcal{E}_0$ ,  $\mathcal{E}_{ox}$  and  $\mathcal{E}_{nit}$  are the relative permittivity of the vacuum, SiO2 and Si3N4, respectively. The equivalent thickness of the double layer is

$$d_{tot} = d_{ox} + (\frac{\varepsilon_{ox}}{\varepsilon_{nit}}) \cdot d_{nit}$$

(2)

#### 3. Results and Discussion

To investigate the capacitance voltage characteristic exactly and to compare it theoretically, computer simulation and actual testing were executed.

#### 3.1 Simulation result

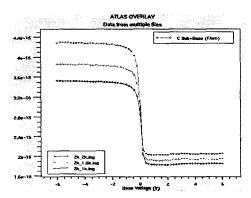

Figures 1 and 2 show the simulated capacitance-voltage characteristics at several samples with varying thickness. We can see that the capacitance value decreases with increasing positive gate bias, from 7[V] to +7[V].

This thickness dependent characteristic can be explained by a simple diagram. For negative bias, the majority carrier (hole) in the p-substrate follows the accumulation mode near the p-substrate surface.

Fig. 1 C-V characteristic due to various thickness.

When the gate bias voltage is lower than 1[V], the hole carrier can be accumulated. The capacitance value reaches a maximum and does not change further with a negative bias. In this case, the total capacitance value of the sample equals the capacitance of the  $SiO_2(C_{ox})$  and the capacitance of the  $Si_3N_4(C_{nit})$  series connection.

Increasing the positive gate bias, the depletion capacitance value by majority carrier in p-substrate far away from the surface in silicon bulk is added to the series connection. Due to this reason, total capacitance

value

$$C_{tot} = (C_{nit} + C_{ox} \pm C_{dep})^{-1}$$

decrease.

Fig. 2 Capacitance of the sample at different thickness.

Figure 3 shows the simulated potential profile and electric field profile at double layers of SiO<sub>2</sub>(2000 [Å])/Si<sub>3</sub>N<sub>4</sub>(1000[Å]).

The potential distribution and electric field in SiO2/Si3N4 electrets samples has been estimated and the electric field crowding phenomenon near the base electrode edge can be seen. In the case of potential distribution, it gets the uniformity potential is under the base electrode.

SiO√Si₃N₄ 이중 박막의 C-V 특성 465

Fig. 3 Simulated potential profile and electric field distribution of the SiO2(2k[Å])/Si3N4(1k[Å]) sample.

Fig. 4 Simulated model of the SiO2(3[Å]) and Si3N4(1.5 [Å]) sample

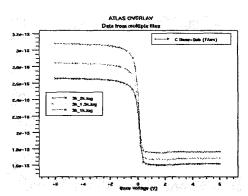

Figure 4 shows the simulation structure model single layers of SiO2 and Si3N4, respectively. Figure 5 shows the simulated results of capacitance characteristics in single layer and double layers, respectively. In contrast, for the single Si3N4 layer, thickness-dependent capacitance value was observed at the base bias by high dielectric constant and lower sample thickness. The single layer of Si3N4 has a very high capacitance value during the negative base biased state due to the high dielectric constant and lower thickness as compared to other samples.

Fig. 5 Capacitance of the samples at SiO2 and Si3N4 single layer and double layer, respectively.

# 3.2 Experimental results

To measure the mobile charge of SiO2/Si3N4 double layer, we progress to HTB, which adds both positive & negative voltage at high temperatures. This experiment helps to maximize the ion's mobility at high temperatures.

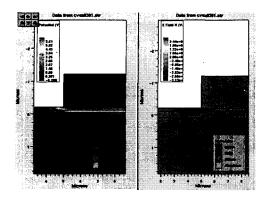

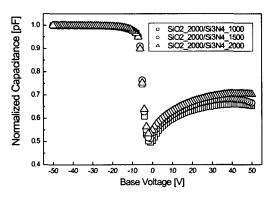

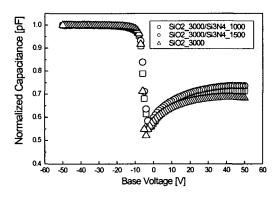

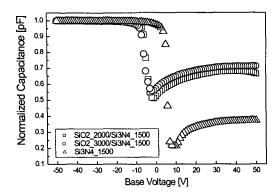

Figures 6 and 7 show the experimental capacitance-voltage characteristics of several samples with varying thickness. We can see that the actual result decreases with increasing positive gate bias, from 50[V] to +50[V].

This plot provides information on the location in the double layers of SiO2/Si3N4 of any contamination. The total capacitance value increase with increasing Si3N4 thickness during the positive base bias in figures 6, 7, and 8.

Fig. 6 Capacitance characteristics of the SiO2(2k[Å]) /Si3N4(1k[Å], 1.5k[Å], 2k[Å]) samples.

Fig. 7 Capacitance characteristics of the SiO2(3k[Å]) /Si3N4(1k[Å], 1.5[Å]) and single SiO2(3k[Å]).

Specially, in figure 8, it can be confirm that Si3N4 single layer's dielectric constant is about twice as much as than SiO2. Therefore, under normalized C-V plot, we can check whether it shows low value around the positive bias compared to SiO2/Si3N4 double layers.

Fig. 8 Capacitance characteristics of the SiO<sub>2</sub>(2k[Å], 3k[Å])/Si<sub>3</sub>N<sub>4</sub>(1.5k[Å]) and single Si<sub>3</sub>N<sub>4</sub>(1.5k[Å]).

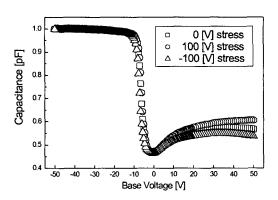

Figure 9 illustrates the experimental capacitance-voltage characteristics of the SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> sample after thermal stress. The actual result shows a decrease with increasing positive gate bias, from 50[V] to +50[V].

Two stress cycles should be used in this experiment. It is necessary to measure all the mobile ions in the double layers sample. The first stress of 100[V] forces the mobile ions to a known position. The second stress of 100[V] then moves the ions across the double layers after reaching a 200[°C] soak temperature.

The shift between the second(+100[V] stress plot) and third plots(-100[V] stress plots) provides the most accurate mobile charge.

Fig. 9 Capacitance characteristics of the SiO2(3k[Å])/ Si3N4(1k[Å]) sample after thermal stress.

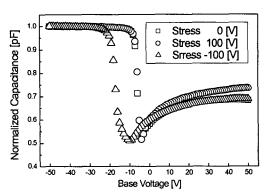

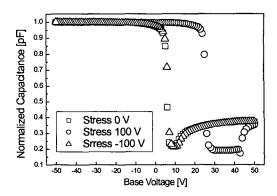

Different capacitance-voltage characteristic values at negative stress bias and positive stress bias in single layers can be achieved.

In figure 9, we confirm that the capacitance-voltage characteristics at the positive bias condition are stable. However, we can find voltage shift with about 10 to 20[V] for single layers in figure 10 and 11. From figure 10, we can forecast the quantity of mobile charge of SiO2 single

layer followed by C-V pilot's shifted value by THB treatment. In figure 11, we can confirm that C-V plot has been affected by the movement of positive ions. Compared to SiO2 single layer, it has been moved by +100[V] stress to Si3N4-Si interface, whereas, the capacitance multiplied by  $\triangle$  V(shifted voltage) is mobile ionic charge.

Fig. 10 Capacitance characteristics of the single layer SiO<sub>2</sub>(3k[Å]) sample after thermal stress.

Fig. 11 Capacitance characteristics of the single layer Si3N4(1.5k[Å]) sample after thermal stress.

The following equation describes the relationship between the flat-band voltage shift and the total charge.

$$\Delta V_{FB} = \frac{Q_m}{q} \frac{T_{tot} \cdot q}{K_{tot} \cdot \varepsilon_0} \tag{3}$$

Therefore, the total mobile charge, Qm, is found by definition from the flat-band voltage.

$$Q_m = q \cdot \Delta V_{FB} \frac{2.1E10}{T_{tot}} \left[ C / cm^2 \right]$$

(4)

Table 2 shows total results of experiment results. The SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> double layer's voltage has been changed from max. 0.43 [V] to min. 0.19[V]. However, on the other

SiO₂/Si₃N₄ 이중 박막의 C-V 특성 467

side, single layer can be changed from max. 19.53[V] to min. 11.38[V]. According to these figures, we can learn that under single layer, the mobile charge's movement is unrestrained but under double layers, the mobile charge's movement is very limited. In addition, from the charge stability view point, double layers have greater predominance characteristics than single layer.

Table 2 Charge measuring data by C-V plot after HTB.

| Condition  | Vfb range             | Qm *e <sup>11</sup> [C/cm <sup>2</sup> ] |

|------------|-----------------------|------------------------------------------|

| 2000/1000  | -6.49 ~ -6.86         | 4.41                                     |

| 2000/1500  | -6.47 ~ -6.78         | 4.08                                     |

| 2000/2000  | -6.83 ~ -7.02         | 4.09                                     |

| 3000/1000  | -7.73 ~ <b>-</b> 8.16 | 4.26                                     |

| 3000/1500  | -7.68 ~ -7.97         | 3.97                                     |

| 3000/2000  | -7.48 ~ -7.78         | 3.67                                     |

| SiO2_3000  | -7.12 ~ -18.5         | 4.74                                     |

| Si3N4_1500 | 24.9 ~ -6.86          | -17.1                                    |

# 4. Conclusion

We investigated the SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> electrets according to the various layer structures in order to obtain the optimal condition.

In double layers of SiO2/Si3N4 electrets, by increasing the thickness of the Si3N4 layer reduces the charge stability. The actual capacitance voltage value depends slightly on the thickness of the Si3N4 layers. The traps, which are responsible for the charge stability in the investigated electrets, are much deeper than the traps in the single layer. We supposed the origin of these traps might be the interface between the SiO2 and Si3N4 layers.

In this paper, we can see the peculiarity of charge stability of SiO2(2k[Å])/Si3N4(2k[Å]) by the experiment of single layer and SiO2/Si3N4 double layers. A more detail dissertation of double layer electret's charge stability can be achieved by additional TSC experiments.

Futher study will help in understanding more about charge stability. We will update the status once additional investigation has been performed.

# References

- [1] H. Amjadi, Charge storage in double layers of thermally grown silicon dioxide and APCVD silicon nitride, *IEEE Transations on the Electrical Insulation*, vol. 6, pp. 852-857, December 1999

- [2] R. Kressmann, G. M. Sessler, P. Gunther, Electret,

- Spinger, Berlin, pp. 1-11, 1987.

- [3] Ho Chee Lai, Preston Murphy, and Mireille Latour, Improved silicon dioxide electret for silicon-based integrated microphones, Proceedings of the 8th International Symposium in Electret ISE8, Paris, pp. 949-954, 1994.

- [4] Nung-Pyo Hong, Doo-Jin Choi, Tae-Sun Lee, Byung-Ha Choi, Tae-Hoon Kim, Jin-Woong Hong The electrical characteristics of oxide due to processing condition, in *Proceedings of IEEE ICSD2001 Conference*, Eindhoven, Netherlands, pp. 211-214, 2001.

- [5] Yonggan Pan, Zhongfu Xia, Xiaoqin Zhang, Yewen Zhang, Charge storage characteristics for double layer of Si3N4/SiO2 and single layer of Si3N4, Proceedings of the 10th International Symposium on Electret ISE10, pp. 391-394, 1999.

- [6] W. Olthuis, P. Bergveld, On the charge storage and decay mechanism in silicon dioxide, *IEEE Transactions on Electrical Insulation*, vol.27, No.4, pp. 691-697, 1992.

- [7] M. Copel, P. R. Varekamp, D. W. Kisker, F. R. McFeely, Nucleation of chemical vapor deposition silicon nitride on silicon dioxide, *Applied Physics Letters*, vol.74, pp. 1830-1832, March 1999.

# 저 자 소 개

# 홍 능 표 (洪 能 杓)

1970년 8월 11일생. 1994년 광운대학교 전기공학과 졸업, 1996년 동 대학원 전기공학과(석사), 1998년~현재 동 대학원 전기공학과 박사과정, 1994년1월~1999년4월 삼성전자(주) 전임연구원, 1999년4월~현재페어차일드 코리아 반도체(주) TRIAC 개

발 선임연구원.

Tel: 82-32-680-1764, Fax: 82-32-680-1823

E-mail: nungpyo@korea.com

# 홍 진 웅(洪眞雄)

1955년 2월 23일생. 1982년 한양대학교 전기공학과 졸업, 1982년~1987년8월 광 운대학교 대학원 전기공학과 졸업(공박), 1989년3월~현재 광운대학교 전자정보대 학 전기공학과 교수, 1992년7월~1993년7 월 일본나고야대학 전기공학과 해외공동

연구원, 2000년 7월~2001년 7월 일본큐슈공대 전기공학과 객원교수, 2003년 2월~2005월 1월 광운대학교 정보과학교육원 원장.

Tel: 82-02-940-5145. Fax: 82-02-915-4630

E-mail: ealab@daisy.kw.ac.kr