# A 1.8 GHz SiGe HBT VCO using $0.5 \mu$ m BiCMOS Process

Ja-Yol Lee<sup>1</sup> · Sang-Heung Lee<sup>1</sup> · Jin-Young Kang<sup>1</sup> · Kyu-Hwan Shim<sup>1</sup> · Kyoung-Ik Cho<sup>1</sup> · Seung-Hyeub Oh<sup>2</sup>

## **Abstract**

In this paper, we fabricated an 1.8 GHz differential VCO using a commercial 0.5  $\mu$ m SiGe BiCMOS process technology. The fabricated VCO consumes 16 mA at 3 V supply voltage and has a 1.2×1.6 mm² chip area. A phase noise measured at 100 kHz offset carrier is -110 dBc/Hz and a tuning range is 1795 MHz $\sim$ 1910 MHz when two varactor diodes are biased from 0 V to 3 V.

Key words: SiGe, BiCMOS, VCO, Phase Noise, Flicker Noise.

## I. Introduction

The phase noise of a VCO has significant effects on digita cellular systems. A SiGe device is a good candidate for designing an oscillator of low power and

low phase noise since that device has advantages of low turn-on voltage and good phase noise characteristics due to low 1/f noise and noise figure [1],[2].

In this paper, a fully monolithic differential VCO is designed and fabricated using a commercial 0.5  $\mu$  m

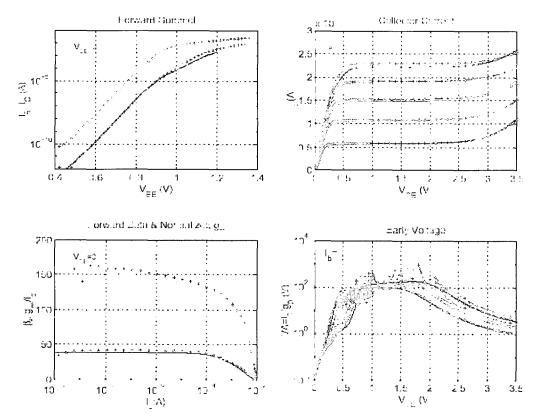

Fig. 1. SiGe HBT DC characteristics.

Manuscript received November 16, 2002; revised January 13, 2003.

<sup>&</sup>lt;sup>1</sup>SiGe Device Teams, ETRI, Daejon, Korea.

<sup>&</sup>lt;sup>2</sup>Dept. of Electronics Enigeering, Chungnam National University, Daejon, Korea.

SiGe BiCMOS process. The fabricated VCO achieved a low phase noise of -110 dBc/Hz at 100 kHz offset carrier and 115 MHz tuning bandwidth. The third harmonic suppression of more than 22 dBc was obtained. A current 16 mA at 3V supply voltage runs in the VCO of  $1246 \times 1649 \,\mu$  m<sup>2</sup> chip area.

## II. SiGe HBT and Inductance Characteristics

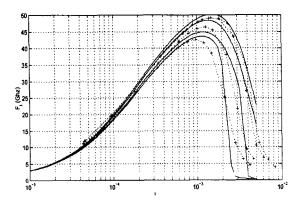

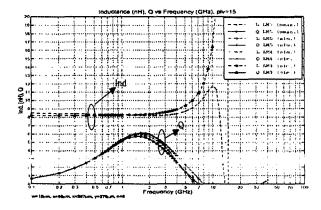

In this section, The DC and AC characteristics of HBT, and the Q factor of inductor used in VCO design are showed. In Fig. 1, it is known that forward beta  $\beta_f$  is 150 and an early voltage is 110 V. Fig. 2 shows that a cutoff frequency  $\beta_f$  is 50 GHz at Ic = 1.5 mA. In Fig. 3, it is shown that the Q-factor of 8.2 nH inductor is 6.6 at 1.6 GHz<sup>[3]</sup>.

## III. VCO Design

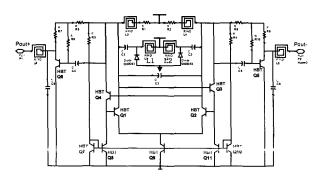

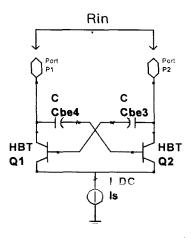

Fig. 4 shows the VCO circuit diagram. The VCO core is a differential cross-coupled type that generates

Fig. 2. SiGe HBT AC characteristics.

Fig. 3. Inductor characteristics.

a negative resistance. The VCO core is divided into three parts. The description of this VCO circuit will be made into three parts, in turn. The first of them is the active part which gives rise to a negative resistance, required to start oscillation in VCO circuit. The negative-resistance part is composed of HBT Q1, Q2, Q3 and Q4. The output of Q1 does positively feedback into Q2 and that of Q2 into Q1 through the base-emitter capacitances Cbe3, Cbe4 of Q3 and Q4, respectively. For that reason, a wide range of negative resistance is caused and if some oscillation conditions are achieved with resonators coupled, the circuit starts to oscillate. Here, Q3 and Q4 have a part to amplify an oscillation signal as well as to cause a positive feedback [4],[5].

The cross-coupled type is shown in Fig. 5. The input resistance  $R_{in}$  of the cross-coupled pair is as follows<sup>[6]</sup>.

$$R_{in} = -2/g_m \tag{1}$$

Here,  $g_m$  is transconductance.

The second is the resonance part of the VCO which consists of varactor diodes, inductors and capacitors,

Fig. 4. Differential VCO Full Schematic.

Fig. 5. Cross-Coupled Topology generating negative resistance.

and does primarily determine the phase noise characteristics of the designed VCO. In the resonator of this VCO, L1 and L2 were used having 8.2 nH inductance, and a pair of varactor diodes were symmetrically placed The last is a buffer that amplifies an oscillation power of the VCO core, which consists of HBT(Q5 & Q6), inductor and capacitor. The amplifier operates in common emitter configuration, and a shunt capacitor and a series inductor are used for transferring maximum power to load.

## IV. Simulation and Measurement

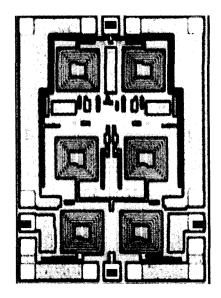

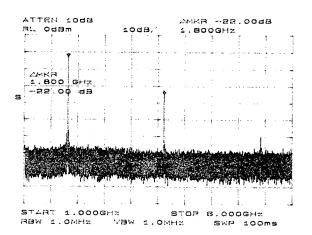

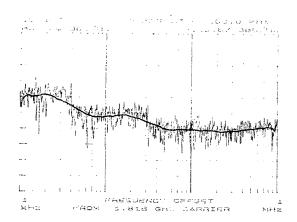

Fig. 6 shows the chip photograph of the fabricated VCO. The chip size of the VCO has  $1246 \times 1649~\mu$  m<sup>2</sup>. The oscillation frequency of the VCO was measured using Agilent 85652 spectrum analyzer as can be shown in Fig. 7. Fig. 7 shows second harmonic suppress on of -22 dBc and third harmonic suppression more han it at 1.8 GHz in the fabricated VCO. Also, the VCO obtained a phase noise of -110 dBc/Hz at 100 kHz offset from carrier frequency as represented in Fig. 8. In Table 1, the simulation and measurement results are compared.

Our target was to design PCS VCO using cadence tool, but the frequency range was shifted down by about 170 MHz. It is supposed that the frequency deviation is due to various parasitic elements, such as

Table 1. Summary of simulated and measured results.

| Parameter                                  | Simu.     | Meas.              |

|--------------------------------------------|-----------|--------------------|

| Supp y voltage [V]                         | 3         | 3                  |

| Current [mA]                               | 16        | 16                 |

| Tunir.g range [MHz]                        | 1837~2084 | 1795~1910          |

| Phase Noise @ 100 kHz                      | _         | - 110[dBc/Hz]      |

| 2 <sup>nd</sup> harmonic suppression [dBc] | - 20      | - 22               |

| Output power                               | -4~-6     | <b>-9.3∼ -11.7</b> |

Fig. 6. Die photograph of the VCO.

Fig. 7. Oscillation Frequency Spectrum.

capacitances, inductances, resistances on layout.

In Table 2, the performance results of this VCO and others are summarized and compared. This VCO is better than any other using silicon process in phase noise. The phase noise of VCO can be represented by the following formula<sup>[7]</sup>:

Table 2. Comparison of this VCO and others.

| Reference<br>number | Fabrication Process | f <sub>t</sub><br>[GHz] | f <sub>o</sub><br>[GHz] | V <sub>cc</sub><br>[V] | Power [mW] | P <sub>out</sub> [dBm] | Bandwidth [MHz] | Phase Noise<br>[dBc/Hz] |

|---------------------|---------------------|-------------------------|-------------------------|------------------------|------------|------------------------|-----------------|-------------------------|

| [7]                 | 0.8 μ m BiCMOS      | 11                      | 1.48                    | 3.6                    | 40         | - 9.4                  | 150             | - 105 @100 kHz          |

| [8]                 | BiCMOS              | 10                      | 1.75                    | 5                      | 70         | - 25                   | 200             | -88 @100 kHz            |

| [9]                 | 0.5 μ m Bipolar     | 25                      | 1.9                     | 3.3                    | 41         | - 5                    | 200             | -103 @100 kHz           |

| this VCO            | 0.5 μm SiGe BiCMOS  | 50                      | 1.82                    | 3                      | 48         | - 10.4                 | 115             | –110 @100 kHz           |

Fig. 8. Phase Noise.

$$L(f_m) = 10\log\left\{\left(\frac{f_o}{2Qf_m}\right)^2 \left[\frac{FkT}{2P_{out}}\left(1 + \frac{f_c}{f_m}\right)\right] + \frac{1}{2}\left(\frac{K_{vco}V_m}{2f_m}\right)^2\right\}$$

(2)

where  $L(f_m)$  is the phase noise in dBc/Hz,  $f_o$  is the output signal frequency of VCO in Hz, Q is the quality factor of VCO,  $f_m$  is the offset frequency in Hz, F is the noise figure of transistor, k is Boltzmann' constant in J/° K, T is the temperature in° K,  $P_{out}$  is the output signal power of VCO in W,  $f_c$  is the flicker noise corner frequency in Hz,  $K_{VCO}$  is the gain of VCO in Hz/V and  $V_m$  total amplitude of all low frequency noise sources in V/ $\sqrt{}$ Hz.

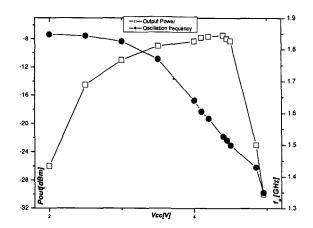

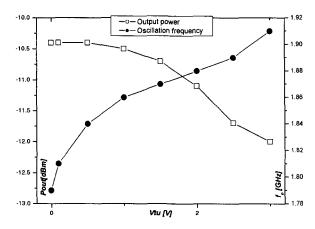

Thus, the phase noise of VCO using SiGe device is supposed to be better because the  $f_c$  and NF of SiGe process are lower than those of silicon process<sup>[1]</sup>. Fig. 9 shows the frequency pushing of the VCO. The graph indicates that oscillation stops below 2 V and above 5 V supply voltage. Also, we can see that the VCO could be used in PCS band at 4 V supply voltage. In Fig. 10, we obtained a tuning range of 1795 MHz $\sim$ 1910 MHz as biased to two varactor diodes from 0 V to 3 V. The output powers of the VCO are -9.3 dBm at 1795 MHz and -11.7 dBm at 1910 MHz. Those measured power levels are lower than the simulated ones by 4 dB. It was found out that about 1 dB loss was due to coaxial cable and connector.

## V. Conclusion

A 1.8 GHz fully differential monolithic HBT VCO has been designed and fabricated using a commercial  $0.5 \,\mu$  m SiGe BiCMOS process technology. The manufactured chip size of VCO is  $1246 \times 1649 \,\mu$  m<sup>2</sup>. The VCO achieved a low phase noise of -110 dBc/Hz at 100 kHz offset carrier and a third harmonic suppression of more than 22 dBc. The tuning range of the VCO

Fig. 9. Frequency Pushing.

Fig. 10. Tuning Range.

was 1795 MHz $\sim$ 1910 MHz as the output power levels were varied from -9.3 dBm to -11.7 dBm including about 1 dB of cable and connector losses. The VCO consumed 16 mA at 3 V supply voltage. The fabricated SiGe VCO showed good phase noise performance.

This work was supported by the Ministry of Information and Communication, Republic of Korea.

# References

- [1] G. Dawe, M. Gilbert, et al., "SiGe Technology: Application to Wireless Digital Communications", *Applied Microwave & Wireless*, pp. 14-24, Summer 1994.

- [2] E. de Foucauld, J. M. Paillot, et al., "Fully Monolithic SiGe Voltage-Controlled-Oscillators for Wire-

- less Phone Application", Topical Meeting on IEEE Silicon Monolithic Integrated Circuits in RF Systems, Digest of papers, pp. 29-32, 2000.

- [3] IBM SiGe HP(BiCMOS 5HP) Model Reference Guide.

- [4] Guillermo Gonzalez, Microwave Transistor Amplifiers Analysis and Design, New Jersey, Prentice-Hall, pp. 384, 1996.

- [5] P. G. M. Baltus, A. G. Wagemns, et al., "A 3.5 mW, 2.5-GHz Diversity Receiver and a 1.2-mW, 3.5-GHz VCO in Silicon on Anything", *IEEE Journal of Solid-State Circuits*, vol. 33, no. 12, pp. 274-279, Dec. 1998.

- [6] Behzad Razavi, RF Microelectronics, New Jersey,

- Prentice-Hall, pp. 228, 1998.

- [7] M. C. Leonard Dauphinee, et al., "A Balanced 1.5 GHz Voltage Controlled Oscillator with an integrated LC Resonator", IEEE ISSCC Digest of Technical Papers, pp. 453-455, Feb. 1997.

- [8] N. M. Nguyen, et al., "A 1.8 GHz Monolithic LC Voltage-Controlled Oscillator", *IEEE Journal of Solid-State Circuits*, vol. 27, no. 3, pp. 444-450, Mar. 1992.

- [9] W. M. John, Jose A. M. Rogers, et al., "A completely Integrated 1.9-GHz Receiver Front-End With Monolithic Image-Reject Filter and VCO", *IEEE Trans. MTT*, vol. 50, no. 1, pp. 210-215, Jan. 2002.

#### Ja-Yol Lee

received the B.E. degree from Konkuk university, Seoul, Korea, in 1998 and the M.E. degree from Chungnam National Univerity, Daejeon, in 2000, all in electronics engineering. Since 2001, he has been with ETRI, where he has been working as RF & Analog Circuit Designer. His research interests are RFIC and

OEIC design, semiconductor device modeling, and SPICE parameter extraction and optimization. He is a member of KICS and KEES.

## Jin-Young Kang

received the M.E. and Ph. D. degrees in Physics from Korea Advanced Institute of Science and Technology, in 1979 and 1991, respectively. He joined the Electronics and Telecommunications Research Institute(ETRI) at Daejeon in 1979. He has been working on the development of SiGe Devices and Processes. At present,

he is a director of SiGe Device Team at ETRI-Basic Research Laboratory.

## Sang-Heung Lee

was born in Daejeon, Korea, in 1966. He received the B.E., M.S., and Ph. D. degrees in Department of Electronics Engineering from Chungnam National University, Korea, in 1988, 1992, and 1998, respectively. From 1998 to 1999, he held a position as a post-doctorial researcher at Electronics and Tele-

communications Research Institute(ETRI) in Daejeon, Korea. Since 1999, he has been working as a circuit design engineer at Electronics and Telecommunications Research Institute (ETRI). His current interests are RFIC and OEIC design, semiconductor device modeling, and SPICE parameter extraction and optimization.

#### Kyu-Hwan Shim

Feb.1884: B.S. degree(Materials Science), Korea University; Feb. 1986: M.S. degree (Semiconductor Materials), Korea University; Oct. 1997: Ph. D. degree (Electronic Materials), University of Illinois at Urbana-Champaign; Jan. 1986~ Present: ETRI, Principal Member of Research Staff, <Major Research Field: SiGe

Devices and Processes, Nanotechnology>

# Kyoung-Ik Cho

received the B.S. degree in Materials Science from Ulsan Institute of Technology in 1979, and the M.S. and Ph. D. degrees in Material Science and Engineering from Korea Advanced Institute of Science and Technology, in 1981 and 1991, respectively. He joined the Electronics and Telecommunications Research

Institute(ETRI) at Daejeon in 1981. He has been working on the development of advanced flat panel display devices, field emission display and digital paper, and next-generation memory devices, such as, ferroelectric memory, optical data storage devices, and corresponding driving power ICs. At present, he is a director of Wireless Communication Devices Department at ETRI-Basic Research Laboratory.

## Seung-Hyeub Oh

received the B.E., the M.S., and the Ph. D. degrees in Yonsei University, Seoul, Korea, in 1971, 1973 and 1982, respectively, all in electrical engineering. He worked for Tohoku University, Japan, from 1980 to 1981, as a guest researcher and Pennsylvania State Uninversity, USA, from 1985 to 1986, as a guest

researcher. Since 1984 he has been with Chungnam National University, Daejeon, Korea, where he is a professor in the Department of Electronics Engineering. His research interests include antenna engineering and digital communication RF sub-system design. He is a member of KICS and KEES and IEEE.